práctica 8: contador síncrono con quartus ii - IIT

Anuncio

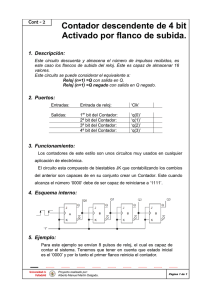

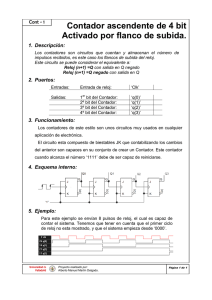

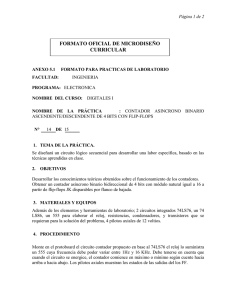

PRÁCTICA 8: CONTADOR SÍNCRONO CON QUARTUS II OBJETIVOS Diseñar un circuito secuencial síncrono e implementarlo en una FPGA. Al finalizar la práctica, el alumno debe ser capaz de: − Diseñar un circuito complejo a base de componentes más simples, − Diseñar circuitos secuenciales sencillos, − Reutilizar componentes de otros diseños usando Quartus II. MATERIAL − Ordenador personal con Quartus II, − Tarjeta de desarrollo de lógica programable DE1 de Altera. DURACIÓN 1 sesión. TRABAJO PREVIO Leer el enunciado de la práctica y diseñar de forma esquemática con flip-flop’s tipo D, un contador síncrono de cuatro bits, que cuente de 0h a Fh. INTRODUCCIÓN En esta práctica se va a diseñar un contador síncrono de cuatro bits que cuente de 0h a Fh para implementarlo en una FPGA y visualizar el resultado de la cuenta en uno de los display de siete segmentos que hay en la tarjeta del laboratorio. El esquema del circuito que el alumno debe montar en la práctica de hoy se encuentra en el Anexo A, al final del enunciado de la práctica. De los tres bloques que se encuentran en dicho esquema, el primero (DivisorReloj.vhd) es un divisor de reloj disponible en la página web del laboratorio. El código está en el anexo B de esta práctica. Este bloque es necesario porque el reloj de la tarjeta del laboratorio es de 50 MHz, lo que impide visualizar correctamente la evolución de la cuenta en el display de la tarjeta. Dicho bloque reduce la frecuencia del reloj de la tarjeta a una frecuencia de unos 2 Hz. 2 Práctica 8 El archivo anterior hay que copiarlo a la carpeta de trabajo de la sesión, abrirlo con Quartus II y generar su símbolo de la misma forma que se genera el símbolo de una captura de esquemas. El segundo bloque (Contador4Bits.gdf) es el contador síncrono de cuatro bits que debe realizar el alumno. Se conecta con el resto de bloques como se indica en el esquema del Anexo A. El tercer y último bloque es el decodificador de binario a siete segmentos (Bina7Seg.bdf) que el alumno ha realizado en las prácticas 3 y 4. Para poder utilizarlo, el alumno debe copiar el archivo Bina7Seg.bdf a la carpeta de trabajo de esta sesión y generar el símbolo. El circuito se diseñará mediante el programa Quartus II de Altera, se guardará con el nombre Contador.bdf y se implementará en la tarjeta de laboratorio con la FPGA. Como siempre, antes de comenzar a trabajar, se debe crear el directorio de trabajo para la práctica de esta sesión. CARACTERÍSTICAS DEL CIRCUITO El circuito Contador.bdf tiene dos entradas: − Una señal Reset, para inicializar el sistema, y − Una señal Reloj del sistema. Y siete salidas (a, b, c, d, e, f y g) que se conectarán a un display de siete segmentos de la tarjeta, para indicar el valor de la cuenta. El bloque Contador4bits.gdf tiene dos entradas: − Una señal Reset para inicializar el contador, y − Una señal Reloj para sincronizar la cuenta. Y cuatro salidas (QD, QC, QB y QA) que representan el número de la cuenta en binario. En el diseño sólo se pueden utilizar flip-flop’s tipo D sin enable (el componente se denomina dff) y puertas NAND (nand2, nand3, etc.). DESARROLLO PRÁCTICO DISEÑO Realice los siguientes pasos de diseño: − el diagrama de transición de estados, − la tabla de transición y la tabla de excitación de los flip-flop’s, 3 Práctica 8 − los diagramas de Karnaugh empleados para la obtención de las ecuaciones lógicas de las entradas a los flip-flop’s y de la salida, − los circuitos lógicos utilizados para implantar dichas ecuaciones lógicas. Recuerde que estos circuitos habrán de diseñarse de modo que sólo se utilicen puertas NAND. ESQUEMA Dibuje el esquema del Anexo A en una ventana de diseño de Quartus II, guárdelo con el nombre Contador.bdf y declárelo como proyecto. Asigne las patillas de la FPGA indicadas en la Tabla 1 a las entradas y salidas del circuito. Consulte para ello el manual de usuario de la tarjeta de lógica programable (Altera DE1 Board).1 Señal Tipo Patilla FPGA Componente Reset Entrada KEY[0] Reloj Entrada CLOCK_50 a Salida HEX0[0] b Salida HEX0[1] c Salida HEX0[2] d Salida HEX0[3] e Salida HEX0[4] f Salida HEX0[5] g Salida HEX0[6] Tabla 1. Asignación de patillas de la FPGA a las señales del circuito. Compile el circuito para el dispositivo EP2C20F484C7 de la familia Cyclone II. Realice la simulación del circuito comprobando las operaciones. Muestre al profesor los resultados de la simulación. CONFIGURACIÓN Configure la FPGA y compruebe el correcto funcionamiento con la tarjeta del laboratorio realizando diferentes operaciones. Enseñe al profesor dicho funcionamiento. ANEXO A 1 Disponible en la dirección http://www.iit.upcomillas.es/carlosrg/Docencia/LED/DE1_UserManual_v1018.pdf 4 Práctica 8 ANEXO B --********************************************************************* --** ** --** Divisor de reloj: divide la frecuencia de reloj por 2^25. ** --** ** --** La salida es una señal de reloj de unos 2 Hz. ** --** ** --** Version: 1.0 ** --** ** --** Universidad Pontificia Comillas de Madrid - I.C.A.I. ** --** ** --********************************************************************* LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.std_logic_arith.all; ENTITY DivisorReloj IS PORT( Reloj_in : IN STD_LOGIC; Reloj_out: OUT STD_LOGIC ); END DivisorReloj; ARCHITECTURE arquit OF DivisorReloj IS SIGNAL Contador : INTEGER RANGE 0 TO 25000000; SIGNAL VectorContador : STD_LOGIC_VECTOR (24 DOWNTO 0); BEGIN PROCESS (Reloj_in, Contador, VectorContador) IS BEGIN VectorContador <= CONV_STD_LOGIC_VECTOR (Contador, 25); IF Reloj_in = '1' AND Reloj_in'EVENT THEN Contador <= Contador + 1; Reloj_out <= VectorContador(24); END IF; END PROCESS; END arquit;