TEMA 6. Circuitos Aritméticos.

Anuncio

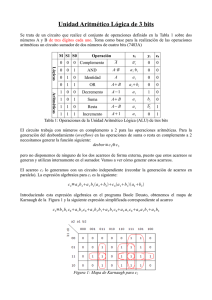

Fundamentos de los Computadores. Circuitos Aritméticos TEMA 6. Circuitos Aritméticos. INDICE: • OPERACIONES EN EL SISTEMA BINARIO • CIRCUITOS SUMADORES • CIRCUITOS RESTADORES • UNIDADES LÓGICO ARITMÉTICAS T6-1 Fundamentos de los Computadores. Circuitos Aritméticos T6-2 OPERACIONES EN EL SISTEMA BINARIO (I) LAS PRINCIPALES OPERACIONES ARITMÉTICAS QUE REALIZA UN COMPUTADOR SON: SUMA, RESTA, PRODUCTO Y DIVISIÓN. EN ESTE CURSO SOLO TRATAREMOS LA SUMA Y LA RESTA BINARIA. SUMA BINARIA ESTÁ BASADA EN LA SUMA DECIMAL QUE CONOCEMOS TAN BIEN: 1 2 3 01 10 11 2 2 4 10 10 100 COMO VEMOS LA SUMA DE NÚMEROS BINARIOS DE DOS BITS NOS PUEDE DAR UN NÚMERO BINARIO DE TRES BITS. A ESTE BIT MÁS SIGNIFICATIVO SE LE CONOCE COMO EL ACARREO (PARECIDO AL “ME LLEVO UNA” DE LA SUMA DECIMAL). A B SUMA ACARREO 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 EJEMPLO DE SUMA BINARIA CON MÁS BITS ACARREO SUMANDO SUMANDO 1111 10111 +1 1 0 1 1 110010 1 23 + 27 50 Fundamentos de los Computadores. Circuitos Aritméticos T6-3 OPERACIONES EN EL SISTEMA BINARIO (I) RESTA BINARIA CONSISTE EN SUMAR UN NÚMERO CON EL NEGATIVO DE OTRO. EL NEGATIVO DE UN NÚMERO BINARIO NORMALMENTE AÑADIENDO UN BIT DE SIGNO. SE OBTIENE LA FORMA MÁS USUAL ES TRABAJAR CON NÚMEROS EN C-1 (COMPLEMENTO A UNO) O, EN C-2 (COMPLEMENTO A DOS). EN AMBOS CASOS EL BIT MÁS SIGNIFICATIVO SE CONVIERTE EN BIT DE SIGNO. Decimal +8 +7 +6 +5 +4 +3 +2 +1 +0 −0 −1 −2 −3 −4 −5 −6 −7 −8 Binario 1000 0111 0110 0101 0100 0011 0010 0001 0000 C-1 C-2 0111 0110 0101 0100 0011 0010 0001 0000 1111 1110 1101 1100 1011 1010 1001 1000 0111 0110 0101 0100 0011 0010 0001 0000 1111 1110 1101 1100 1011 1010 1001 1000 C-1 SE OBTIENE INVIRTIENDO TODOS LOS BITS UNO A UNO. C-2 SE OBTIENE SUMANDO 1 AL C-1 DEL NÚMERO A NEGAR, O BIEN, SE PUEDE OBTENER REESCRIBIENDO DE DERECHA A IZQUIERDA, COPIANDO LOS BITS HASTA EL PRIMER 1, Y A PARTIR DE AHÍ EL RESTO ES INVERTIDO. Fundamentos de los Computadores. Circuitos Aritméticos T6-4 CIRCUITOS SUMADORES UN SUMADOR ES UN CIRCUITO QUE ARITMÉTICA DE DOS PALABRAS BINARIAS. REALIZA LA SUMA LA SUMA DE NÚMEROS BINARIOS DE n BITS NOS DA UN NÚMERO BINARIO DE n+1 BITS. UN SUMADOR DE DOS BITS DEBERÁ TENER 2 ENTRADAS Y TRES SALIDAS. A ESTE BIT MÁS SIGNIFICATIVO EN LA SALIDA SE LE CONOCE COMO EL ACARREO. UN DISPOSITIVO QUE REALICE ESTA OPERACIÓN SE DENOMINA MEDIO SUMADOR: AB 00 01 10 11 CARRY 0 0 0 1 A+B 0 1 1 0 A B Σ A+B Cout A LA SALIDA A+B, SE LE CONOCE TAMBIÉN COMO MEDIA SUMA (HA). COUT, INDICA EL ACARREO DE SALIDA (CARRY OUT). ESTA SALIDA SE PUEDE USAR PARA CONECTAR EN CASCADA DISTINTOS SUMADORES, DE MANERA QUE PODAMOS SUMAR PALABRAS DE MÁS DE UN BIT. PARA ELLO NECESITAMOS QUE EL CIRCUITO DISPONGA DE UNA ENTRADA EXTRA POR DONDE PODAMOS INFORMARLE DE LA SUMA DE LOS BITS ANTERIORES. UN ACARREO DE ENTRADA. Fundamentos de los Computadores. Circuitos Aritméticos T6-5 SUMADOR COMPLETO ES UN CIRCUITO QUE TIENE, ADEMÁS DE LAS ENTRADAS CORRESPONDIENTES A LOS BITS QUE SE PRETENDEN SUMAR, UNA ENTRADA DE ACARREO. (SÍMBOLO PARA LA SUMA DE PALABRAS DE n BITS) A B n n Σ n A+B Cout Cin TABLA DE FUNCIONAMIENTO PARA PALABRAS DE 1 BIT: AB 00 00 01 01 10 10 11 11 Cin 0 1 0 1 0 1 0 1 Cout 0 0 0 1 0 1 1 1 A+B 0 1 1 0 1 0 0 1 ESTE SUMADOR COMPLETO CONSTITUYE EL BLOQUE BÁSICO PARA SUMAR PALABRAS DE MAYOR NÚMERO DE BITS. SÍMBOLO STANDARD DEL SUMADOR COMPLETO DE 4 BITS (74283) Fundamentos de los Computadores. Circuitos Aritméticos T6-6 SUMADOR COMPLETO DE 16 BITS ESTE CIRCUITO SUMA 16 BITS CON PROPAGACIÓN DE ACARREO SERIE, USANDO SUMADORES COMPLETOS DE 4 BITS. PROPAGACIÓN EN SERIE DEL ACARREO: SI EL TIEMPO QUE TARDA UN SUMADOR DE 4 BITS EN OBTENER, A PARTIR DE LOS DATOS DE ENTRADA, LOS VALORES DE LA SALIDA LO DENOMINAMOS τ, EL TIEMPO QUE SE TARDA EN OBTENER LA PALABRA S[0-16] COMO LA SUMA BINARIA DE A[0-15] Y B[0-15], CON ESTE CIRCUITO ES 4 τ. PROPAGACIÓN EN PARALELO DEL ACARREO: EXISTEN CIRCUITOS QUE PERMITEN MANEJAR LOS ACARREOS AL MISMO TIEMPO Y REDUCIR EL TIEMPO EN OBTENER LA SUMA A 2 τ. SE USAN PRINCIPALMENTE CON ALU’S. Fundamentos de los Computadores. Circuitos Aritméticos T6-7 CONVERSIÓN DE CÓDIGOS CON SUMADORES EJEMPLO1: PARA OBTENER UNA PALABRA DEL CÓDIGO BCD-EXCESO-3, BASTA SUMAR LA PALABRA 0011 (3) AL NÚMERO BCD-NATURAL. EJEMPLO 2: REALIZACIÓN DE UN CONVERTIDOR DE CÓDIGO BCD-NATURAL A BCD-AIKEN, USANDO UN CIRCUITO SUMADOR DE 4 BITS Y PUERTAS LÓGICAS: BCD-natural n 0 1 2 3 4 5 6 7 8 9 X A3 0 0 0 0 0 0 0 0 1 1 1 A2 0 0 0 0 1 1 1 1 0 0 0 A1 0 0 1 1 0 0 1 1 0 0 1 Palabra para convertir A0 0 1 0 1 0 1 0 1 0 1 0 B3 0 0 0 0 0 0 0 0 0 0 X B2 0 0 0 0 0 1 1 1 1 1 X B1 0 0 0 0 0 1 1 1 1 1 X B0 0 0 0 0 0 0 0 0 0 0 X BCD-Aiken S3 0 0 0 0 0 1 1 1 1 1 X S2 0 0 0 0 1 0 1 1 1 1 X S1 0 0 1 1 0 1 0 0 1 1 X S0 0 1 0 1 0 1 0 1 0 1 X DE LA TABLA DE FUNCIONAMIENTO SE OBTIENEN Bi A PARTIR DE LAS Ai: B3 = B0 = 0 B1 = B2 = A3 + A2A1 + A2A0 EL CIRCUITO QUEDA: A0 A1 A2 A3 B1 B2 B0 B3 S0 S1 S2 S3 Fundamentos de los Computadores. Circuitos Aritméticos T6-8 CIRCUITOS RESTADORES SE REALIZAN MEDIANTE SUMADORES, YA QUE LA RESTA DE DOS NÚMEROS ES LA SUMA DE UNO CON EL NEGATIVO DEL OTRO. ESTE CIRCUITO REALIZA LA RESTA DE A[0-3] Y B[0-3] EN C-1: A0 A1 A2 AS B0 B1 B2 BS S0 S1 S2 SS ESTE OTRO ES UN SUMADOR/RESTADOR DE A[0-3] Y B[0-3], EN C-2. LA ENTRADA SL ES 0 PARA OBTENER A+B Y 1 PARA OBTENER A-B. A0 A1 A2 AS B0 B1 B2 BS SL S0 S1 S2 SS Fundamentos de los Computadores. Circuitos Aritméticos T6-9 UNIDADES LÓGICO ARITMÉTICAS (ALU) SE TRATAN DE CIRCUITOS MSI QUE PUEDEN REALIZAR DIFERENTES OPERACIONES ARITMÉTICAS Y LÓGICAS CON DOS PALABRAS DE n BITS. ESTA ALU DE 4 BITS PUEDE REALIZAR HASTA 32 FUNCIONES DIFERENTES (16 LÓGICAS Y 16 ARITMÉTICAS): Fundamentos de los Computadores. Circuitos Aritméticos T6-10 ASOCIACIÓN DE ALU’s (ACARREO EN SERIE) LA ASOCIACIÓN DE ALU’S, PARA OPERAR CON MÁS BITS, SE PUEDE HACER EN SERIE (ACARREO SERIE) O EN PARALELO (ACARREO PARALELO). PARA EL PRIMERO, BASTA USAR LAS ENTRADAS DE ACARREO ANTERIOR (C1) Y LAS SALIDAS DE ACARREO SERIE (CO), PARA REALIZAR UNA CONEXIÓN SIMILAR A LA DE LOS SUMADORES: S[0-3] y M0 A[0-7] B[0-7] Ci B00 A A1 B1 A2 B2 A3 B3 B A44 A5 B5 A6 B6 A7 B7 F[0-7] Co PARA QUE EL PROCESAMIENTO DE LOS DATOS SEA MÁS RÁPIDO, SE USA UN CIRCUITO DE PROPAGACIÓN Y GENERACIÓN DE ACARREO. PARA ELLO SE USAN LAS SALIDAS G Y P DE LAS ALU’S: G SE ACTIVA SI LA ALU GENERA UN ACARREO, O SEA, SI SE PRODUCE UNA ACARREO SALIENTE (CO=1), INDEPENDIENTEMENTE DE SI HAY O NO UN ACARREO ENTRANTE (C1=X). P SE ACTIVA SI LA ALU PROPAGA UN ACARREO, O SEA, SE PRODUCIRÁ UN ACARREO SALIENTE SI HAY UN ACARREO ENTRANTE. Fundamentos de los Computadores. Circuitos Aritméticos T6-11 ASOCIACIÓN DE ALU’s (ACARREO EN PARALELO) EL SIGUIENTE DIAGRAMA CORRESPONDE A UN CIRCUITO CAPAZ DE PROCESAR 16 BITS. SE TRATA DE UNA ALU DE 16 BITS, CON PROPAGACIÓN DE ACARREO EN PARALELO. S[0-3] y M0 A[0-15] B[0-15] Ci A otro CPG F[0-15]