Práctico Rendimiento

Anuncio

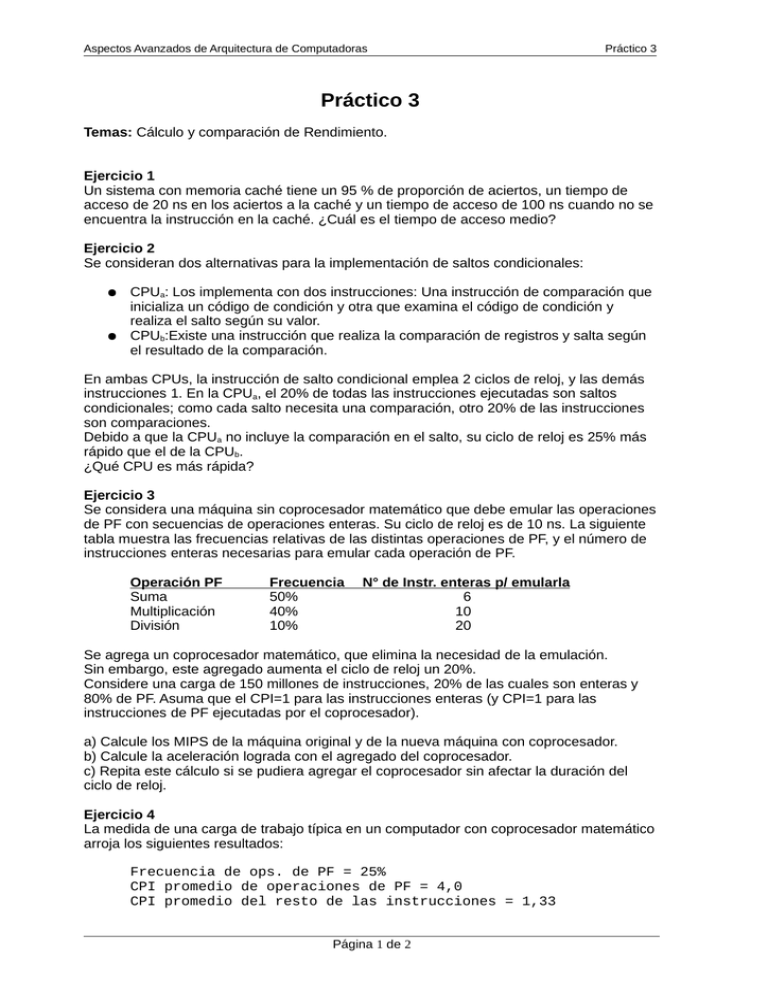

Aspectos Avanzados de Arquitectura de Computadoras Práctico 3 Práctico 3 Temas: Cálculo y comparación de Rendimiento. Ejercicio 1 Un sistema con memoria caché tiene un 95 % de proporción de aciertos, un tiempo de acceso de 20 ns en los aciertos a la caché y un tiempo de acceso de 100 ns cuando no se encuentra la instrucción en la caché. ¿Cuál es el tiempo de acceso medio? Ejercicio 2 Se consideran dos alternativas para la implementación de saltos condicionales: CPUa: Los implementa con dos instrucciones: Una instrucción de comparación que inicializa un código de condición y otra que examina el código de condición y realiza el salto según su valor. ● CPUb:Existe una instrucción que realiza la comparación de registros y salta según el resultado de la comparación. ● En ambas CPUs, la instrucción de salto condicional emplea 2 ciclos de reloj, y las demás instrucciones 1. En la CPUa, el 20% de todas las instrucciones ejecutadas son saltos condicionales; como cada salto necesita una comparación, otro 20% de las instrucciones son comparaciones. Debido a que la CPUa no incluye la comparación en el salto, su ciclo de reloj es 25% más rápido que el de la CPUb. ¿Qué CPU es más rápida? Ejercicio 3 Se considera una máquina sin coprocesador matemático que debe emular las operaciones de PF con secuencias de operaciones enteras. Su ciclo de reloj es de 10 ns. La siguiente tabla muestra las frecuencias relativas de las distintas operaciones de PF, y el número de instrucciones enteras necesarias para emular cada operación de PF. Operación PF Suma Multiplicación División Frecuencia 50% 40% 10% N° de Instr. enteras p/ emularla 6 10 20 Se agrega un coprocesador matemático, que elimina la necesidad de la emulación. Sin embargo, este agregado aumenta el ciclo de reloj un 20%. Considere una carga de 150 millones de instrucciones, 20% de las cuales son enteras y 80% de PF. Asuma que el CPI=1 para las instrucciones enteras (y CPI=1 para las instrucciones de PF ejecutadas por el coprocesador). a) Calcule los MIPS de la máquina original y de la nueva máquina con coprocesador. b) Calcule la aceleración lograda con el agregado del coprocesador. c) Repita este cálculo si se pudiera agregar el coprocesador sin afectar la duración del ciclo de reloj. Ejercicio 4 La medida de una carga de trabajo típica en un computador con coprocesador matemático arroja los siguientes resultados: Frecuencia de ops. de PF = 25% CPI promedio de operaciones de PF = 4,0 CPI promedio del resto de las instrucciones = 1,33 Página 1 de 2 Aspectos Avanzados de Arquitectura de Computadoras Práctico 3 Frecuencia de la FPSQR = 2% CPI de la FPSQR = 20 PF: Punto Flotante, FPSQR: Raíz cuadrada Se consideran dos alternativas de diseño para mejorar el rendimiento: Alternativa 1) Reducir la CPI de la FPSQR a 2. Alternativa 2) Reducir la CPI promedio para todas las operaciones de PF a 2. Se pide: a) ¿Qué alternativa recomendaría ? Justifique numéricamente b) La Ley de Amdhal establece que la mejora obtenida en el rendimiento al utilizar alguna mejora de diseño está limitada por la fracción de tiempo en que se pueda utilizar esa mejora de diseño. Define la aceleración como el cociente: Tiempo de ejecución de la tarea completa sin utilizar la mejora Tiempo de ejecución de la tarea completa utilizando la mejora cuando sea posible Calcule la aceleración para cada una de las alternativas. ¿Es coherente con su conclusión de la Parte a)? Ejercicio 5 a) ¿Cuál es el tiempo de ejecución de una instrucción en un pipeline de N etapas, c/etapa con una duración T? b) En el caso ideal, ¿cuál es la frecuencia de instrucciones ejecutadas por ciclo usando un pipeline? ¿Qué tipos de instrucciones impiden este desempeño ideal?. Describa una técnica utilizada en una arquitectura conocida, para contrarrestar esto. Justifique sus respuestas. c) Suponga un procesador de 5 etapas: extracción, decodificación, cálculo de direcciones, extracción de operandos y ejecución. Cada etapa emplea 50, 50, 60, 50 y 50 nanosegundos respectivamente. ¿Cuánto tiempo empleará en ejecutarse una instrucción si el procesador se organiza en pipeline? ¿Cuál es el factor de aumento de velocidad del pipeline? Obs: tenga en cuenta que en un pipeline c/etapa está a continuación de la siguiente, y no hay posibilidad de que unas etapas esperen por otras para ser completadas. Ejercicio 6 Considere una CPU y la siguiente carga de trabajo: Tipo de instrucción Cantidad de instrucciones CPI Operaciones de ALU 20 millones 1 Accesos a memoria 10 millones 3 Operaciones de E/S 5 millones 8 Se propone agregar un cache L1 que reduce el CPI de las operaciones de memoria a 1.5. a) Calcule la aceleración lograda con la mejora, utilizando la ley de Amdahl. b) Calcule la aceleración lograda comparando los tiempos de ejecución de las cargas Página 2 de 2