7.6. Memorias RAM 7.6.1. Introducción a las memorias

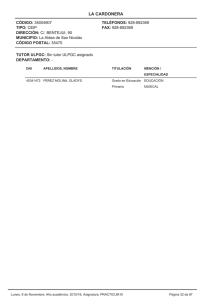

Anuncio

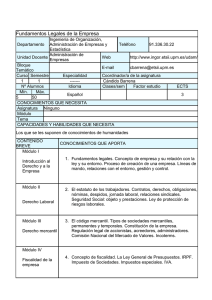

Electrónica Industrial, 4º ETSII 7.6. Memorias RAM 7.6.1.Introducción a las memorias 7.6.2. Memorias ROM [ Wakerly 10.1 pág. 833] 7.6.2.1. Estructura interna [ Wakerly 10.1.2 pág. 837] 7.6.2.2. Tipos comerciales de ROM [ Wakerly 10.1.4 pág. 841] 7.6.2.3. Temporización y entradas de control [ Wakerly 10.1.5 pág. 845] 7.6.3. Tipos de memoria [ Wakerly 10.2 pág. 854] 7.6.4. RAM Estática 7.6.4.1.Entradas y salidas de la RAM estática [ Wakerly 10.3.1 pág. 854] 7.6.4.2.Estructura interna de la RAM estática [ Wakerly 10.3.2 pág. 856] 7.6.4.3.Temporización de la RAM estática [ Wakerly 10.3.3 pág. 858] 7.6.5. RAM Dinámica 7.6.5.1.Estructura interna de la RAM dinámica [ Wakerly 10.4.1 pág. 866] 7.6.5.2.Temporización de la RAM dinámica [ Wakerly 10.4.2 pág. 868] 7.6.5.3.DRAM síncronas [ Wakerly 10.4.3 pág. 871] ULPGC Electrónica Industrial - 4º ETSII 1 7.6.1. Introducción a las memorias • Organización básica de las memorias • Concepto de capacidad • Concepto de bit, byte y word (palabra) ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 2 1 Electrónica Industrial, 4º ETSII 7.6.1. Introducción a las memorias • Operación de lectura en memoria ULPGC Electrónica Industrial - 4º ETSII 3 7.6.1. Introducción a las memorias • Operación de escritura en memoria ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 4 2 Electrónica Industrial, 4º ETSII 7.6.2. Memorias ROM • Almacenamiento de programas – “Boot” en PCs y todo el programa en sistemas empotrados • La ROM es un circuito combinacional – Puede desarrollar cualquier función ULPGC Electrónica Industrial - 4º ETSII 5 7.6.2. Memorias ROM • Circuito lógico ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 6 3 Electrónica Industrial, 4º ETSII 7.6.2.1. Estructura interna 000 001 010 011 100 101 110 111 PDP-11 boot ROM (64 palabras, 1024 diodos) ULPGC Electrónica Industrial - 4º ETSII 8 7.6.2.1. Estructura interna • Decodificación en dos dimensiones 000XXXX 001XXXX 010XXXX 011XXXX 100XXXX 101XXXX 110XXXX 111XXXX ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 9 4 Electrónica Industrial, 4º ETSII 7.6.2.1. Estructura interna • Posible composición de una ROM de 32Kx8 ULPGC Electrónica Industrial - 4º ETSII 10 7.6.2.1. Estructura interna • Actualmente las ROM usan transistores MOS • 256K bytes, 1M byte, o mayor ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 11 5 Electrónica Industrial, 4º ETSII 7.6.2.2. Tipos comerciales de ROM EPROMS y EEPROMs ULPGC • Operación de lectura en una memoria flash Electrónica Industrial - 4º ETSII 12 7.6.2.2. Tipos comerciales de ROM EPROMS y EEPROMs • ROMs programables y borrables • Usan transistores MOS de puerta flotante ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 13 6 Electrónica Industrial, 4º ETSII 7.6.2.2. Tipos comerciales de ROM EPROMS y EEPROMs ULPGC • Programación y desprogramación de la memoria flash Electrónica Industrial - 4º ETSII 14 7.6.2.2. Tipos comerciales de ROM ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 15 7 Electrónica Industrial, 4º ETSII 7.6.2.2. Tipos comerciales de ROM Programación de las EPROMS • Programación: se aplica una mayor tensión para almacenar un uno en la puerta flotante – Por ejemplo, VPP = 12 V – En los chips más recientes hay circuitería específica para hacer esto • Borrado: – Byte-byte – Todo el chip (“flash”) – Un bloque (típicamente 32K - 66K bytes) a un tiempo • La programación y el borrado son más lentas que la lectura (milisegundos frente a decenas de nanosegundos) ULPGC Electrónica Industrial - 4º ETSII 16 7.6.2.2. Tipos comerciales de ROM ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 17 8 Electrónica Industrial, 4º ETSII 7.6.2.2. Temporización y entradas de control • Señales de control y de entrada/salida de las ROM ULPGC Electrónica Industrial - 4º ETSII 18 7.6.2.2. Temporización y entradas de control • Temporización – – – – – Tiempo de acceso de dirección, tAA Tiempo de acceso de selección de chip, tACS Tiempo de habilitación de salida, tOE Tiempo de deshabilitación de salida, tOZ Tiempo de retención de salida, tOH ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 19 9 Electrónica Industrial, 4º ETSII 7.6.3. Tipos de memoria • RAM = “Random Access Memory” • Volatilidad – La mayorías de las RAM pierden el contenido al quitar la tensión – NVRAM = RAM + batería – EEPROM: ROM eléctricamente reprogramables • SRAM (RAM Estática) – El comportamiento de la memoria es como el de los latches o flip-flops • DRAM (Memoria Dinámica) – El contenido se almacena durante unos pocos milisegundos – Necesitan “refrescarse” mediante lecturas y escrituras repetidas ULPGC Electrónica Industrial - 4º ETSII 20 7.6.4. RAM Estática (SRAM) Entradas y salidas ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 21 10 Electrónica Industrial, 4º ETSII 7.6.4. RAM Estática (SRAM) Comportamiento funcional • Los bits de memoria se comportan con latches no como flip-flops – Número de transistores por celda reducido. • Implicaciones para las operaciones de escritura: – La dirección debe estar estable antes de escribir el dato – El dato debe estar estable antes del fin de la escritura ULPGC Electrónica Industrial - 4º ETSII 22 7.6.4. RAM Estática (SRAM) Estructura interna ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 23 11 Electrónica Industrial, 4º ETSII 7.6.4. RAM Estática (SRAM) Estructura interna • Líneas de control de la SRAM – Chip select – Output enable – Write enable ULPGC Electrónica Industrial - 4º ETSII 24 7.6.4. RAM Estática (SRAM) Temporización: Lectura ULPGC ®«Roberto Sarmiento» • Similar a la de una memoria ROM Electrónica Industrial - 4º ETSII 25 12 Electrónica Industrial, 4º ETSII 7.6.4. RAM Estática (SRAM) • Temporización: Escritura ULPGC • La dirección debe estar estable antes y después de introducir el write-enable El Dato es almacenado en el flanco de bajada de (WE & CS). Electrónica Industrial - 4º ETSII 26 7.6.4. RAM Estática (SRAM) 32-pin DIPs RAM estática estándar 28-pin DIPs ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 27 13 Electrónica Industrial, 4º ETSII 7.6.4. RAM Estática (SRAM) RAM estática estándar Pines bidireccionales para entradas y salidas • Se usan los mismos pines para lectura y escritura – Muy común en chips de alta densidad – La memorias se conectan con microprocesadores con buses bidireccionales ULPGC Electrónica Industrial - 4º ETSII 28 7.6.5. RAM Dinámica Celda de memoria ULPGC ®«Roberto Sarmiento» • Las SRAMs normalmente usan 6 transistores por cada bit que almacenan. • Las DRAMs solamente usan un transistor por bit: • Se almacena un 1/0 cuando la capacidad esta cargada/descargada Electrónica Industrial - 4º ETSII 29 14 Electrónica Industrial, 4º ETSII 7.6.5. RAM Dinámica Operación de lectura • Se precarga la línea de bit (bit line) to VDD/2. • Se pone la línea de palabra (word line) a HIGH. • Se detecta cuando en la línea de bit fluye la corriente hacia dentro o hacia fuera de la célula • Nota: ¡la lectura destruye el contenido de la celda de memoria! • Se debe reescribir el contenido después de la lectura ULPGC Electrónica Industrial - 4º ETSII 30 7.6.5. RAM Dinámica Operación de escritura • Se pone la línea de palabra (word line) a HIGH. • Se pone la línea de bit (bit line) a LOW o HIGH según queramos escribir un 0 o un 1 • Se vuelve la línea de palabra a LOW • Nota: ¡la carga almacenada en el condensador cuando se almacena un 1 se pierde paulatinamente! ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 31 15 Electrónica Industrial, 4º ETSII 7.6.5. RAM Dinámica Pérdida de la carga • DRAM típica requieren que la carga del condensador se refresque entre los 4 y los 64 ms • En la condición de “suspensión” los portátiles requieren la corriente para refrescar la memoria DRAM ULPGC Electrónica Industrial - 4º ETSII 32 7.6.5. RAM Dinámica Estructura interna de una DRAM de 64Kx1 ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 33 16 Electrónica Industrial, 4º ETSII 7.6.5. RAM Dinámica • Temporización: Lectura ULPGC Row Address Strobe, Column Address Strobe – n address bits are provided in two steps using n/2 pins, referenced to the falling edges of RAS_L and CAS_L – Traditional method of DRAM operation for 20 years. – Now being supplanted by synchronous, clocked interfaces in SDRAM (synchronous DRAM). Electrónica Industrial - 4º ETSII 34 7.6.5. RAM Dinámica Temporización: Refresco ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 35 17 Electrónica Industrial, 4º ETSII 7.6.5. RAM Dinámica Temporización: Escritura ULPGC ®«Roberto Sarmiento» Electrónica Industrial - 4º ETSII 36 18