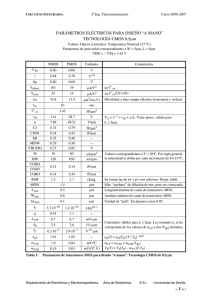

1- Dado el layout de la figura P-1, representar las secciones en

Anuncio

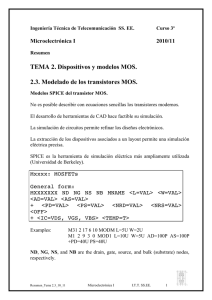

Microelectrónica I 1- I. T. de Telecomunicación, Esp. Sistemas Electrónicos Examen Febrero 2010 Dado el layout de la figura P-1, representar las secciones en profundidad por las lineas: a)A-B. b) C-D. (1 punto: a) 0,5 puntos; b) 0,5 puntos) C 2µm 1µm 4µm 8µm 2µm A B D Figura P-1 2- Dado el layout del transitor NMOS de la figura P-1 y considerando un proceso con: y suponiendo que Vg=5V, VDD=5V y VTh=0,6V, se pide: a)Encontrar los valores de las capacidades parásitas Cgd, Cgs, Cdb, Csb así como la transconductancia del dispositivo. b) Obtener los parámetros para el modelo digital del transistor. 3- Dada la función lógica: kʼn=µn Cʼox=150µA/V2 Cʼox=2,7fF/µm2 Cj=0,86fF/µm2 Cjsw=0,24fF/µm (2 puntos: a) 0,5 puntos; b) 1,5 puntos) F = (A•B + C•D)•(E+F) se pide: a)Suponiendo que se dispone de las señales de entrada en su forma complementada y no complementada, mostrar su implementación FCMOS. b)Considerando el estilo de diseño de puertas estándar, mostrar el diagrama de sticks correspondiente a un layout de la puerta lo más compacto posible. (2 puntos: a) 1 punto; b) 1 punto) 1 de 2 Microelectrónica I 4- I. T. de Telecomunicación, Esp. Sistemas Electrónicos Examen Febrero 2010 Dada la función lógica: F = / [ /A + (/B+C)•/D ] se pide: a)Mostrar el esquema para su implementación FCMOS suponiendo que se dispone de las señales de entrada con ambas polaridades. b)Suponiendo que los transistores del mismo tipo se diseñan con las mismas dimensiones y que se emplea para la implementación un proceso de canal corto de 50nm, con las características: Cʼox=25fF/µm2 Rp=3,4KΩ.µm/Wp(µm), Rn=1,7KΩ.µm/Wn(µm) Wp=1µm, Wn=0,5µm, Lp=Ln=50nm Indicar el retraso de peor caso a través de la puerta cuando se conecta a su salida una capacidad de carga de 60fF. 5- Una puerta NOT CMOS tiene una carga capacitiva de 75pF. Considerando un proceso de canal largo con: (1 punto: a) 0,5 puntos; b) 0,5 puntos) Ln=Lp=2µm, Wn=40µm, Wp=120µm, RʼN=12KΩ, RʼP=36KΩ, Cʼox=800aF/µm2 se pide: a)Encontrar el tiempo de retraso tPLH + tPHL. b)Diseñar un buffer formado por dos NOT en cadena para insertar entre la NOT original y la carga, de tal modo que se minimice el citado retraso. Calcúlese el nuevo valor de tPLH + tPHL y muéstrense las dimensiones de cada uno de los dispositivos en el circuito diseñado. (2 puntos: a) 1 punto; b) 1 punto) 6- a)Diseñar una puerta compleja BiCMOS que implemente la función lógica: F = / [(A+B).(C+D)+E.F] b)Mostrar una segunda versión de la citada puerta. c) Explicar el modo de funcionamiento de la puerta diseñada en el apartado a), indicando para cada situación relevante de las entradas el modo de operación de los transistores bipolares así como los voltajes de salida aproximados. (2 puntos: a) 1 punto; b) 0,5 puntos; c) 0,5 puntos) 2 de 2