Etapas de salida Amplificadores de potencia 1)Introducción Hasta el

Anuncio

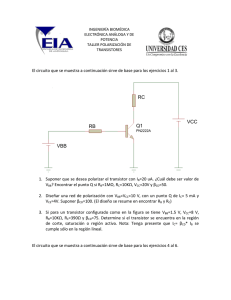

Etapas de salida Amplificadores de potencia 1)Introducción Hasta el momento se analizaron amplificadores de bajo nivel y la condición para tal estudio fue admitir que la tensión base emisor es muy pequeña (comparada con la tensión térmica). Esta suposición implicaba la aproximación a un modelo lineal del transistor en alterna, el cual permite determinar los parámetros útiles en un amplificador. Sin embargo, al trabajar con amplificadores de potencia, no podremos, en general, admitir como válida la hipótesis anterior, por lo que el modelo lineal no será, estrictamente hablando, válido para los amplificadores de potencia. Desde otro punto de vista, vimos las posibles formas de operar de un amplificador según la polarización del transistor, lo que entendemos por clase del amplificador. Vimos en aquel momento que se los clasificaba en clase A, B, AB y C. 2) Amplificador clase A 2.1) Colector común En este tipo de aplicación el transistor está polarizado en el punto Q, es decir pasará por el colector del transistor una corriente continua permanente. En general, la corriente de polarización se logra a través de una fuente de corriente. Un esquema típico podría ser el indicado en la fig.1. Interesa obtener la característica de transferencia de la etapa para analizar si presenta alinealidades. Dicha característica define la relación entre la tensión de salida y la de entrada (Vo = f(Vi)). Para determinarla recorramos la malla de entrada, observándose que Vi - Vbe - Vo = 0, por lo tanto Vo = Vi - Vbe, por lo tanto cuando Vi = 0 deberá cumplirse que Vo = Vbe y también si Vo = 0, Vi = Vbe. Como la salida sigue a la entrada, se tratará de una recta aproximadamente a 45º. El tema que queda por investigar antes de trazar la curva es qué límites tendrá esa recta. En el semiciclo positivo, la tensión de salida sólo podrá alcanzar un valor tal que asegure que el transistor esté en modo activo directo (MAD), por lo tanto, el límite será la saturación de T1.Admitiendo que la tensión colector emisor cuando el TBJ está en modo de saturación (MS), es Vce(sat) = 0.2 V, podemos establecer que la máxima tensión de salida sin recorte por saturación es Vo(máx) = Vcc-Vce(sat). por otra parte, en el semiciclo negativo, pueden producirse dos fenómenos a saber: por un lado, puede saturarse el T2 de la fuente de corriente, con lo cual, mediante un análisis similar al anterior se llega a que Vo(mín) = Vcc + Vce(sat). Por otra parte, puede ser que cuando se esta en la cresta del semiciclo negativo, la corriente en la carga puede alcanzar el valor de la corriente de polarización fijada por la fuente Icq. En tal circunstancia, el T1 pasará a estar en modo de corte (MC). Para este caso Vo(mín) = - Icq RL. Deberíamos entonces tener en cuenta ambas posibilidades y adoptar como valor máximo posible de tensión de salida la menor de las dos como hemos hecho siempre. En virtud de las consideraciones anteriores podemos dibujar la característica de transferencia que es la que podemos observar en la fig. 2 VCC Q3 ic R1 Vg io Q4 0 RL Q2 0 Fig.1 VEE Iq 2.1.1)Balance de potencias Mediante la aplicación del principio de conservación de la energía podemos afirmar que la potencia entregada por las fuentes debe ser igual a la suma de la potencia útil en la carga más la potencia que se disipa en los dispositivos de salida. Matemáticamente expresaremos Ps = Pd + PL, donde Ps es la potencia entregada por las fuentes, Pd es la potencia disipada en los dispositivos de salida y PL es la potencia útil desarrollada en la resistencia de carga. Analicemos ahora por separado cada término. El valor medio de la corriente que entrega cada fuente es la corriente de polarización definida por la fuente de corriente, es decir Icq. Por lo tanto Ps = 2 Vcc Icq Por su parte, la potencia entregada a la carga la podemos determinar, considerando una onda senoidal cuyo valor pico sea el valor máximo admisible sin recorte, determinado como analizamos anteriormente multiplicando los valores eficaces de tensión y corriente, es decir PL = Vo(rms) Io(rms) = (Vomáx Iomáx )/2 Finalmente, la potencia disipada por los dispositivos de salida la podemos obtener mediante la diferencia entre la entregada por las fuentes y la útil en la carga. Mediante este análisis se observa que si no tenemos efecto útil en la carga, es decir sin señal, la potencia disipada en los transistores será máxima, es decir ¡ Consume más cuando no obtenemos efecto útil ! Esta característica es típica de las etapas clase A y hace que esta configuración tenga un comportamiento deficitario desde el punto de vista de la potencia (esperaríamos que los TBJ disiparan más cuanto más potencia entregaran). Para poder medir y comparar el balance de potencias entre las distintas etapas, se define el concepto de rendimiento del mismo modo que se lo hace para el caso de las máquinas, como la relación entre la potencia útil en la carga y la potencia consumida (entregada por las fuentes). En forma analítica podemos escribir η= PL/Ps. Queda claro que el rendimiento estará comprendido entre 0 y 1, aunque desde el punto de vista práctico, está claro que un sistema con rendimiento nulo carece de sentido y, por otra parte tampoco podrá alcanzarse el valor unitario, en virtud que para lograr un efecto útil habrá siempre una pérdida de potencia. Resumiendo 0<η η<1. Interesa pues determinar el rendimiento máximo que puede alcanzar una etapa de salida clase A. Reemplazando en la definición queda η= (Vomáx Iomáx)/2(2Vcc Icq). Es interesante conocer el valor máximo de ese rendimiento para cada clase de amplificador. Por lo tanto deberemos conocer la condición para obtener la máxima potencia en la carga, ya que para igual corriente de polarización, garantizará máximo rendimiento. Para obtener la condición de máxima potencia en la carga, realizaremos el sig. análisis gráfico. Para entender el gráfico anterior hay que determinar previamente la ecuación de la recta de carga; para ello analizamos la malla de salida que involucra a T1. VCC - iO RL - vCE = 0 Por otra parte, aplicando una ecuación de nodos al nodo de RL, queda: iC = iO + IQ, por lo tanto iO = iC - IQ. Reemplazando esta última ec. en la primera resulta VCC - (iC - IQ) RL - vCE = 0 VCC - iC RL + IQ RL - vCE = 0 Finalmente, operando se llega a iC = - vCE / RL + VCC / RL +IQ, que es la ec. de la recta de carga dinámica para esta etapa amplificadora. Establezcamos la ordenada y la abscisa al origen. iC (0) = 0 + VCC / RL + IQ vCE (0) = VCC + IQ RL. Por otra parte, también es interesante saber cuánto vale la tensión de polarización IQ = -VCEQ / RL + VCC / RL + IQ, por lo tanto VCEQ = VCC, hecho previsible desde lo conceptual, en virtud que si iC = IQ es porque iO = 0, en consecuencia vO = 0 y vCE = VCC. Luego de esta disgresión entremos de lleno en el análisis gráfico. Se observan tres rectas de carga, las cuales, es evidente, tienen pendientes distintas y, consecuentemente corresponden a resistencias de carga distintas. Recordando que PL = (Vomáx Iomáx)/2 observamos que las áreas rayadas de los triángulos indicados representan las potencias en la carga para cada recta. Vemos que para la recta "2" esta área es máxima, lo que significa que existirá una resistencia de carga óptima, para la cual el rendimiento y la potencia de salida serán máximos. Por otra parte la recta "1" corresponde a RL < RLóptima y la recta "3" a RL > RLóptima. Como aclaración recordamos algo obvio, pero que no está de más: el área del triángulo es b h /2 y de aquí surge que las áreas de los triángulos formados representan las potencias útiles en las respectivas resistencias de carga. Debemos reconocer también que está claro que la resistencia óptima y la máxima potencia útil se verifican en lo que conocemos como condición de máxima excursión simétrica (MES), es decir cuando la máxima tensión por corte y por saturación coinciden. ¿Cuánto valdrá entonces la resistencia de carga para tal condición? Simplemente analicemos la pendiente de la recta óptima. Como sabemos, la pendiente de la recta de carga es la recíproca de la resistencia de carga, de modo que 1 / RL = IQ / VCC y finalmente RLóptima = VCC / IQ Analizado esto, podemos determinar el valor del rendimiento máximo de esta etapa. PL = (Vomáx Iomáx) / 2 = Vomáx Vomáx / 2 RL, pero Vomáx = VCC, despreciando la tensión de saturación del TBJ, queda η= (Vomáx Iomáx)/2(2Vcc Icq) = (VCC VCC) / 2 RL 1/ 2 VCC VCC/RL = 1/4 η =25 %, es decir que el rendimiento máximo de la etapa clase A no superará el 25 %, es decir que el 75 % de la potencia se disipará en forma de calor en los transistores, por lo cual es, como habíamos anticipado una etapa de bajo rendimiento. 2.1.2) Máxima potencia disipada Como expliqué anteriormente, en ausencia de señal. es decir sin efecto útil en la carga, la potencia disipada será máxima, por lo tanto Pdmáx = Ps. Por supuesto que para cada TBJ debemos considerar la mitad de este valor, el cual deberá ser tenido en cuenta para el cálculo del disipador. 2.2) Emisor común En la fig.3, se observa la configuración típica con una fuente de corriente. Trataremos de determinar la característica de transferencia de esta etapa. En el circuito se observa IQ = iO + iC , por lo que iO = IQ - iC, mientras que la tensión de salida será vO = (IQ - iC) RL y poniendo en función de Vi, resulta vbe + vi Vbe Vi VT vo = IQ − Ise RL = IQ − Ise VT e VT RL Vbe vi VT v Recordando que IQ = Ise y reemplazando vo = IQ 1 − e T RL Fórmula válida en un entorno de Vbe, ya que vemos que con unos pocos mV ya se alcanza los niveles de saturación o corte. En la última expresión observamos además primeramente que existe una inversión de fase como es de esperar que ocurra en toda configuración de emisor común y en segunda instancia vemos que la curva será de tipo exponencial y de ninguna manera lineal como ocurría en el colector común. luego veremos la influencia de este tipo de característica en la distorsión por alinealidad o distorsión armónica. Para trazar la curva falta aún definir los límites de excursiones máximas sin recorte. En el semiciclo positivo de salida (negativo en la entrada), se puede saturar T2, de manera que la tensión máxima podría ser Vomáx = Vcc. SIn embargo podría haber también la posibilidad que T1 pase a MC y en tal caso toda la IQ se drenará a través de la carga. En tal circunstancia Vomáx = IQ RL, por supuesto habrá que adoptar la menor de las dos. Mientras tanto, en el semiciclo negativo la única posibilidad es que sature T1 y la tensión mínima en el semiciclo negativo es Vomín = - Vcc. En virtud de todo lo anterior podemos dibujar la característica del modo sig. VCC Q3 IQ Q2 iO RL Q1 R1 iC 0 Vg VEE exponencial 2.2.1) Balance de potencias El análisis es exactamente el mismo y se arriban a los mismos resultados, ya que no dependen de la configuración, sino de la clase de amplificador. 2.2.2) Distorsión armónica Está claro que si la característica de trasferencia de la etapa no es lineal, la forma de la onda de salida no será exactamente la misma que la de la entrada. Esto lleva a lo que se llama distorsión. Por otra parte si la señal de entrada es una senoide pura, la salida estará constituida por la señal deseada (amplificada), pero además aparecerán componentes de frecuencias múltiples de la original de menor amplitud. Estas componentes de frecuencias múltiples de la original (fundamental), se denominan armónicos, de forma tal que la señal que presente el doble de frecuencia que la fundamental se llamará segundo armónico, la señal que presente el triple de frecuencia se llamará tercer armónico y así sucesivamente. Cabe aclarar además que a la señal fundamental se la suele denominar también primer armónico. SI hacemos un diagrama espectral de la señal, es decir de las amplitudes en función de la frecuencia se vería lo siguiente. En la fig. anterior se observan la fundamental y las armónicas segunda, tercera y cuarta. Vamos ahora a realizar el análisis matemático de la distorsión. Para ello debemos conocer el desarrollo en serie de Taylor de una función en el entorno de cero o lo que se llama también serie de Mc Laurin. Laurin. Partimos de la expresión deducida anteriormente Vo = IQ (1- exp(VI/VT) RL. El desarrollo en serie de Taylor de una función cualquiera, con la única condición que sea derivable en el entorno del punto en el que desea desarrollarla es el siguiente: f ´´( 0) 2 f ´´´( 0 ) 3 f ( x ) = f ( 0) + f ´( x )x + x + x + ... 2! 3! Aplicando este concepto a la expresión de la tensión de salida resulta: vi vi 2 1 vi 3 1 vO = IQ 1 − 1 + + + VT VT 2 VT 6 aproximación de tercer orden. Admitamos ahora que la señal de entrada es senoidal Vi = Vp sen (wt), entonces analizando la expresión anterior, se ve que el término lineal no va a tener ninguna influencia, es decir, reproducirá en la salida una señal semejante a la de entrada. ¿ Pero qué sucede con el término cuadrático?. Para responder esta pregunta debemos primero revisar alguna relaciones trigonométricas sen 2 ( ωt ) + cos 2 ( ωt ) = 1 cos 2 ( ωt ) − sen 2 ( ωt ) = cos( 2ωt ) Restando miembro a miembro ambas expresiones resulta 2 sen 2 ( ω t ) = 1 − cos( 2 ω t ) 1 1 sen 2 ( ω t ) = − cos( 2 ω t ) 2 2 En esta última fórmula se observa que la aparición de un seno cuadrado da origen a componentes del doble de la frecuencia fundamental. Algo semejante ocurre con el seno al cubo, dando origen en este caso a señales del triple de frecuencia que la fundamental. Interesa pues conocer los coeficientes de distorsión de segunda y tercera armónicas. La idea es tener una valoración relativa respecto de la amplitud de la fundamental. 2 Vp VT Vp HD2 = = 0.5 VT Vp 2 VT 3 Vp 2 1 Vp VT HD 3 = = Vp 6 VT 6 VT Se observan dos cosas interesantes; una de ellas, que la distorsión disminuye al bajar la tensión de entrada y la segunda que la distorsión disminuye a medida que aumenta el orden de la armónica. Si Vp << VT, los coeficientes de distorsión serán despreciables y podremos admitir que el sistema se comporta casi linealmente, lo que corresponde, como recordarán a la condición de bajo nivel de señal. Desafortunadamente dicha aproximación es válida en amplificadores de bajo nivel, pero no en amplificadores de potencia. De esta última consideración surge que la etapa clase A en emisor común es muy poco utilizada como amplificador de salida. .3) Etapa clase B (complementaria) Ya vimos que la etapa clase B tiene la característica de estar polarizada al corte de modo tal que si por ejemplo, en el semiciclo positivo se polariza en directa, el TBJ conducirá. Sin embargo durante el semiciclo negativo, el transistor anterior quedará polarizado en inversa imposibilitado de conducir, de manera tal que no habrá tensión de salida sobre la carga. La forma de solucionar tal inconveniente es utilizar dos transistores de polaridad opuesta, lo que se conoce como simetría complementaria. Un circuito básico es el que se indica a continuación. VCC Q1 io Vg Q2 0 RL -VCC 0 El funcionamiento es extremadamente sencillo. Durante el semiciclo positivo el TBJ NPN se encuentra polarizado en directa, es decir trabajando en MAD, mientras que el PNP está polarizado en inversa, de manera que está trabajando en MC. Se drenará a través de T1 la corriente a la carga, de manera de reproducir en la salida el semiciclo positivo. Durante el semiciclo negativo ocurre exactamente lo inverso al caso anterior: el TBJ NPN tiene la juntura base emisor polarizada en inversa, por lo que estará trabajando en MC, sin conducir, mientras que el PNP estará con su juntura BE en directa y en MAD, por lo que entregará corriente a la carga reproduciendo el semiciclo negativo. Habrá una zona entre - 0.6 V y + 0.6 V aproximadamente en la que no conducirán ninguno de los dos TBJ, produciéndose una distorsión a la que se la conoce como distorsión por cruce. Analicemos ahora la característica de transferencia que deberá presentar esta etapa. Deberá cumplirse en el semiciclo positivo que Vi - Vbe = Vo por lo tanto si Vo = 0, Vi = Vbe. Mientras que en el semiciclo negativo Vi + Vbe = Vo por lo que para Vo = 0, Vi = - Vbe y mientras quela tensión de entrada esta comprendida entre Vbe y -Vbe se tiene una salida nula. Finalmente las excursiones máxima y mínima estarán definidas por la saturación del NPN y del PNP, respectivamente. En virtud de lo antedicho, la curva de transferencia de esta etapa será la indicada en la fig. sig. Hay que tener en cuenta que, eventualmente y, fundamentalmente si ls ganancia de corriente del TBJ es baja, podría producirse un recorte en el hemiciclo positivo por falta de corriente en la base de T1. Este problema se verá más en detalle con los ejemplos prácticos. En el gráfico sig. puede observarse el efecto de deformación en la forma de onda de salida por la distorsión por cruce para señales de muy bajo nivel. Por lo tanto será necesario implementar algún método para eliminar esta deformación, para ello se recurrirá a la configuración clase AB, en la cual se polariza al transistor un poquito por encima del corte, de manera que siempre haya una pequeña corriente de colector, lo cual permitirá tener tensión sobre la carga aún con tensiones muy bajas en la entrada. Más adelante analizaremos con cierto detalle dicha configuración. 3.1) Balance de potencias Por supuesto sigue siendo válido el principio de conservación de la energía, pero cambiará la forma de calcular cada uno de los términos involucrados en la expresión. Ps = Pd + PL La corriente tomada de cada fuente tiene ahora la forma de una onda semirrectificada en virtud que cada TBJ conduce sólo medio ciclo. Por lo tanto el valor medio de esa corriente puede determinarse según las expresiones deducidas en el curso anterior, es decir Im = Ip /π π y, consecuentemente la potencia total tomada de las fuentes será Ps = 2 Vcc Im = 2 Vcc Ip /π π. Por otra parte, la corriente de pico es la corriente máxima en la carga y ella depende de la máxima excursión de salida sin recorte, es decir Ip = Iomáx = Vomáx / RL y en el mejor de los casos, esta tensión estará muy cercana a la de la fuente (saturación) difiriendo sólo en la Vce(sat) de alrededor de los 0,2 V, por lo que en general podrá despreciarse con los valores comunes de la tensión de alimentación. En virtud de esto último, la potencia tomada de las fuentes será Ps = 2 Vcc Vcc / πRL 2VCC 2 Ps = π RL Vomáx 2 Por lo tanto, el 2RL VCC 2 π rendimiento de esta etapa podemos calcularlo del sig. modo η = 2RL 2 = = 78% 4 2 VCC πRL mucho más elevado que el de la configuración tipo clase A En otro orden de cosas, la potencia derivada a la carga será PL = 3.1.2) Máxima potencia disipada En el amplificador clase A, vimos que es obvio que la máxima potencia disipada por el dispositivo de salida tiene lugar cuando la potencia entregada a la carga es nula, caso que puede ocurrir si el operador ubica el control de volumen al mínimo si se trata de un amplificador de audio. Para el amplificador clase B no puede utilizarse el mismo criterio en virtud que si la potencia entregada a la carga es nula, también lo es la potencia disipada en los transistores, cosa beneficiosa desde el punto de vista de la eficiencia. Por lo tanto habrá que determinar el valor de tensión de salida que hace máxima la potencia 2 VCCVo Vo 2 disipada en los TBJ. Podemos escribir que Pd = Ps − PL = − 2RL πRL Se trata de una función de segundo grado, cuya gráfica será una parábola y cuyo vértice (máximo) puede obtenerse mediante el cálculo diferencial, es decir haciendo la derivada e igualando a cero, pues si la función tiene un máximo a un mínimo, la pendiente en ese punto es nula, como se observa en la gráfica sig. d (Pd) / d Vo = 0 d (Pd) / d Vo = 2 Vcc / π RL - 2 Vo / 2 RL = 0 Simplificando y operando algebraicamente obtenemos que Vo = 2 Vcc / π y si reemplazamos en la expresión de Pd, resulta 4 VCC 2 4 VCC 2 VCC 2 Pd = − 2 =2 2 πRL 2π RL π RL Puede demostrarse que el rendimiento para la condición de la máxima potencia disipada será η = 50% Es decir que cuando la potencia disipada es máxima, entonces el rendimiento es mucho menor que el máximo obtenible, lo cual es lógico, pensando que si hay más consumo, la eficiencia va a disminuir. Finalmente, si nos interesa la potencia máxima por dispositivo, que será el valor a utilizar para el cálculo del disipador deberemos dividir por dos la potencia anteriormente calculada, es decir Pd máx (cada TBJ) = (Vcc|2) / (π|2) (π RL 4) Etapa clase AB Vimos cuando analizamos la característica de transferencia de la etapa clase B que aparecía una zona en la cual los diodos no conducen, lo cual se traducía en la distorsión por cruce. Para resolver el problema, es necesario llevar a los transistores a un valor de polarización del orden de los 0.6 V para que exista una pequeña corriente de manera que no entren estrictamente en MC y conduzca corriente a la carga para bajos niveles en la tensión de entrada. Esto puede lograrse fácilmente colocando dos diodos en serie entre las bases de ambos TBJ como se observa en la fig.sig. VCC Q1 io Vg D1 0 D2 Q2 -VCC RL 0 Por supuesto, a los diodos hay que polarizarlos a través de una resistencia o fuente de corriente. La característica de transferencia será la sig. Analizando el circuito queda claro que Vi + 2 Vbe = Vo. Cuando Vo = 0, deberá cumplirse que Vi = - Vbe. Por otra parte, si Vi = 0, entonces Vo = Vbe. Por lo tanto podemos dibujar la característica: Por supuesto, hay que tener e cuenta en cuanto al recorte de la señal si no existe una limitación también por falta de corriente en el hemiciclo positivo. Se observa además que ha desaparecido la zona de distorsión por cruce. Por esta razón es que se trata de la etapa más usada. Además debemos aclarar que si bien la forma más económica de obtener la prepolarización es mediante los diodos, también suelen usarse métodos más caros, pero también más efectivos como por ejemplo el llamado multiplicador de Vbe.. El circuito completo es el dibujado a continuación y lo podemos analizar del sig. modo. Para el TBJ central se puede plantear el divisor de tensión de base Vbe = Vce R2 / (R1+R2) de donde podemos despejar el valor de Vce que representa la tensión de polarización de los transistores. Vce = Vbe (R1 / R2 +1). Vemos que poniendo un potenciómetro como divisor de base fácilmente podemos obtener la tensión justa para prepolarizar a los TBJ. En general se ajusta el potenciómetro de base para obtener una cierta corriente de algunos miliampere o si disponemos de algún instrumental usando un osciloscopio para verificar cuando desaparece la distorsión por cruce. A R1 Q1 R2 Vo B 5) Sistemas de protección Si por alguna falla, se pone en cortocircuito la salida, es posible que se supere la máxima corriente que el TBJ es capaz de soportar. por lo tanto, los buenos amplificadores tienen algún circuito adicional de protección. Uno de los más comunes es el dibujado a continuación. EL funcionamiento es sencillo. Cuando la corriente de salida es tal que hace caer 0,6 V en la resistencia Rm, entonces comenzará a conducir el T2 de manera que el colector de este último tomará corriente de la base de T1, restándole a este último posibilidad de conducir, con lo cual evitará su destrucción. Algo similar ocurre podría ocurrir con el transistor PNP. Habrá simplemente que elegir el valor de Rm de forma tal que cuando la corriente de salida llegue al valor máximo, la caída en dicha resistencia alcance la tensión de encendido del transistor de salida. VCC R3 Q1 Q2 D1 R1 R2 R4 D2 Q3 0 Q4 Vg BC546B 0 -VCC 6) Etapa cuasicomplementaria Puede construirse una etapa de salida con transistores Darlington, lo cual aumenta la capacidad de manejo de corriente del dispositivo como vimos en su momento. Además es fácilmente obtenible un Darlington de tipo PNP con un transistor NPN, lo cual mejora la capacidad de entregar corriente, ya que la movilidad de los electrones es mayor que la de los huecos. VCC D3 Q7 Q2 R3 1k Q3 D1 0 D2 Q4 Q5 Q6 Vg -VCC 0