Síntesis NAND NOR

Anuncio

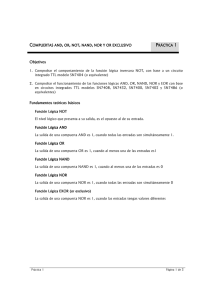

Síntesis NAND_NOR EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 1 Síntesis NAND NOR Síntesis NAND_NOR Introducción EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 2 • Hasta ahora las implementaciones en dos niveles que hemos sintetizado están formadas por varias compuertas AND más una compuerta OR a la salida (circuitos AND–OR) o varias OR más una AND a la salida (circuitos OR–AND). • Las compuertas NAND (o NOR) constituyen por separado un conjunto suficiente de operadores, es decir, que todas las funciones de lógicas podrán expresarse con sólo compuertas NAND (o NOR) e inversores. • La ventaja es que sólo utilizaríamos un mismo tipo de compuertas que serían del mismo o menor costo y un solo puesto de trabajo para el montaje que las AND y OR o sus combinaciones. Síntesis NAND_NOR Circuitos con dos niveles EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 3 • Teorema: Dado un circuito AND–OR en el que todas las entradas externas actúen sobre las compuertas AND, si cada una de las compuertas del circuito se sustituyen por una compuerta NAND del mismo número de entradas, la función realizada por el circuito no cambia. Síntesis NAND_NOR Demostración EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 4 • Circuito AND OR • Circuito NAND NAND E1 E2 E3 Ep f ( E1, E2 ,...E P ) = X + .... + W X W f ( E1, E2 ,...E P ) = X ....W f ( E1, E2 ,...E P ) = X + .... + W f ( E1, E2 ,...E P ) = X + .... + W Síntesis NAND_NOR Circuitos de dos niveles EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 5 • Teorema: Dado un circuito de dos niveles OR–AND en el que todas las entradas externas actúen sobre las compuertas OR, si cada una de las compuertas del circuito se sustituye por una compuerta NOR del mismo número de entradas, la función realizada por el circuito no cambia. Síntesis NAND_NOR Demostración EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 6 • Circuito OR AND f ( E1, E2 ,...E P ) = X ....W • Circuito NOR NOR f ( E1, E2 ,...EP ) = X + .... + W f ( E1, E2 ,...E P ) = X ....W f ( E1, E2 ,...E P ) = X ....W Síntesis NAND_NOR Circuitos con más de dos niveles de compuertas EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 7 • Supongamos un circuito AND–OR donde existen entradas externas a la compuerta de salida. • Se puede comprobar que la sustitución NAND se realiza si las entradas externas a la compuerta de salida se complementan. Síntesis NAND_NOR Demostración EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 8 • Circuito AND OR • Circuito NAND NAND 1 2 3 p f ( E1, E2 , E3 , E P ) = X + Z + W f ( E1, E2 , E3 , E P ) = XZ W f ( E1, E2 , E3 , E P ) = X + Z + W Síntesis NAND_NOR Circuitos con más de dos niveles EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 9 • Supongamos circuitos con compuertas AND y OR con más de dos niveles: • En circuitos con niveles alternados de compuertas AND–OR se puede pasar a un circuito con compuertas NAND complementando únicamente las entradas a las compuertas OR ya que podemos ir sustituyendo el circuito global por subcircuitos de dos niveles AND–OR y sustituir al igual que en el caso anterior. Síntesis NAND_NOR EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 10 Ejemplo • Se subdivide el circuito en niveles NAND OR. Síntesis NAND_NOR Solución EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 11 Síntesis NAND_NOR Circuitos con mas de dos niveles EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 12 • Si el circuito no se puede estructurar en niveles alternados de compuertas AND y OR entonces se descompone en subcircuitos que puedan estructurarse en niveles AND–OR. • Luego se transforma cada uno de estos circuitos en compuertas NAND. • Y luego se ensamblan. Síntesis NAND_NOR Circuito con más de dos niveles EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 13 Síntesis NAND_NOR Agrupación en subcircuitos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 14 A B C D E F G H Síntesis NAND_NOR Subcircuitos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 15 • Subcircuito X • Subcircuito Y Síntesis NAND_NOR Subcircuitos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 16 • Subcircuito V • subcircuito Síntesis NAND_NOR Solución EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 17