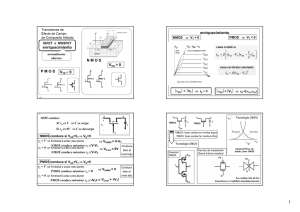

V P MOS N MOS V > 0 enriquecimiento

Anuncio

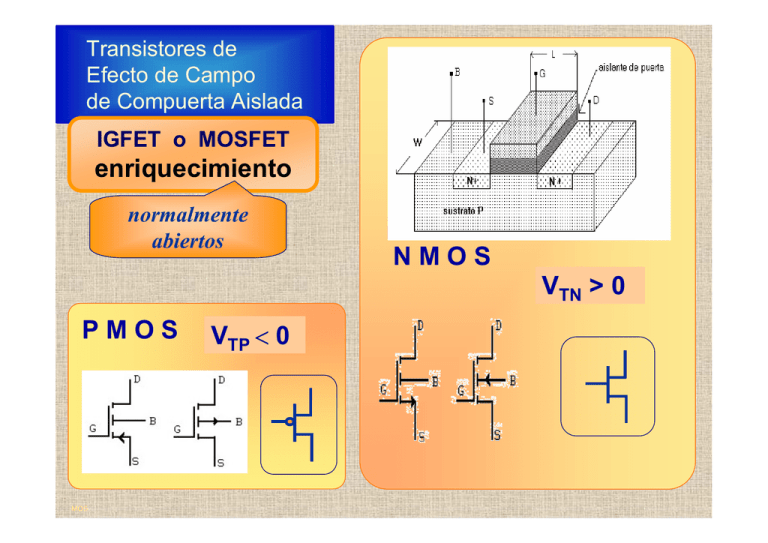

Transistores de Efecto de Campo de Compuerta Aislada IGFET o MOSFET enriquecimiento normalmente abiertos NMOS VTN > 0 PMOS MOS VTP < 0 enriquecimiento NMOS ⇒ VT > 0 PMOS ⇒ VT < 0 zona resistiva 1 2 i D = β (vGS − VT )v DS − v DS 2 zona corriente constante i D = β (vGS − VT ) 2 vGS < VT ⇒ iD = 0 vGS>VT ⇒ iD=f(vGS,vDS) PT MOS conduce Si va es V ⇒ C se carga Si va es 0V ⇒ C se descarga b a + va C G NMOS conduce si VGS>VT ⇒ VG=V va = V ⇒ Terminal b actúa como fuente ⇒ VCMÁX = V-VT NMOS conduce mientras vC ≤ V-VT Conduce va = 0 ⇒ Terminal a actúa como fuente ⇒ VCmín = 0V bien el NMOS conduce mientras vC ≤ V-VT nivel bajo PMOS conduce si VGS<VT ⇒ VG=0 va = V ⇒ Terminal a actúa como fuente Conduce ⇒ VCMÁX = V PMOS conduce mientras va = V bien el nivel alto va = 0 ⇒ Terminal b actúa como fuente PMOS conduce mientras vC ≤ -lVTl ⇒ VCmín = -lVTl a b a C NMOS rON b PMOS Tecnología CMOS C VDD rON-NMOS NMOS: buen conductor niveles bajos PMOS: buen conductor niveles altos r pt Tecnología CMOS Inversor CMOS vi VDD rON-PMOS Puertas de transmisión (llaves bidireccionales) NK v ent Característica de salida Llave CMOS NK vo K K VSS La conducción de los transistores se habilita simultáneamente CMOS ular p o p s gía má o l o n c La t e Simplicidad de diseño No disipa potencia vo id V A B DD Altos niveles de integración C .5VDD D VTN VC E vi V + VTP V DD DD Inversor CMOS zona corriente constante zona resistiva 1 2 i D = β (vGS − VT )v DS − v DS 2 i DN ≡ i DP V A 2 Conmutación se produce con ambos transistores en zona corriente constante B DD ( β N (v i − VTN ) = β P V − v i − VTP 2 vo id i D = β (vGS − VT ) VC = VDD − VTP + VTN 1+ C .5VDD D VC βN βP depende de la geometría KK VTN βN βP E vi β = µ Cox W L V + VTP V DD DD depende de la tecnología ) 2 Influencia de las características de los transistores β / β =1 vo N P β / β = 0,1 VDD N .5VDD P si VTN VDD+ V TP V .5VDD vi DD β P = µ P C ox WP LP P β / β = 10 N β N = µ N C ox WN LN LN = LP β N µN WN = β P µ P WP depende del tamaño de los transistores Circuitos Lógicos CMOS Salida siempre conectada (VDD o VSS) red PMOS conectada a VDD (llaves de pull-up) VDD VDD VDD RED P entradas salida salida salida RED N VSS VSS VSS Consumo de potencia red NMOS conectada a VSS (llaves de pull-down) estática nulo Independencia de la temperatura Inmunidad al ruido y a variaciones de la alimentación Implementar el circuito CMOS para las siguientes compuertas lógicas básicas Fabricación de Circuitos Integrados María Isabel Schiavon - 2006 TOTALMENTE DEDICADOS (full custom) El diseñador provee al fabricante el tamaño, ubicación física e interconexión de cada transistor para lograr la funcionalidad deseada para el CI LAYOUT Conjunto de máscaras que conforman el total del CI y se correlacionan con los pasos necesarios para su fabricación Cada máscara representa la forma, tamaño y distribución de los materiales para una cierta tecnología de fabricación Se especifica en un archivo de texto de formato predeterminado y normalizado (CIF, GSD) ASIC´s 16 FULL CUSTOM El diseñador es responsable de todos los pasos del diseño. Diseña, ubica e interconecta cada uno de los elementos que conforman el circuito, asegurando el correcto funcionamiento de acuerdo a especificaciones de funcionamiento y de la tecnología (reglas de diseño) pads celdas funcionales Con esta información, en la fundición de silicio se generan las máscaras necesarias para fabricar el circuito ASIC´s 17 Proceso Pozo N Proceso Doble Pozo Proceso Pozo P Proceso SOI CMOS: etapas proceso fabricación Máscara 1 Difusión de pozo Pozo ÓXIDO DE CAMPO N-WELL SUSTRATO P CMOS: etapas proceso fabricación Máscara 2 Definición de áreas activas Área activa ÓXIDO FINO CMOS: etapas proceso fabricación Máscara 3 Definición de las puertas Polisilicio POLISILICIO CMOS: etapas proceso fabricación Máscara 4 Difusión n+ MOS canal N Implante N+ N+ N+ CMOS: etapas proceso fabricación Máscara 5 Difusión p+ MOS canal P Implante P+ P+ P+ CMOS: etapas proceso fabricación Máscara 6 Perforaciones de contacto Contactos CMOS: etapas proceso fabricación Máscara 7 Metalización Metal Máscara 8 Pasivación Conexionado (micro soldaduras) Sección inversor CMOS Layout inversor CMOS Latch-up Generación de un camino de baja impedancia entre alimentación y tierra en un CI CMOS debido a la formación de transistores bipolares parásitos. T1 y T2 forman circuito tiristor La circulación de corrientes parásitas con Rw y Rs no nulas pueden provocar la conducción de T1 y T2 en forma simultánea Cortocircuito entre Vdd y VSS Reducción ganancia transistores parásitos Mayor distancia entre dispositivos diferentes tipos Anillos de guarda Contactos de pozo Etapas proceso CMOS ÓXIDO DE CAMPO Pozo N-WELL SUSTRATO P Área activa Polisilicio ÓXIDO FINO POLISILICIO ASIC´s 30 Implante N+ Implante P+ N+ N+ P+ P+ Contactos Metal ASIC´s 31 Inversor CMOS Layout y sección VSS VDD vout v in SiO2 N+ N+ P+ P+ Pozo N Sustrato P Inversor CMOS Distintos layouts Etapas del diseño ETAPAS DEL PROYECTO especificación circuito concepción y diseño prototipos ensayo, verificación caracterización Fabricación en serie definición arquitectura verificación funcional diseño lógico y verificación diseño circuital y verificación Diseño Circuital y verificación Circuito a nivel transistores Dimensionamiento transistores Simulación eléctrica pre lay-out Implementación del layout Verificación reglas diseño Extracción del circuito Simulación eléctrica post lay-out Reglas de Diseño MASCARA Area Activa Pozo N REGLA DIMENSION Mínimo ancho 2λ Separación mínima entre áreas activas de igual clase 2λ Separación mínima entre áreas activas de distinta clase 4 λ Mínimo ancho 4 λ Mínimo espacio (igual potencial) 3λ Mínimo espacio (≠ potencial) 6 λ Mínimo solapamiento con área activa interna 3λ Mínimo espacio a área activa externa 5λ