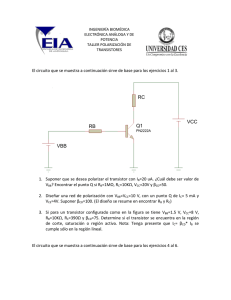

Tema3: El problema de la polarización

Anuncio