Análisis de una puerta lógica

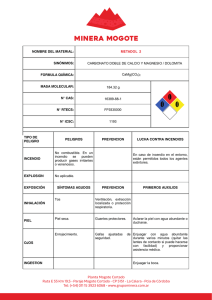

Anuncio

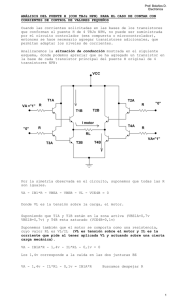

PRÁCTICA 1: ANÁLISIS DE UNA PUERTA LÓGICA TTL. • OBJETIVO DE LA PRÁCTICA. Durante la realización de esta práctica hemos comprobado que el circuito de la figura 1 es efectivamente una puerta NAND. También calcularemos las características estáticas y de transferencia y veremos el estado de polarización de los transistores para las distintas combinaciones de las entradas. • FUNCIÓN LÓGICA. Se trata de una puerta lógica NAND cuya tabla de verdad se muestra en la siguiente tabla: V1 V2 V0 0 0 1 0 1 1 1 0 1 1 1 0 • CARACTERÍSTICA ESTÁTICA En la tabla que presentamos a continuación se muestran los valores obtenidos experimentalmente: Podemos observar como entre 1'2 y 1'5 V se produce la conmutación de la puerta de 1 a 0, siendo ésta muy rápida. • ESTADO DE LOS TRANSISTORES. Para valor lógica alto y bajo a la salidavamos a anotar los valores de las tensiones de base, emisor y colector de cada transistor. Veremos en función de estos datos en qué estado se encuentran los transistores. En primer lugar mostramos los resultados obtenidos para T1='0' y T2='1'. T1 T2 T3 T4 Vbase 0.641 0.641 0.015 0 Vemisor 0 0.053 0 0 Vcolector 0.015 0.015 5.167 5.167 Con estos datos concluimos que el estado de los transistores es: T1−>Cortado. T2−>Activa inversa. T3−>Cortado. 1 T4−>Cortado. Mostramos ahora los resultados obtenidos con T1='1' y T2='1'. T1 T2 T3 T4 Vbase 0.641 1.31 0.666 1.94 Vemisor 0 0.666 0 1.33 Vcolector 0.015 0.958 0.014 1.311 El estado de los transistores es el siguiente: T1−>Cortado. T2−> Cortado. T3−>Activa. T4−>Saturación. Figura 1 2 3