caché - Departamento de Arquitectura y Tecnología de Computadores

Anuncio

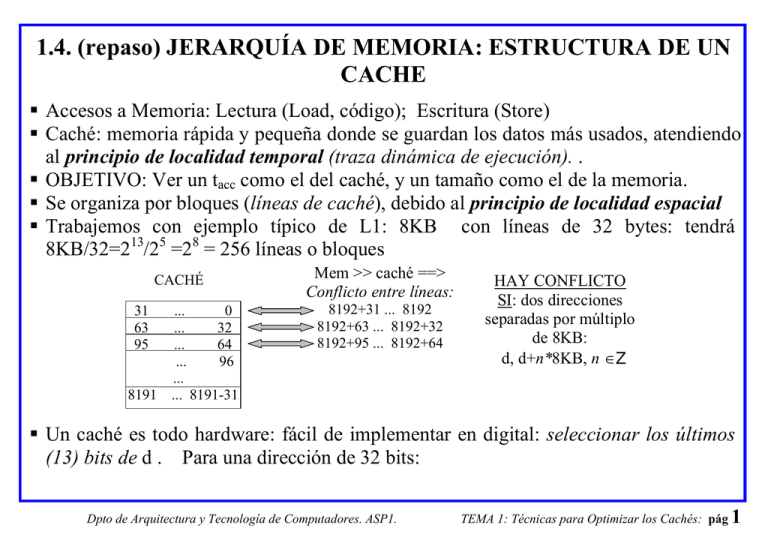

1.4. (repaso) JERARQUÍA DE MEMORIA: ESTRUCTURA DE UN

CACHE

Accesos a Memoria: Lectura (Load, código); Escritura (Store)

Caché: memoria rápida y pequeña donde se guardan los datos más usados, atendiendo

al principio de localidad temporal (traza dinámica de ejecución). .

OBJETIVO: Ver un tacc como el del caché, y un tamaño como el de la memoria.

Se organiza por bloques (líneas de caché), debido al principio de localidad espacial

Trabajemos con ejemplo típico de L1: 8KB con líneas de 32 bytes: tendrá

8KB/32=213/25 =28 = 256 líneas o bloques

CACHÉ

31

63

95

...

0

...

32

...

64

...

96

...

8191 ... 8191-31

Mem >> caché ==>

Conflicto entre líneas:

8192+31 ... 8192

8192+63 ... 8192+32

8192+95 ... 8192+64

HAY CONFLICTO

SI: dos direcciones

separadas por múltiplo

de 8KB:

d, d+n*8KB, n ∈Z

Un caché es todo hardware: fácil de implementar en digital: seleccionar los últimos

(13) bits de d . Para una dirección de 32 bits:

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 1

ETIQUETA

Dir. dentro de caché

19

13

Las etiquetas se almacenan en la caché (“tag memory”) para distinguir entre dos

líneas que entren en conflicto

MEMORIA

CACHÉ

31

ZONA DE

DATOS

31

...

0

...

0

ZONA DE ETIQUETAS

(19 bits por línea)

00

...

0000

00

...

0000

8191 ... 8191-31

8192+31 ... 8192

13

8191 ... 8191-31

CPU

BUS DE DIRECC

32

19

=?

Acierto/Fallo

Hit/Miss

Acierto (Hit). Pocos ciclos CPU: thit. Porcentaje de aciertos: HR (Hit Rate)

Fallo (Miss). traer dato de L2: tiempo de penalidad Pmiss (Penalty miss), del orden de

10 ciclos para L2, 100 para memoria. Porcentaje de fallos: MR (Miss Rate)

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 2

HR + MR = 1

tiempo de acceso medio (para todo acceso, siempre hay que gastar el thit):

tacc = HR * thit + MR (thit +Pmiss) = thit + MR Pmiss

Ejemplo: caché con 95% de aciertos y thit=1 ciclos, Acceso a L2: 12 ciclos:

tacc = 1 +0.05 * 12 = 1.6 ciclos

Asociatividad:

¿Y si muchas direcciones de un programa se diferencian en un múltiplo de 8KB?:

char a[8192], b[8192], c[8192];

for (i=0; i<8192 ; i++) a[i]= b[i] + c[i];

Caché dividido en “vías”, y cada línea puede ubicarse en cualquiera de ellas.

CACHÉ DE CUATRO VÍAS

2 KB por vía x 4 = 8 KB

Conjunto

VÍA 0:

VÍA 1:

VÍA 2:

c[i]

b[i]

a[i]

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

VÍA 3:

TEMA 1: Técnicas para Optimizar los Cachés: pág 3

Conjunto: grupo de líneas que se ubican en la misma dirección de las diferentes vías

(el mismo dato puede estar en cualquier vía, dentro de un conjunto).

El caché es asociativo por conjuntos.

Si sólo tiene una vía: caché de mapeado (correspondencia) directo.

Los cachés de datos suelen tener 2, 4 e incluso 8 vías. Los de instrucciones 1 ó 2.

Más asociatividad ⇒ MR menor. Regla empírica 2:1, “un caché de una vía tiene

tanto MR, como una caché de dos vías de la mitad de tamaño”.

Pero hay que buscar el dato en todas las vías (más comparaciones de etiq; más hw. ⇒

más thit) ⇒ COMPROMISO.

Ejemplo: memoria virtual es completamente asociativa, es decir, tiene tantas vías

como páginas (bloques) hay en memoria física.

¿Qué línea de un conjunto expulsar? Algoritmos fáciles de implementar en hardware:

o Aleatorio

o LRU (Least Recently Used). Implementación con contadores de pocos bits.

o Menos veces accedido. Implementación con contadores de pocos bits.

Políticas de escritura (caché de datos)

Actualización: dos posibilidades:

o Caché de actualización permanente. Write Through (WT, “escritura directa”).

VENTAJA: Toda línea expulsada está coherente.

INCONV: Hacer un acceso mucho más lento (consume AB).

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 4

o Caché de actualización retrasada (Copy Back , CB o Write Back)

Marcar la línea de caché como sucia o modificada (bit Limpia/Sucia, L/S).

VENTAJA: Sólo se accede a memoria, cuando la línea es expulsada.

Alojamiento: dos posibilidades:

o Carga ante fallo de escritura (Write Allocate, WA).

Si el bloque (línea) va a ser accedido más veces, esto conviene.

o No carga ante fallo de escritura (No Write Allocate, NoWA).

A veces un porcentaje elevado de las escrituras de los prog. son aisladas.

Cada política tiene sus pros y contras, los cachés de datos L1 suelen ser CB, WA

Ejemplo claro: páginas de memoria virtual son siempre Copy Back Write Allocate,

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 5

EJEMPLO DE COMPORTAMIENTO DE CACHÉS

• Porcentaje típico de instrucciones de lectura (Load) es 25% (progr. para RISC)

• Porcentaje de escrituras (Store) es del 9%. (progr. para RISC).

El propio acceso al código de una instrucción (caché de instrucciones) es una lectura de

memoria. Luego las instrucciones Ld/St acceden dos veces y el resto sólo 1.

• Nº de Accesos por Instrucción (NAI)= (100+25+9) / 100 =1.34

• Porcentaje de accesos al caché de datos:

(25+9) / (100+25+9) = 25.4 %

• Porcentaje de accesos al caché de instrucciones: 100 / (100+25+9) = 74.6 %

• Porcentaje total de accesos de lectura: (100+25) / (100+25+9) = 93.28%

• Porcentaje total de accesos de escritura: 9 / (100+25+9) = 6.72%

• Porcentaje de accesos de lectura al caché de datos: 25 / (25+9) = 73.5%

• Porcentaje de accesos de escritura al caché de datos: 9 / (25+9) = 26.5%

• Porcentaje de fallos de acceso al caché instr: MR,instr típicam. de 0.5% a 3%

• Porcentaje de fallos de acceso al caché datos: MR,datos típicam. mayor, de 2% a 10%

• Porcentaje de fallos de lectura (al caché datos) es típicamente bastante menor que el

de escritura: MR,lect,datos < MR,escrit,datos

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 6

EJERCICIO

Calcular el MR de acceso a L1datos si se ejecuta el siguiente bucle de 16 iteraciones (sí

deben considerarse los fallos forzosos, es decir, la caché está vacía, y cualquier acceso

inicial es un fallo) para un caché de datos de 16 KB, con línea =4 pal. para los casos:

• R1 inicialmente múltiplo de 16, frente a R1 múltiplo de 16 + 12 (R1 mod 16=12).

• CB, No WA, frente a CB, WA.

• ¿Y si sustituyo el último SW por LW R5, 1024 (R1)?

; R1 apunta inicialmente al primer elemento de un array.

Bucle:

Load R4, 0(R1)

Otra instrucción

Store 0(R1), R4

Store 4(R1), R4

Store 1024(R1), R4

ADD R1, R1, 1024

Otra instrucción

Salto condicional

1ª ITER

Fallo forzoso

Acierto

Acierto

Fallo

RESTO ITER

Acierto si WA.

Fallo si No WA

Acierto

Acierto

Fallo

// PARA R1 MÚLTIPLO DE 16

SOLUCIÓN: MR,WA=17/(16*4), 17 fallos, 2 en la primera iter. y 1 en el resto.

MR,NoWA=32/(16*4), 2 fallos en todas las iter. El NAI=1.5 accesos/instr

EJERCICIOS: - ¿Influye nº vías?

- Pensar en valor inicial de R1: si no es múltiplo de 16, el 2º SW falla.

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 7

1.4. TÉCNICAS PARA OPTIMIZAR LOS CACHÉS

Tiempo de acceso medio:

tacc = thit + MR Pmiss

Se pueden clasificar las técnicas para reducir

tacc según el parámetro que reducen.

Técnicas que reducen Pmiss

Varios niveles de caché:

La memoria DRAM es lentísima hoy respecto a CPU: tendría Pmiss altísimo.

Interesa thit chico: L1 rápida y pequeña (thit es proporcional al tamaño de caché).

Interesa MR chico: L1 no tan pequeña (MR es invers. proporcional al tamaño de caché).

Solución: otros L2, L3 cuyo tamaño crece progresivamente + ponderar tam L1

o L2, L3 son caros (SRAM)

o Pmiss,L1 = thit,L2 crece con tamaño.

Tiempo de acceso medio complicado:

tacc = thit,L1 + MR,L1 Pmiss,L1= thit,L1 + MR,L1 (thit,L2 + MR,L2 Pmiss,L2)

MR,L2 es MR “local”: suele ser alto (L1 se lleva la “crema” de los accesos locales)

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 8

Interesa mayor asociatividad de L2 y otras complejidades (sólo afecta a Pmiss,L1 y no a

thit,L1)

Ley empírica: tam (Lj) >= 4*tam(Lj-1)

Suele implementarse inclusión de L1 en L2. Por simplicidad interesa tam_línea (L1)=

tam_línea (L2)

Si L1 es WT Î L2 es CB.

Buffer de escritura:

Lecturas pueden bloquear la CPU; escrituras, no.

Almacenar escrituras en buffer (de WT o CB), que bajan al siguiente nivel cuando

bus está libre.

Necesito: comparador de direcciones del buffer con la dirección de cualquier lectura.

Interesa generalmente que el buffer se pueda organizar por líneas: si p ej 3 escrituras

caen en la misma línea, se hace un acceso de línea completa (mejor que 3 accesos)

Caché de líneas víctimas:

Unas pocas de líneas totalmente asociativas por si existen muchos conflictos en un

conjunto.

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 9

Interesante: caché mapeado directo con caché víctimas de más de 4 líneas: absorbe

más del 25% de los fallos.

Caché que no se bloquea ante fallo:

Procesadores simples se bloquean completamente ante fallo.

Procesador moderno intenta seguir ejecutando otras instrucciones (se verá en tema 3):

interesa que caché siga sirviendo otros datos mientras se trae la línea del fallo.

En paralelo hace ambas cosas. Pmiss se “oculta”. Tiempos no son aditivos.

La fórmula tacc = thit + MR Pmiss no sirve aquí, pues el verdadero tiempo que se

pierde en un fallo, depende de los accesos que se hayan podido paralelizar

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 10

thit

Caché normal

thit

thit+PMiss

Accesos

Caché no bloqueable

thit+PMiss

Accesos

thit

thit

thit

thit

thit

Tiempo total

thit

Tiempo total

En general Pmiss,L1 se puede ocultar bastante (del 30-50%) si se acierta en L2, pero los

fallos de L2 no son fáciles de ocultar (muchos ciclos sin que llegue el dato

necesario).

Técnicas que reducen MR

Modelo regla de las 3 C (4 C para multiprocesadores)

Forzoso (“Compulsory”): fallos forzosos o inaugurales. Supongo caché infinito.

Capacidad. Supongo completamente asociativo.

Conflicto. Fallos de colisión.

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 11

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 12

Forzoso: sólo se reducen aumentando tamaño línea. Pero aumenta Pmiss.

Capacidad. sólo se reducen aumentando tamaño caché: da idea del tamaño (L2).

Conflicto. se reducen aumentando asociatividad. Pero aumenta thit.

Aumentar tamaño línea:

Reduce fallos forzosos (aprovecha más la localidad espacial).

Pero aumenta PMiss. Cuidado: producto MR * PMiss

Además pocas líneas: mucho MR

Ejemplo: páginas de 4KB o más porque latencia disco es alta y AB también.

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 13

Prebúsqueda hardware de instrucciones o datos:

Instrucciones: además de traerse una línea se guarda la siguiente en un buffer (traza

bastante secuencial). Si el buffer tiene varias líneas guardadas, éste captura en torno a

la mitad de los fallos.

Datos: accesos más dispersos: buffer mayor tamaño. Se calcula la zancada (distancia

entre dos fallos) y se busca la línea distanciada tal zancada. “Patrón de accesos”.

“Smart caché” en Pentium 4, L2.

Prebúsqueda software: compilador o programador:

Añadir una instrucción que sólo sirve para cargar un dato antes de usarlo.

for (j=0; j<1000 ; j++) a[i][j]= b[i][j] + c[j][i];

//c[][] se accede por columnas: mala localidad

//a[][] y b[][] se accede por filas: buena localidad

Se podría escribir así, sup. que un acceso a L2 dura 10 iteraciones (estimarlo):

for (j=0; j<1000 ; j++) {

prefetch(c[j+10][i]);

a[i][j]= b[i][j] + c[j][i];

} //no se contempla los fallos de primeras iteraciones

// ni las precargas inútiles de las últimas iter.

//Peligro: muchas instr. Prefecth añadidas Î más tiempo.

//EJERCICIO: escribir código para evitar los 3 comentarios

// anteriores

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 14

Punteros: más difícil calcular los prefetch, pero también se evitan muchos fallos.

Prefetch usual: se prohibe que provoque un fallo de página.

Ocurre que una prebúsqueda hardware puede precargar bien si el patrón es simple.

Optimizaciones del compilador/programador:

Aumentar la localidad de los accesos a instrucciones:

o Reordenar/reubicar código para evitar conflicto entre procedimientos que se usan

a la vez.

o Alinear para que las instrucciones de arranque (tras un salto) sean las primeras de

una línea.

o Resultados: se puede conseguir que un caché de instrucciones de mapeado

directo tenga menos MR que uno de 8 vías

Aumentar la localidad de los accesos a datos. Ordenación de:

o Recorrido por filas / columnas de matrices

o Estructura de vectores (SOA) suele ser mejor que vectores de estructuras (AOS)

Normalmente solo se usa un campo, pero…

CONTRAEJEMPLO:

struct {char a[8192]; char b[8192] char c[8192]; }

for (i=0; i<8192 ; i++) s.a[i]= s.b[i] + s.c[i];

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

s;

TEMA 1: Técnicas para Optimizar los Cachés: pág 15

struct {char a; char b; char c; } s[8192];

for (i=0; i<8192 ; i++) s[i].a= s[i].b+ s[i].c;

o Para matrices grandes trabajar por bloques de tamaño menor o igual que caché:

ejemplos: filtros de imágenes, producto de matrices

float A[N][N], B[N][N], D[N][N] ;

for (jj=0; jj<N; jj+=bb)

for (kk=0; kk<N; kk+=bb)

for (i=0; i<N; i++)

for (j=jj; j<jj+bb; j++)

for (k=kk; k<kk+bb; k++)

D[i][j] = D[i][j] + A[i][k] * B[k][j];

// bb*bb es el tamaño del bloque. Sup. N es múltiplo de bb

Técnicas que reducen thit

Caché de primer nivel pequeño y simple:

Electrónica: cuanto más pequeño: más rápido.

Crítico: la frecuencia del procesador suele venir determinada por thit. Un aumento de

thit puede afectar a toda la CPU.

Aunque tenga más MR, un caché L1 menor y más simple (mapeado directo) posibilita

más frecuencia de la CPU: eléctricamente 20-50% más rápidos que el de dos vías.

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 16

El tamaño de L1 no ha crecido en los últimos 10 años (en Pentium 4 ha disminuido):

caché 8KB puede ser (eléctricamente) 30% más rápido que uno de 16 KB y 60% más

que de 32KB.

Para L2 no es tan crítico, pero interesa L2 dentro del chip.

Acceso al caché segmentado o encadenado:

Barrera del acceso a memoria: acceso a cachés cada vez más ciclos CPU.

Permitir ejecutar accesos en cadena. Varios accesos simultáneos

Acceso al caché de instrucciones (tb. se hace para datos)

T1

Resto de la instrucción (varios ciclos)

T2

T3

T1

T2

T3

T1

T2

Resto de la instrucción (varios ciclos)

T3

Resto de la instrucción (varios ciclos)

Notar que la latencia es la misma o mayor (se incrementa el AB)

Dpto de Arquitectura y Tecnología de Computadores. ASP1.

TEMA 1: Técnicas para Optimizar los Cachés: pág 17

![COMPONENTES_DE_LA_CPU_OSWALDO_IBARRA[1]](http://s2.studylib.es/store/data/000896384_1-834ea5f7823f030c85a9c1dfdecaf524-300x300.png)