La figura muestra la estructura de un computador con una CPU de

Anuncio

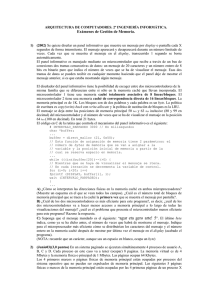

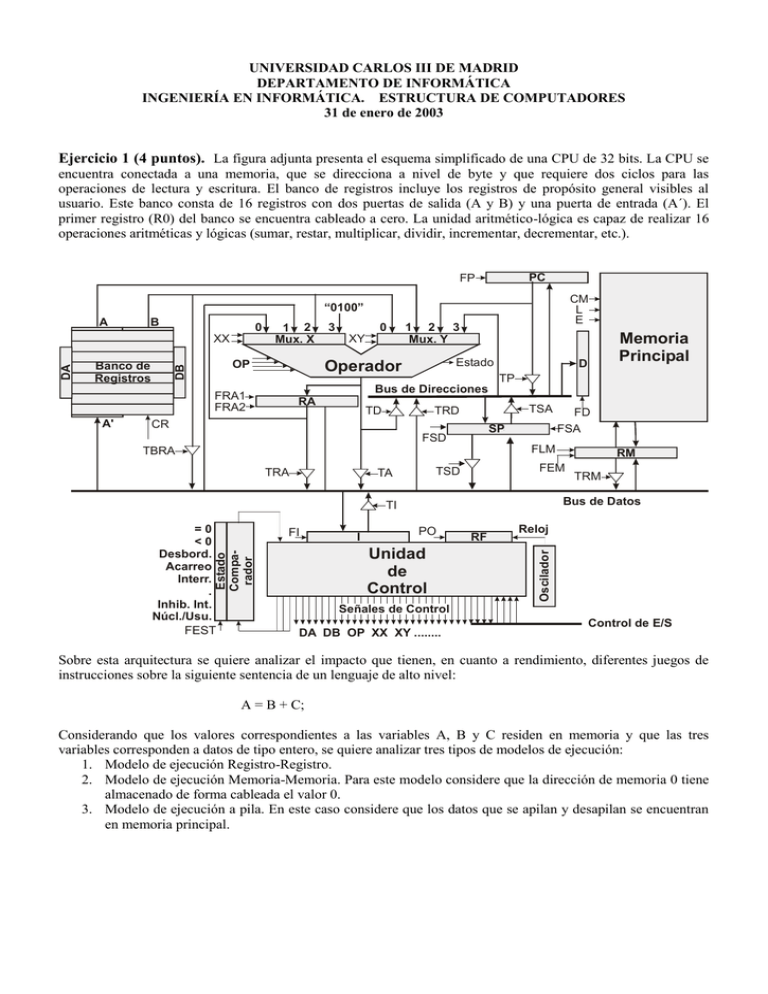

UNIVERSIDAD CARLOS III DE MADRID DEPARTAMENTO DE INFORMÁTICA INGENIERÍA EN INFORMÁTICA. ESTRUCTURA DE COMPUTADORES 31 de enero de 2003 Ejercicio 1 (4 puntos). La figura adjunta presenta el esquema simplificado de una CPU de 32 bits. La CPU se encuentra conectada a una memoria, que se direcciona a nivel de byte y que requiere dos ciclos para las operaciones de lectura y escritura. El banco de registros incluye los registros de propósito general visibles al usuario. Este banco consta de 16 registros con dos puertas de salida (A y B) y una puerta de entrada (A´). El primer registro (R0) del banco se encuentra cableado a cero. La unidad aritmético-lógica es capaz de realizar 16 operaciones aritméticas y lógicas (sumar, restar, multiplicar, dividir, incrementar, decrementar, etc.). PC FP CM L E “0100” A B 0 Banco de Registros 1 2 Mux. X XY 1 2 3 Mux. Y Estado Memoria Principal D TP Bus de Direcciones FRA1 FRA2 A' 0 3 Operador OP DB DA XX RA TD TSA TRD CR SP FSD FD FSA FLM TBRA TRA TSD TA I PO Estado Comparador Unidad de Control RF Reloj Oscilador FI TRM Bus de Datos TI =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST RM FEM Señales de Control DA DB OP XX XY ........ Control de E/S Sobre esta arquitectura se quiere analizar el impacto que tienen, en cuanto a rendimiento, diferentes juegos de instrucciones sobre la siguiente sentencia de un lenguaje de alto nivel: A = B + C; Considerando que los valores correspondientes a las variables A, B y C residen en memoria y que las tres variables corresponden a datos de tipo entero, se quiere analizar tres tipos de modelos de ejecución: 1. Modelo de ejecución Registro-Registro. 2. Modelo de ejecución Memoria-Memoria. Para este modelo considere que la dirección de memoria 0 tiene almacenado de forma cableada el valor 0. 3. Modelo de ejecución a pila. En este caso considere que los datos que se apilan y desapilan se encuentran en memoria principal. Se pide: a) Microprograme a nivel de operaciones elementales el ciclo de fetch. Indique además, para cada operación elemental, las señales de control necesarias. b) Para cada uno de los modelos de ejecución anterior indique las instrucciones en ensamblador que son necesarias para ejecutar la sentencia de alto nivel A = B + C; c) Para cada una de las instrucciones en ensamblador obtenidas anteriormente, indique el formato que debería tener la correspondiente instrucción de máquina. Considere que en todos los modelos se desea disponer de 130 instrucciones de máquina. d) Determine cuál de los modelos de ejecución anterior permite ejecutar en un menor número de ciclos la sentencia A = B + C; Ejercicio 2 (3 puntos). Escriba en ensamblador del MIPS R2000 una función que realice la factorización de un número entero. Esta función recibe en $a0 el número entero a factorizar e imprime por pantalla todos los factores primos del número pasado como argumento. La factorización de un número supone encontrar la descomposición del mismo como producto de números primos. Por ejemplo: Factorizar(15) = 5 * 3 * 1 Factorizar(30) = 5 * 3 * 2 * 1 Factorizar(72) = 3 * 3 * 2 * 2 * 2 * 1 Ejercicio 3 (3 puntos). Un computador de 32 bits que se direcciona a nivel de byte posee una memoria caché de datos de 4 KB y una caché de instrucciones de 2 KB. Ambas cachés utilizan una función de correspondencia directa y su tamaño de bloque es de 4 palabras. El tiempo de acceso al sistema de memoria en caso de acierto es de 20 ns. En caso de fallo, el tiempo de acceso (incluyendo la actualización de la caché) es de 100 ns. La memoria caché utiliza una política de actualización diferida (post-escritura, write-back o copy-back). El tiempo para escribir un bloque de memoria caché a memoria principal es también de 100 ns. En el computador descrito se ejecuta el siguiente fragmento de código, que se almacena a partir de la dirección de memoria 0x00F00000: bucle: move $t0, $zero lw $t1, x($t0) sw $t1, y($t0) addi $t0, $t0, 4 bne $t0, 12, bucle fin: Donde x se corresponde con la dirección de memoria 0x70000000 e y se corresponde con la dirección de memoria 0x00000400. Todas las instrucciones usadas en el fragmento de código ocupan una palabra cada una. Se pide: a) Determine cuál es le tiempo medio de acceso a memoria para el programa descrito. b) Si se sustituye la memoria caché de datos, por otra que utilice una función de correspondencia asociativa por conjuntos de 4 entradas (4 vías) que utiliza una política de sustitución FIFO ¿cuál será el tiempo?