Soluciones Examen Diciembre 02

Anuncio

ARQUITECTURA DE COMPUTADORES

SEGUNDO INGENIERIA INFORMATICA. DICIEMBRE 2003.

P1. (2,5 puntos)

P2. (3,0 puntos) Se dispone del siguiente código en lenguaje ensamblador perteneciente a un

determinado microcontrolador (procesador) que se está ejecutando en memoria principal:

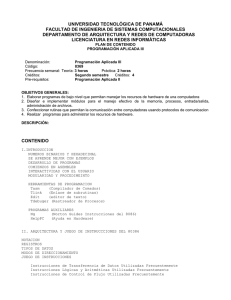

TIPO (LECTURA/ESCRITURA) –

DIRECCIÓN (hexadecimal) –

TIPO (INSTRUCCIONES/DATOS) –

Nº BYTES ACCEDIDOS

ENSAMBLADOR

COD-INST OP-destino, OPfuente1, (OP-fuente2)

L 0x0000 CD00 I 02

L 0x0000 DA00 D 02

Bucle: LW R3, 0(R5)

lee de memoria en R3 el

contenido apuntado por

R5

(que

contiene

la

dirección 0xDA00)

L 0x0000 CD02 I 02

L 0x0000 DA04 D 02

LW R4, 4(R5)

L 0x0000 CD04 I 02

ADD R7, R7, R3

L 0x0000 CD06 I 02

ADD R8, R8, R4

L 0x0000 CD08 I 02

ADD R10, R7, R8

L 0x0000 CD0A I 02

E 0x0000 DA00 D 02

L 0x0000 CD0C I 02

SW

lee de memoria en R4 el

contenido apuntado por

R5+4 (dirección 0xDA04)

suma en R7 el contenido

de R7 más el de R3

suma en R8 el contenido

de R8 más el de R4

suma

en

R10

el

contenido de R7 más el

de R8

escribe en memoria el

contenido de R6

Compara si R10 es igual

a R11 salta a bucle

0(R5), R6

BEQ Bucle, R10, R11

SIGNIFICADO

Los registros generales (R1, R2, ... R16) almacenan palabras (datos) de 16 bits. Las instrucciones (LW,

ADD, BEQ y SW) también tienen todas una longitud de 2 bytes. Además el microcontrolador donde se

ejecuta este código tiene una memoria caché unificada de correspondencia directa. La política de

escritura es copy-back y write-allocate. Tiene una capacidad de 32 bytes y líneas de una sola palabra. Se

pide:

A) Indique qué ocurre al ejecutar el bucle. Calcule el porcentaje de fallos (MR). Explique o justifique su

respuesta.

B) El bucle itera 100 veces (N =100). Suponiendo que un acierto de caché supone 2 ms y en caso de fallo

se necesitan 20 ms para traer el bloque necesario de memoria principal, calcule el tiempo total de

ejecución de su programa.

C) Rediseñe la memoria caché de forma que el tiempo de cómputo sea el mínimo posible teniendo en

cuenta que el tamaño/capacidad de la memoria caché no se puede alterar. Justifique su elección.

D) Ahora se dispone de un sistema paginado con 1M byte de memoria principal y marcos físicos de

página de 1K byte. Calcule cuántos y cuáles marcos de páginas de memoria principal son usados por el

proceso/programa que implementa el bucle.

1

P3. (2,0 puntos) Se dispone de un teclado y una pantalla con las siguientes características:

El teclado y la pantalla tienen un bus de datos capaces de enviar o recibir un carácter. La señales “Data

Ready” sirven para comunicar desde o hacia el dispositivo que el dato (carácter) está listo para ser

transmitido. Las señales ACK sirven para comunicar que el dato ha sido correctamente transmitido o

recibido. En el caso de la pantalla, la señal Backspace sirve para retroceder y borrar el último carácter de

la pantalla y la señal space para introducir un espacio en blanco.

Se pide: Diseñar un subsistema de E/S con estos dos dispositivos externos basado en un microprocesador

i8086 de forma que se pueda hacer un programa de usuario que escribe en pantalla el carácter que se

recibe por teclado. Para ello:

- Diseñar el circuito que forman los dispositivos externos con el procesador.

- Programar las rutinas necesarias para realizar el proceso.

IMPORTANTE: utilizar notación hexadecimal (0x ...) a la hora de programar las rutinas. El carácter

backspace tiene el código ASCII 0x08 y carácter space el código 0x20. El resto de datos numéricos

relativos por ejemplo a direcciones de E/S o vectores de interrupciones los puede tomar según su

conveniencia.

2

RESPUESTAS EXAMEN AC CURSO 2002-2003. DICIEMBRE

P2. A) Se trabaja con bloques de 1 palabra = 21 bytes por lo que se necesita 1 bit en el

campo desplazamiento dentro de una dirección física interpretada por una memoria

caché. Se dice que la memoria caché ocupa 32 bytes = 25 bytes. La caché es de

correspondencia directa con 25 /21 líneas = 24 líneas por lo que tendrá un campo índice

que ocupe 4 bits.

Una dirección física de memoria principal ocupa 16 bits, ya que esa es el tamaño de la

palabra del procesador (palabras/datos de 16 bits), y los registros de la CPU no pueden

contener direcciones de más de 16 bits (ver ej. primera instrucción de lectura LW con

dirección DA00). Por lo tanto y si no se especifica ningún dato más del procesador, el

espacio de memoria principal direccionable por el procesador tiene un tamaño de 216

bytes = 64K bytes. Si a 16 bits le restamos los 4 bits del campo índice y el bit del

desplazamiento entonces los 11 bits restantes serán los bits de etiqueta.

Así pues el esquema de direcciones físicas de caché quedará de la siguiente forma:

Dirección física caché

11

4

1

Etiqueta

Índice

offset

A continuación se analizan las referencias de datos e instrucciones que se producen así

como los bloques de la memoria caché a los que se accede y sus fallos (F) o aciertos (A)

de caché:

Instrucciones

LW R3, 0(R5)

LW R4, 4(R5)

ADD R7, R7, R3

ADD R8, R8, R4

ADD R10, R7, R8

SW 0(R5), R6

BEQ R10, R11,

bucle

Ref. Instr.

Ref. Datos

1ª

Iteración

2ª

Iteración

CD00 à 11001101000

0000 0 à línea 0

CD02 à 11001101000

0001 0 à línea 1

CD04 à 11001101000

0010 0 à línea 2

CD06 à 11001101000

0011 0 à línea 3

CD08 à 11001101000

0100 0 à línea 4

CD0A à 11001101000

0101 0 à línea 5

CD0C à 11001101000

0110 0 à línea 6

DA00 à 11011010000

0000 0à línea 0

DA04 à 11011010000

0010 0à línea 2

-

F–F

F–F

F–F

A–F

F

F

-

F

A

-

F

A

DA00 à 11011010000

0000 0à línea 0

-

F–A

A–A

F

A

Hay que tener en cuenta que primero se ha de leer la instrucción y a continuación si es

preciso acceder a el dato de memoria referenciado por la instrucción y no al revés. Es

decir, en las instrucciones LW y SW se producen dos referencias a memoria: una

primera por instrucción y otra a continuación por datos. El resto de instrucciones

simplemente producen una referencia.

Así, como se puede ver en la tabla a partir de la 2ª iteración se producen dos fallos de

conflicto entre la 1ª instrucción y la 6ª y otros dos entre la 2ª y la 3ª debido a las

referencias a datos que obligan a expulsar intercambiar bloques en las líneas 0 y 2 de la

caché. En la primera iteración se producen además de estos fallos de conflicto toda una

serie de fallos forzosos. MR => 10 accesos a memoria de los cuales 4 son fallos y el

resto aciertos a partir de la 2ª iteración => 0,4 aproximadamente.

3

B) Con estos resultados ya se puede calcular el tiempo de ejecución. Simplemente hay

que contar el número de fallos de caché que se producen en 100 iteraciones:

Fcache = Fprim.iter. + 99*Fsegun.iter. = 9 + 99*3 = 306 fallos de caché

MR = 306 fallos / 10*100 referencias a memoria = 0,306 (aproximadamente 0,3)

Tejecución = N accesos * (Thit + MR * Tfallo_cache) = 1000 * ( 2ms + 0,405*20ms) = 10100 ms

C) Como ya se apuntó en la cuestión A el principal problema del bucle a partir de la 2ª

iteración son los fa llos de conflictos. De echo, en la línea 0 de la caché se han de ubicar

dos bloques de memoria principal y en la línea 2 otros dos bloques. Como en la caché

de correspondencia directa sólo se puede ubicar un único bloque, entonces surgen los

conflictos.

Por lo tanto para solucionar este problema basta con convertir la memoria caché de

correspondencia directa en otra asociativa por conjuntos de al menos dos vías. El

esquema de direcciones en ese caso sería el siguiente:

Dirección física caché

12

3

1

Etiqueta

Índice

offset

Ahora en vez de tener 16 conjuntos de un bloque se pasa a tener 8 conjuntos de dos

bloques cada uno. Con este nueva caché ya no se producen fallos de conflictos:

Instrucciones

Ref. Instr.

Ref. Datos

CD00 à 110011010000

DA00 à 110110100000

000 0 à conjunto 0(vía 0) 000 0à conjunto 0 (vía 1)

LW R4, 4(R5)

CD02 à 110011010000

DA04 à 110110100000

001 0 à conjunto 1(vía 0) 010 0à conjunto 2 (vía 0)

ADD R7, R7, R3

CD04 à 110011010000

010 0 à conjunto 2(vía 1)

ADD R8, R8, R4

CD06 à 110011010000

011 0 à conjunto 3(vía 0)

ADD R10, R7, R8 CD08 à 110011010000

100 0 à conjunto 4(vía 0)

SW 0(R5), R6

CD0A à 110011010000

DA00 à 110110100000

101 0 à conjunto 5(vía 0) 000 0à conjunto 0 (vía 1)

BEQ R10, R11,

CD0C à 110011010000

bucle

110 0 à conjunto 6(vía 0)

LW R3, 0(R5)

1ª

2ª

Iteración Iteración

F–F

A–A

F–F

A–A

F

A

F

A

F

A

F–A

A–A

F

A

El MR ahora es aproximadamente 0 ya que sólo se producen 9 fallos forzosos en la

primera iteración.

D) Primero se va a dimensionar el espacio de direcciones de la memoria virtual. Se

disponen de marcos de páginas de 1K bytes = 210 bytes à 10 bits para el campo

desplazamiento dentro de una dirección virtual. ¿cuántas páginas puede tener un

proceso? Si el procesador direccionara toda la memoria física de 1 MB = 220 bytes de

capacidad, entonces, 220 / 210 = 210 = 1024 marcos de página en memoria principal. Por

lo tanto una dirección virtual del proceso después de haber sido traducida seguirá el

siguiente esquema:

4

10

10

Dirección de marco/página física Desplazamiento en página

En el anterior caso se utiliza toda la memoria RAM (memoria principal o física)

disponible. Realmente el procesador de 16 bits en principio sólo puede direccionar 216

bytes = 64K-s o lo que es lo mismo 64 marcos de página. El resto de memoria no se

utiliza. Por lo tanto el esquema de direcciones sería el siguiente:

6

10

Dirección de marco/página física Desplazamiento en página

Ahora la cuestión radica en saber cuántas páginas ocupa el programa/proceso. Se tienen

por un lado referencias a instrucciones que van desde la dirección física CD00 hasta la

CD0C (7 instrucciones de 2 bytes). De este modo la traducción de las direcciones

virtuales a físicas después de acceder a la tabla de páginas hubiera quedado tal como

sigue:

6

10

1100 11 01 0000 0000

CD00 à

......

CD0C à

6

10

1100 11 01 0000 1100

Como se puede ver el código del programa (instrucciones) está contenido en una única

pagina. En concreto el número de marco o página física es la 1100 11(2 = 33(16 = 51(10

Para los datos se sigue un mismo razonamiento:

DA00 à

6

10

1101 10 10 0000 0000

DA04 à

6

10

1101 10 10 0000 0100

Como se puede ver en este caso se necesita cargar en memoria principal otra página

distinta a la anterior. En concreto el número marco o de página física es la 1101 10(2 =

36(16 =54(10

5

P3. Existen varias posibilidades de diseño del sistema. La primera decisión importante

es saber si se va a usar E/S programada o E/S por interrupciones ya que amb as

aproximaciones son posibles en este problema. En la solución propuesta se decide

utilizar E/S por interrupciones. Para ello se utiliza un PIC i8259 para gestionar las

interrupciones y un PPI i8255 para conectar tanto los dispositivos externos (teclado y

pantalla) al sistema. Así se forma un periférico compuesto por un controlador/módulo

de E-S (el 8255) y dos dispositivos externos que dependen de él. El esquema de

conexión y el software sería el siguiente:

/* Direcciones puestas a partir de unos espacios de direccionamiento de E/S elegidos al

azar */

#define PORTA 0x60

#define PORTB 0x61

#define PORTC 0x62

#define CONTROL 0x63

#define PORT_ 8259_0 0x20

#define PORT_ 8259_1 0x21ç

/* Las interrupciones se han conectado a IR1 e IR2. Se podrían haber conectado a otras

IR-s. Si se toma por ejemplo la base del vector de interrupciones como 0x08 entonces al

producirse la IR1 (teclado) el i8259 pondrá en el bus de datos el vector 0x08 + 0x01 =

0x09 y al producirse la IR2 (pantalla) pondrá en el bus de datos el vector de

interrupciones 0x08 + 0x02 = 0x0A */

#define BASE_INT

0x08

#define VECTOR_INT_TECLADO 0x09

#define VECTOR_INT_PANTALLA 0x0A

#define BACKSPACE 0x08

#define SPACE

0x20

6

/****************************************/

/*** RUTINA DE INICIALIZACION *********/

/****************************************/

void INICIALIZAR (void) {

disable ();

/* Configuración del 8259: inicialización + base vector interrupciones */

/* ICW1: activación por flancos, modo simple, no ICW4 */

outportb (PORT_ 8259_0, 0x10); // 0b 0001 0000

/* ICW2 : base interrupciones. */

outportb (PORT_ 8259_1, BASE _INT);

/* Configuración del 8255 : puerto A modo 1 + entrada, puerto B modo 1 +

salida */

outportb (CONTROL, 0xB4); // 0b 1011 0100

/* Activar interrupciones en puerto A */

outportb (CONTROL, 0x09); // 0b 0000 1001

/* Activar interrupciones en puerto B */

outportb (CONTROL, 0x05); // 0b 0000 0101

/* Modificación del vector de interrupciones */

setvect (VECTOR_INT_TECLADO, RUTINA_ATENCION_TECLADO);

setvect (VECTOR_INT_PANTALLA, RUTINA_ATENCION_PANTALLA);

enable ();

}

/*****************************************************/

/*** RUTINAS DE ATENCIÓN A LAS INTERRUPCIONES ***/

/****************************************************/

void interrupt RUTINA_ATENCION_TECLADO (void) {

/* Se ha recibido un carácter por teclado y hay que enviarlo a la pantalla */

char c = inportb (PORTA);

/* Se comprueba que se puede escribir en la pantalla para lo cual la señal ACK

tiene que estar en alta ya que en el modo 1 del puerto B el bit C2 corresponde a

la señal ACK# (ACK negada) */

if ((inportb (PORTC) & 0x04) != 0) {

if (c == BACKSPACE) {

/* Si el carácter es de retroceso entonces hay que activar la señal

backspace del dispositivo PANTALLA a través del bit C6*/

outportb (PORTC, inportb(PORTC) | 0x40); // 0b 0100 0000

/* A continuación se desactiva otra vez la señal. Es posible que

fuese necesario que la señal durase un cierto periodo de tiempo.

Como no se especifica nada en el enunciado, se supone que una

duración de al menos un ciclo de reloj es suficiente. */

outportb (PORTC, inportb(PORTC) & 0xBF); // 0b 1011 1111

else if (c == SPACE) {

/* Si el carácter es de espacio (blanco) entonces hay que activar

la señal space del dispositivo PANTALLA a través del bit C7 */

outportb (PORTC, inportb(PORTC) | 0x80); // 0b 1000 0000

/* A continuación se desactiva otra vez la señal */

outportb (PORTC, inportb(PORTC) & 0x7F); // 0b 0111 1111

} else

/* Otro carácter. Se manda directamente a la PANTALLA */

7

outportb (PORTB, c);

}

}

void interrupt RUTINA_ATENCION_PANTALLA (void) {

/* En principio no necesita hacer nada*/

}

NOTA: sobre esta solución y en el caso de la rutina de atención a la interrupción

llamada RUTINA_ATENCION_TECLADO, se podía haber supuesto que los caracteres

ASCII de espacio en blanco y retroceso son directamente procesables por la pantalla. En

ese caso por lo tanto no habría que activar explícitamente las señales Space y

Backspace. Esto suele ser así en muchos displays comerciales.

Como en principio este display proporciona estas dos señales, se supone que es porque

no reconoce estos caracteres como caracteres de control a través de su bus de datos S0S7.

8

![COMPONENTES_DE_LA_CPU_OSWALDO_IBARRA[1]](http://s2.studylib.es/store/data/000896384_1-834ea5f7823f030c85a9c1dfdecaf524-300x300.png)