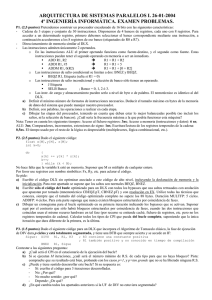

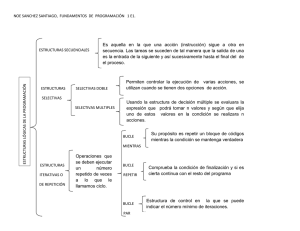

ARQUITECTURA DE SISTEMAS PARALELOS I. 29-11

Anuncio

ARQUITECTURA DE SISTEMAS PARALELOS I. 29-11-2006

4º INGENIERÍA INFORMÁTICA. TEORÍA. Tercera Convocatoria 2005-06

Apellidos

Nombre

DNI

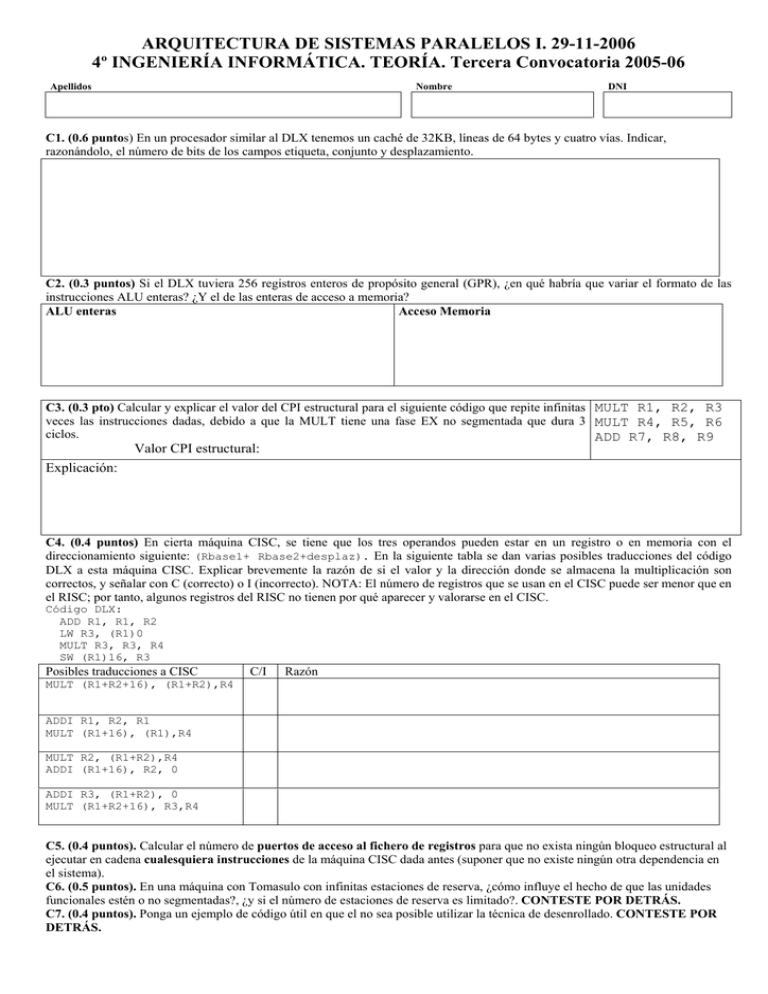

C1. (0.6 puntos) En un procesador similar al DLX tenemos un caché de 32KB, líneas de 64 bytes y cuatro vías. Indicar,

razonándolo, el número de bits de los campos etiqueta, conjunto y desplazamiento.

C2. (0.3 puntos) Si el DLX tuviera 256 registros enteros de propósito general (GPR), ¿en qué habría que variar el formato de las

instrucciones ALU enteras? ¿Y el de las enteras de acceso a memoria?

ALU enteras

Acceso Memoria

C3. (0.3 pto) Calcular y explicar el valor del CPI estructural para el siguiente código que repite infinitas MULT R1, R2, R3

veces las instrucciones dadas, debido a que la MULT tiene una fase EX no segmentada que dura 3 MULT R4, R5, R6

ciclos.

ADD R7, R8, R9

Valor CPI estructural:

Explicación:

C4. (0.4 puntos) En cierta máquina CISC, se tiene que los tres operandos pueden estar en un registro o en memoria con el

direccionamiento siguiente: (Rbase1+ Rbase2+desplaz). En la siguiente tabla se dan varias posibles traducciones del código

DLX a esta máquina CISC. Explicar brevemente la razón de si el valor y la dirección donde se almacena la multiplicación son

correctos, y señalar con C (correcto) o I (incorrecto). NOTA: El número de registros que se usan en el CISC puede ser menor que en

el RISC; por tanto, algunos registros del RISC no tienen por qué aparecer y valorarse en el CISC.

Código DLX:

ADD R1, R1, R2

LW R3, (R1)0

MULT R3, R3, R4

SW (R1)16, R3

Posibles traducciones a CISC

C/I

Razón

MULT (R1+R2+16), (R1+R2),R4

ADDI R1, R2, R1

MULT (R1+16), (R1),R4

MULT R2, (R1+R2),R4

ADDI (R1+16), R2, 0

ADDI R3, (R1+R2), 0

MULT (R1+R2+16), R3,R4

C5. (0.4 puntos). Calcular el número de puertos de acceso al fichero de registros para que no exista ningún bloqueo estructural al

ejecutar en cadena cualesquiera instrucciones de la máquina CISC dada antes (suponer que no existe ningún otra dependencia en

el sistema).

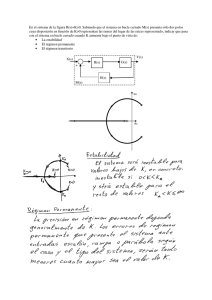

C6. (0.5 puntos). En una máquina con Tomasulo con infinitas estaciones de reserva, ¿cómo influye el hecho de que las unidades

funcionales estén o no segmentadas?, ¿y si el número de estaciones de reserva es limitado?. CONTESTE POR DETRÁS.

C7. (0.4 puntos). Ponga un ejemplo de código útil en que el no sea posible utilizar la técnica de desenrollado. CONTESTE POR

DETRÁS.

ARQUITECTURA DE SISTEMAS PARALELOS I. 29-11-2006

4º INGENIERÍA INFORMÁTICA. TEORÍA. Tercera Convocatoria 2005-06

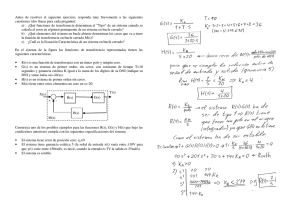

PROBLEMA 1 (2.1 puntos) Supongamos que en una máquina similar al DLX, queremos ejecutar el siguiente código:

#define N 32

float a[N][N], b[N][N], c[N][N], d[N][N]; //Suponer que el primer vector empieza en una

//dirección múltiplo del tamaño del caché

int main(void){

register int i,j;

for (i=0; j<N; i++)

for (j=0; j<N; j++){

c[i][j] = a[i][j] + b[i][j]; //el orden de lectura escritura es de derecha a izquierda

b[i][j] = c[i][j] + d[i][j];

}}

Para un caché con 64 líneas de 16 bytes cada una, y suponiendo que la política de reemplazo es LRU, calcular el miss rate para los

siguientes casos:

a) (0.7 puntos) CB-WA y WT-NWA, si el caché es de mapeado directo.

b) (0.7 puntos) Igual que antes pero suponiendo un caché de 2 vías.

c) (0.7 puntos) Igual que antes pero suponiendo un caché de 4 vías.

PROBLEMA 2. (2.2 puntos) Sea un DLX encadenado sin planificación dinámica, con todos los bypasses y con BTB. La duración

de la UF MULT es de 5 ciclos y la de DIV entera de 5 ciclos.

Considere que: toda coincidencia de fases bloquea totalmente la CPU; se permite escribir registros en el primer semiciclo de WB y

leer en el segundo de ID. Siempre se acierta en los accesos a los cachés de datos e instrucciones.

unsigned char datos[32][32]; //se supone que esta matriz está inicializada con valores

int i,j;

for (i=0;i<1024;i++)

for (j=0;j<3;j++) datos[4][i] = datos[4][i] * datos[j][i] / 4 ;

Dado el código anterior, se pide:

a) Traducir sin optimizar a ensamblador DLX, utilizando dos bucles anidados e incluyendo la cabecera para inicializar los

registros. Puede utilizar instrucciones de desplazamiento lógico o artimético. SRLI, SLLI, SRL, SLL. SRAI, SLAI, SRA, SLA.

(S=Shift ; R/L=Rigth/Left; L/A=Logical/arithmetical)

b) Reordenar el código anterior para optimizarlo sin cambiar el número de instrucciones y dibujar el cronograma desde la

primera instrucción del código, hasta la primera instrucción (inclusive) de la segunda iteración del bucle interno (es decir,

cuando i=0, j=1). Indicar claramente el tipo (datos, control, etc.) y causa de cada bloqueo y todos los bypasses que se activan.

Para este apartado suponer que la BTB siempre acierta, y que las variables i,j, no se van a usar después del bucle.

c) Para el bucle entero, decidir y justificar razonadamente cuál sería la BTB más simple (es decir, número de bits de historia y de

correlación y estado inicial de la máquina) que maximizara el porcentaje de acierto de predicción. Por BTB simple se entiende

la que tiene menos bits de estado por cada entrada o línea. Considere siempre números de bits de historia y correlación

inferiores a 5.

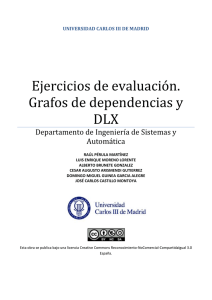

PROBLEMA 3. (2.7 puntos) Sea el siguiente código:

ADDI R4, R1, #8000

bucle_int:

LD F1, M(R1)

LD F2, N(R1)

MULTD Faux, Faux, #3

ADDD Faux, Faux, F1

SD Z(R1), Faux

ADDI R1, R1, 8

SLTI R3, R1, R4

BNEZ R3, bucle_int

Considere un DLX con todos los bypasses activados; que escribe en el primer semiciclo de WB y lee en el segundo ciclo de ID;

que resuelve los saltos en la fase ID y apuesta por NT; la duración de la etapa EX de las multiplicaciones FP de de 5 ciclos, de

las sumas FP 2 ciclos y del resto 1 ciclo.

a) Desenrolle el bucle y calcule el CPI total del bucle completo.(nota: considere los posibles bloqueos estructurales por

coincidencia de fase).

Considere una máquina encadenada con una BTB que siempre acierta y con planificación dinámica basada en el algoritmo de

Tomasulo con las siguientes características:

- La duración de UF entera es 1 ciclo, las sumas y restas FP 2 ciclos, las multiplicaciones FP 5 ciclos.

- Las instrucciones de salto se ejecutan en la unidad funcional entera

- Las UF están totalmente segmentadas.

- Existen 1 bus común para instrucciones enteras y otro para instrucciones en FP

- Cada UF dispone de 2 estaciones de reserva.

b) Dibuje el cronograma de dos iteraciones del bucle desenrollado (indicando el paso de operandos por el CDB) y calcule el CPI

total

c) ¿Cuál es la aceleración entre las máquinas del apartado a y b?

Nota: para todos los apartados CPImem = 0.