Implementación de una ALU de 8 bits en lenguaje VHDL

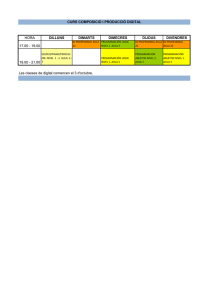

Anuncio