Taller 1

Anuncio

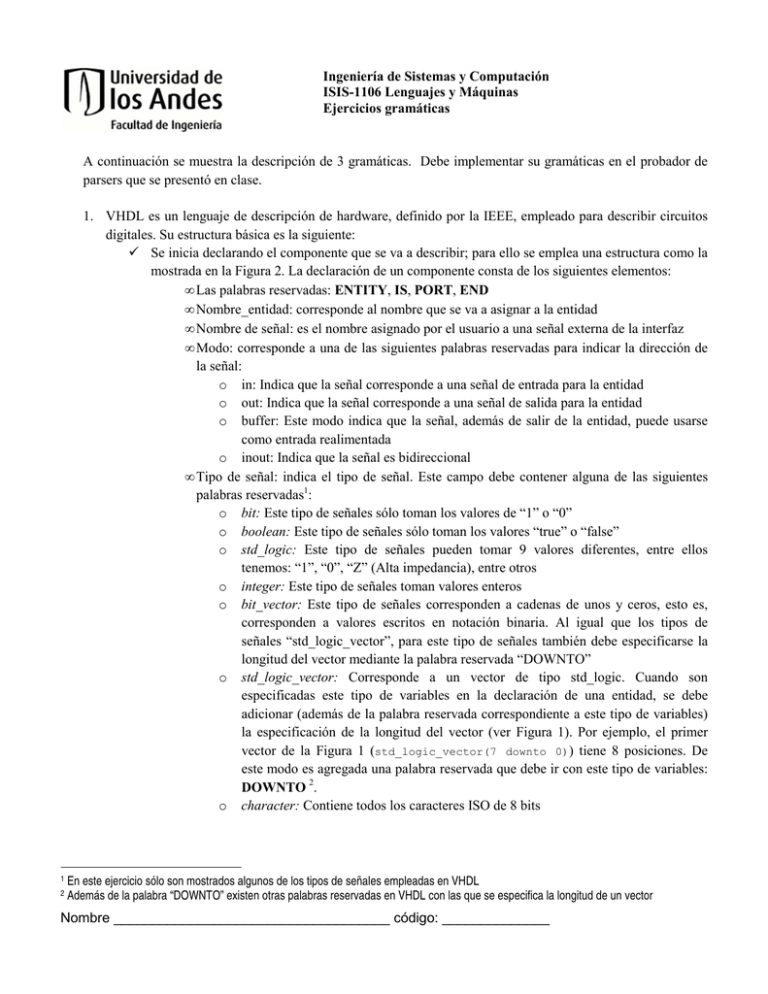

Ingeniería de Sistemas y Computación ISIS-1106 Lenguajes y Máquinas Ejercicios gramáticas A continuación se muestra la descripción de 3 gramáticas. Debe implementar su gramáticas en el probador de parsers que se presentó en clase. 1. VHDL es un lenguaje de descripción de hardware, definido por la IEEE, empleado para describir circuitos digitales. Su estructura básica es la siguiente: Se inicia declarando el componente que se va a describir; para ello se emplea una estructura como la mostrada en la Figura 2. La declaración de un componente consta de los siguientes elementos: • Las palabras reservadas: ENTITY, IS, PORT, END • Nombre_entidad: corresponde al nombre que se va a asignar a la entidad • Nombre de señal: es el nombre asignado por el usuario a una señal externa de la interfaz • Modo: corresponde a una de las siguientes palabras reservadas para indicar la dirección de la señal: o in: Indica que la señal corresponde a una señal de entrada para la entidad o out: Indica que la señal corresponde a una señal de salida para la entidad o buffer: Este modo indica que la señal, además de salir de la entidad, puede usarse como entrada realimentada o inout: Indica que la señal es bidireccional • Tipo de señal: indica el tipo de señal. Este campo debe contener alguna de las siguientes palabras reservadas1: o bit: Este tipo de señales sólo toman los valores de “1” o “0” o boolean: Este tipo de señales sólo toman los valores “true” o “false” o std_logic: Este tipo de señales pueden tomar 9 valores diferentes, entre ellos tenemos: “1”, “0”, “Z” (Alta impedancia), entre otros o integer: Este tipo de señales toman valores enteros o bit_vector: Este tipo de señales corresponden a cadenas de unos y ceros, esto es, corresponden a valores escritos en notación binaria. Al igual que los tipos de señales “std_logic_vector”, para este tipo de señales también debe especificarse la longitud del vector mediante la palabra reservada “DOWNTO” o std_logic_vector: Corresponde a un vector de tipo std_logic. Cuando son especificadas este tipo de variables en la declaración de una entidad, se debe adicionar (además de la palabra reservada correspondiente a este tipo de variables) la especificación de la longitud del vector (ver Figura 1). Por ejemplo, el primer vector de la Figura 1 (std_logic_vector(7 downto 0)) tiene 8 posiciones. De este modo es agregada una palabra reservada que debe ir con este tipo de variables: DOWNTO 2. o character: Contiene todos los caracteres ISO de 8 bits 1 2 En este ejercicio sólo son mostrados algunos de los tipos de señales empleadas en VHDL Además de la palabra “DOWNTO” existen otras palabras reservadas en VHDL con las que se especifica la longitud de un vector Nombre ____________________________________ código: ______________ Figura 1. Ejemplo de la declaración de un componente empleando el tipo de variable std_logic_vector Figura 2. Estructura para la declaración de un componente Una vez es declarado el componente se define la arquitectura de la entidad, para ello se emplea un esquema como el mostrado en la Figura 2. Este esquema se compone de las siguientes partes: • Las palabras reservadas ARCHITECTURE, IS, OF, BEGIN, END • Nombre_arquitectura: Corresponde al nombre que se va a asignar a la arquitectura de la entidad • Nombre_entidad: Corresponde al nombre de la entidad cuya arquitectura va a ser definida ARCHITECTURE nombre_arquitectura OF nombre_entidad IS BEGIN --Código de la entidad END nombre_arquitectura; Figura 3. Estructura para la declaración de la arquitectura de un componente En la Figura 4 se muestra un ejemplo de un programa en VHDL de un circuito con dos entradas: a y b (observe que se pueden definir dos señales del mismo tipo en la declaración del componente); y una salida: F. La salida de este circuito es 0 sólo si las entradas son iguales (operación XOR). Observe que en VHDL los comentarios se escriben con dos guiones (--) Figura 4. Ejemplo de un componente en VHDL Defina una gramática para la declaración de un componente y su respectiva arquitectura en VHDL 2. Defina una gramática para la declaración de la arquitectura de un componente en VHDL, con base en los siguientes criterios: Para este ejercicio, únicamente se contemplarán arquitecturas sencillas (como la mostrada en la Figura 5). En la arquitectura de este ejemplo, son asignados valores fijos a las variables de salida de la entidad, sin tener en cuenta las entradas En el ejemplo de la Figura 5, la asignación de valores a cada una de las señales de salida, se hace empleando diferentes bases: la base binaria (tomada por defecto), la base octal y la base Nombre ____________________________________ código: ______________ hexadecimal. Dependiendo de la base numérica elegida, cambiará el formato en que son asignados los valores de las señales La gramática definida sólo debe verificar que los valores asignados a cada una de las variables en el cuerpo de la arquitectura, sean los adecuados de acuerdo a la base numérica elegida, sin verificar que la longitud (en bits) de los valores asignados corresponda a la que se asignó a la variable en la declaración de la entidad ENTITY Ejemplo1 IS PORT( in1, in2: in std_logic_vector(3 downto 0); out1: out std_logic_vector(15 downto 0); out2: out std_logic_vector(8 downto 0); out3: out std_logic; out4, out5: out std_logic_vector(3 downto 0) ); END Ejemplo1; ARCHITECTURE arquitectura_ejemplo1 OF ejemplo1 IS BEGIN out1 <= X"AF67"; --Base hexadecimal out2 <= O"723"; --Base octal out3 <= "0"; --Base binaria, tomada por defecto out4 <= "0000"; --Base binaria, tomada por defecto out5 <= B"0001"; --Base binaria, especificada explícitamente END ejemplo1; Figura 5. Ejemplo de declaración de una arquitectura sencilla en VHDL 3. Para incluir librerías en VHDL se emplean las palabras reservadas “library” y “use”, en la Figura 6 se muestra la estructura general para la declaración de librerías en VHDL y en la Figura 7 se muestra un ejemplo. A través de la palabra “library” se especifica el nombre de la librería, mientras que “use” especifica el paquete de la librería que se pretende utilizar, después de la declaración del nombre de la librería pueden ser añadidos tantos paquetes como los existentes en la librería. Observe que, para este ejercicio, después de especificar el nombre del paquete se emplea la palabra reservada “ALL”, para hacer visibles todos los elementos del paquete. Defina una gramática que permita la declaración de librerías en VHDL de acuerdo al esquema explicado. Nombre ____________________________________ código: ______________ LIBRARY nombre_libreria1; USE nombre_libreria1.nombre_paquete1.ALL; USE nombre_libreria1.nombre_paquete2.ALL; ⋮ USE nombre_libreria1.nombre_paqueteN.ALL; LIBRARY nombre_libreria2; USE nombre_libreria2.nombre_paquete1.ALL; ⋮ USE nombre_libreria2.nombre_paqueteN.ALL; Figura 6. Declaración de librerías en VHDL LIBRARY mis_componentes; USE mis_componentes.logic.ALL; LIBRARY ieee; USE ieee.std_logic_1164.ALL; Figura 7. Ejemplo de declaración de librerías en VHDL Nombre ____________________________________ código: ______________