Reválida de Septiembre - Universitat de les Illes Balears

Anuncio

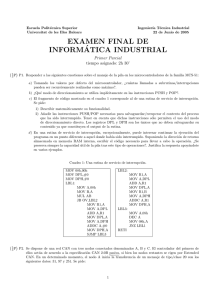

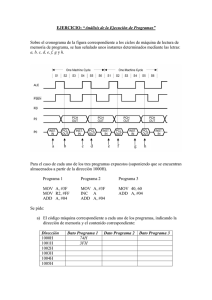

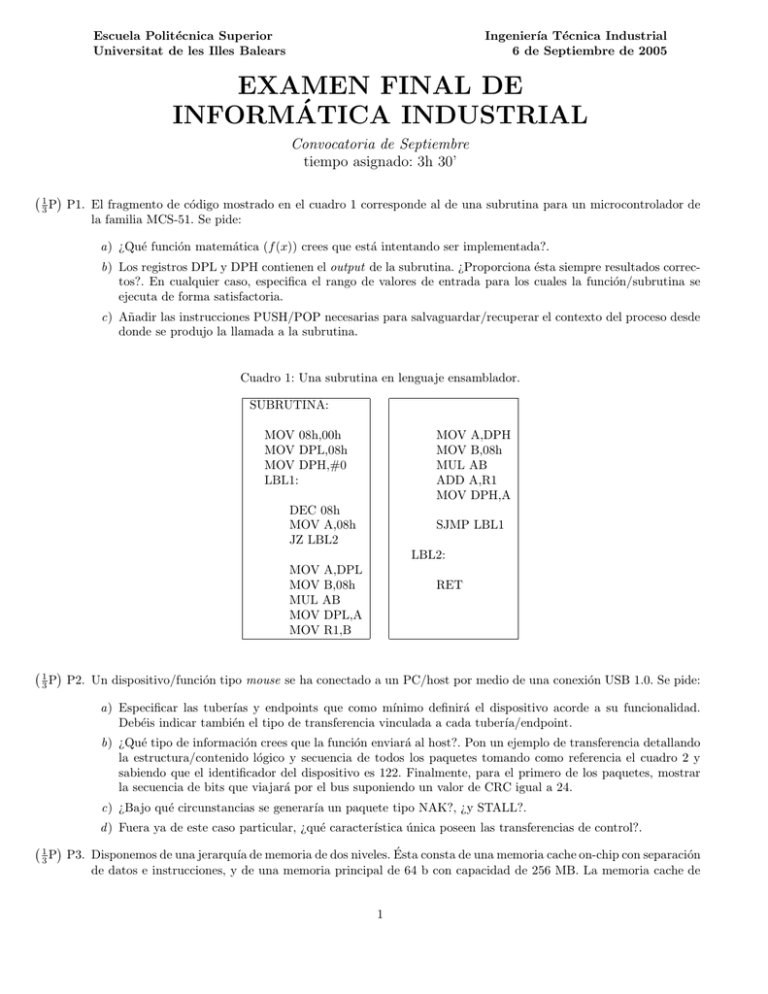

Escuela Politécnica Superior Universitat de les Illes Balears Ingenierı́a Técnica Industrial 6 de Septiembre de 2005 EXAMEN FINAL DE INFORMÁTICA INDUSTRIAL Convocatoria de Septiembre tiempo asignado: 3h 30’ 1 3P P1. El fragmento de código mostrado en el cuadro 1 corresponde al de una subrutina para un microcontrolador de la familia MCS-51. Se pide: a) ¿Qué función matemática (f (x)) crees que está intentando ser implementada?. b) Los registros DPL y DPH contienen el output de la subrutina. ¿Proporciona ésta siempre resultados correctos?. En cualquier caso, especifica el rango de valores de entrada para los cuales la función/subrutina se ejecuta de forma satisfactoria. c) Añadir las instrucciones PUSH/POP necesarias para salvaguardar/recuperar el contexto del proceso desde donde se produjo la llamada a la subrutina. Cuadro 1: Una subrutina en lenguaje ensamblador. SUBRUTINA: MOV 08h,00h MOV DPL,08h MOV DPH,#0 LBL1: MOV A,DPH MOV B,08h MUL AB ADD A,R1 MOV DPH,A DEC 08h MOV A,08h JZ LBL2 SJMP LBL1 LBL2: MOV A,DPL MOV B,08h MUL AB MOV DPL,A MOV R1,B 1 3P RET P2. Un dispositivo/función tipo mouse se ha conectado a un PC/host por medio de una conexión USB 1.0. Se pide: a) Especificar las tuberı́as y endpoints que como mı́nimo definirá el dispositivo acorde a su funcionalidad. Debéis indicar también el tipo de transferencia vinculada a cada tuberı́a/endpoint. b) ¿Qué tipo de información crees que la función enviará al host?. Pon un ejemplo de transferencia detallando la estructura/contenido lógico y secuencia de todos los paquetes tomando como referencia el cuadro 2 y sabiendo que el identificador del dispositivo es 122. Finalmente, para el primero de los paquetes, mostrar la secuencia de bits que viajará por el bus suponiendo un valor de CRC igual a 24. c) ¿Bajo qué circunstancias se generarı́a un paquete tipo NAK?, ¿y STALL?. d ) Fuera ya de este caso particular, ¿qué caracterı́stica única poseen las transferencias de control?. 1 3P P3. Disponemos de una jerarquı́a de memoria de dos niveles. Ésta consta de una memoria cache on-chip con separación de datos e instrucciones, y de una memoria principal de 64 b con capacidad de 256 MB. La memoria cache de 1 Cuadro 2: Listado breve de identificadores de paquetes junto con su correspondiente valor numérico. Tipo PID SETUP IN OUT DATA0 Valor 13 9 1 3 Tipo PID DATA1 ACK NAK STALL Valor 11 2 10 14 datos se caracteriza por una función de correspondencia directa, bloques de 4 palabras ası́ como por un espacio de almacenamiento de 512 B. La memoria cache de instrucciones, por su parte, teniendo una capacidad de 1 Kb utiliza un enfoque asociativo por conjuntos de 4 vı́as con bloques de 2 palabras y polı́tica de sustitución pseudo-LRU. Se pide: a) Esquematizar detalladamente la estructura de las caches. ¿Cómo determinan que un determinado dato/instrucción se encuentra o no en la cache?. b) Suponer que tanto las instrucciones como los datos necesarios para ejecutar un determinado programa se encuentran almacenados en memoria principal, concretamente entre las direcciones 0000000 H y 0000145 H (de 0000000 H − 000012FH datos y de 0000130 H − 0000145 H instrucciones). Cada instrucción requiere la lectura de 0, 1 o 2 datos. Por simplicidad, supondremos que todas las instrucciones pueden ser codificadas con 64 b. Indicar qué accesos son aciertos y cuáles son fallos, ası́ como el tipo de fallo, junto con el contenido parcial y final de ambas caches para el flujo de ejecución [0000131 H , 0000137 H , 0000138 H , 0000139 H , 000013FH , 0000140 H , 0000133 H , 0000134 H , 000013CH , 0000141 H , 0000145 H y 0000130 H ]. Debéis también especificar el estado de los bits vinculados al algoritmo de sustitución utilizado. c) Responder razonadamente a las siguientes cuestiones acerca de las caches tipo I+D: 1) ¿Qué operación (R/W), si alguna, crees que podrı́a ser prescindible para una y otra cache?. 2) ¿Puede un dato ser ubicado en la cache de instrucciones?, ¿y una instrucción en la cache de datos?. 3) ¿Está garantizada la coherencia entre ambas caches?. En caso negativo, describe una posible situación en donde dicha coherencia no se mantenga. Cuadro 3: Volcado parcial de memoria principal. Dirección 0000130 H 0000131 H 0000132 H 0000133 H 0000134 H 0000135 H 0000136 H 0000137 H 0000138 H 0000139 H 000013AH Instrucción I 0000000 H , 000004FH I I 0000005 H , 000002DH I 000000CH , 000004DH I 0000043 H , 0000044 H I I 0000007 H I 0000009 H ,000000AH I 0000011 H I 0000025 H I Dirección 000013BH 000013CH 000013DH 000013EH 000013FH 0000140 H 0000141 H 0000142 H 0000143 H 0000144 H 0000145 H 2 Instrucción I 0000002 H , 0000005 H I 0000004 H , 0000005 H I I 0000013 H I 0000026 H ,0000002 H I 0000007 H I I 00000F EH , 000003AH I 0000101 H I 000006BH , 000006CH I 000000EH , 0000018 H