C13_Memoria

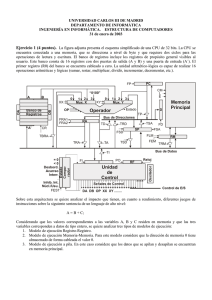

Anuncio

Memoria 1 Memoria Organización de memorias estáticas. 2 Memoria En memoria físicas con bus de datos sea bidireccional. 3 Memoria Decodificación en dos niveles. 4 Memoria Caché Necesidad de cantidades ilimitadas de memoria rápida. Crear la ilusión de una gran memoria a la que podamos acceder tan rápidamente como a una memoria muy pequeña. 5 Memoria Caché Principio de localidad Los programas acceden a una parte relativamente pequeña de su espacio de direcciones en cualquier instante de tiempo. Dos tipos de localidad: Localidad Temporal Localidad Espacial 6 Memoria Caché Principio de localidad Localidad Si un elemento es referenciado, volverá a ser referenciado pronto. Localidad Temporal (localidad en el tiempo) Espacial (localidad en el espacio) Si un elemento es referenciado los elementos cuyas direcciones están próximas tenderán a ser referenciados pronto. 7 Memoria Caché Principio de localidad En los programas la localidad surge de estructuras sencillas y naturales. Por ejemplo: Bucles localidad temporal Instrucciones que se acceden en forma secuencial localidad espacial Acceso a los datos, elementos de un arreglo. 8 Memoria Caché Jerarquía de Memoria. Consta de múltiples niveles de memoria con diferentes velocidades y tamaños. Memorias rápidas son más caras y pequeñas. La memoria principal se implementa a partir de memorias más lentas. Los niveles más próximos a la CPU (cachés) utilizan memorias más pequeñas y rápidas. 9 Memoria Caché Jerarquía de Memoria. Debido a las diferencias de costo y tiempo de acceso, es ventajoso construir la memoria como una jerarquía de niveles. La memoria más rápida cerca del procesador y la más lenta debajo de las más rápida. ilusión de una memoria tan grande como la mayor, pero con tiempo de acceso igual a la memoria más rápida. 10 Memoria Caché Jerarquía de Memoria. CPU Estructura Básica Memoria Más rápida Más pequeña Mayor costo Memoria Memoria Más lenta Más Grande Menor costo 11 Memoria Caché Jerarquía de Memoria. Una jerarquía de memoria puede estar formada múltiples niveles, pero los datos e copian cada vez solamente entre dos niveles adyacentes. La unidad mínima de información se denomina bloque, se transfiere un bloque completo cuando se copia algo entre niveles. 12 Memoria Caché Cache de mapeo directo. (Tamaño de bloque igual a uno) Cada palabra puede estar exactamente en una posición de la caché. Se asigna la posición de la caché en base a la dirección que tiene la palabra en memoria. Cada posición de la memoria le corresponde exactamente una posición en la caché. 13 Memoria Caché Cache de mapeo directo. (Tamaño de bloque igual a uno) Para saber si el dato de la caché corresponde a la palabra solicitada, se añade un conjunto de etiquetas a la caché. Para reconocer si un bloque de caché no tiene información válida, es necesario añadir un bit de validez. 14 Memoria Caché Cache de mapeo directo. 15 Memoria Caché Cache de mapeo directo. (Tamaño de bloque igual a una potencia de dos) Para aprovechar la localidad espacial el bloque de la cache contiene varias palabras adyacentes(una potencia de dos). Los bits dedicados a la administración de la cache(válido, marca) disminuyen al aumentar el tamaño del bloque. 16 Memoria Caché Cache de mapeo directo. 17 Memoria Caché Caché directa y con bloque de una palabra Aciertos y fallos son simples Caché con un tamaño de bloque mayor de una palabra. Hace disminuir la taza de fallos. Mejora la eficiencia de la caché. Reduce cantidad de memoria para las etiquetas. 18 Memoria Caché Tratamiento de fallos La unidad de control debe detectar los fallos Procesarlos y buscar el dato en memoria. Fallos de una instrucción en un camino de datos multiciclo o segmentado. Pasos que se realizan en un fallo de instrucción de la caché: 19 Memoria Caché Tratamiento de fallos 1. Calcular valor de PC-4 Indicar a memoria principal que realice una lectura y esperar que la memoria complete su acceso. Escribir en la entrada de la caché 2. 3. 1. Dato procedente de memoria en la porción del dato de entrada. Escribir bits superiores de dirección en el campo etiqueta. Bit de validez a 1. Reiniciar la ejecución d la instrucción 20 Memoria Caché Tratamiento de fallos El procesamiento de un fallo genera una detención. Incrementar el tamaño del bloque mejora el rendimiento. La tasa e fallos cae cuando aumentamos el tamaño del bloque. La tasa de fallos puede aumentar si el tamaño del bloque se hace muy grande comparado con el tamaño de la caché. 21 Memoria Caché Caché asociativa. En una caché asociativa por conjuntos hay un número fijo de posiciones (mínima dos) donde puede ubicarse cada bloque. Una caché asociativa por conjuntos con n posiciones para un bloque se denomina una caché asociativa por conjuntos de n vías. 22 Memoria Caché Caché asociativa. Una caché asociativa por conjuntos de n vías consta de una serie de conjuntos, cada uno de los cuales consta de n bloques. Cada bloque de la memoria se corresponde a un único conjunto en la caché dada por el campo índice, y un bloque puede ser sustituido en cualquier elemento de ese conjunto. 23 Memoria Caché Caché asociativa. En una caché asociativa por conjuntos, el conjunto que contiene un bloque está dado por: (Número de bloque) módulo (número de conjuntos en la caché) 24 Memoria Caché Caché asociativa. Para encontrar un bloque Tres partes de una dirección en una caché asociativa por conjuntos o correspondencia directa. Etiqueta Índice Desplazamiento bloque 25 Memoria Caché Caché asociativa. Cada bloque de la caché lleva una etiqueta que indica la dirección del bloque. La etiqueta de cada bloque de la caché que puede contener la información deseada es comprobada para ver si corresponde a la dirección del bloque de la CPU. 26 Memoria Caché Caché asociativa. 27 Memoria Caché Caché asociativa Caché asociativa por conjuntos de cuatro vías se requiere cuatro comparadores y un multiplexor. 28 Memoria Caché Rendimiento caché Tiempo de CPU = (ciclos de reloj de ejecución CPU + ciclos de reloj de detención memoria) x Duración ciclo de reloj Ciclo de reloj de detención-memoria = ciclos de detención de lectura + ciclo de detención de escritura 29 Memoria Caché Rendimiento caché Ciclos de detención de lectura = (lecturas/programa) x (tasa de fallos de lectura) x (penalización de fallos de lectura) Ciclos de detención de escritura = (Escrituras/Programa) x ( tasa de fallos de escritura) x ( penalización fallos de escritura) + detenciones del buffer de escritura 30 Memoria Caché Rendimiento caché Si se considera que penalización por fallos de escritura y lectura son las mismas y detenciones del buffer son despreciables. 31 Memoria Caché Rendimiento caché Ciclos de reloj detención-memoria = (acceso memoria/programa) x (tasa de fallos) x (penalización de fallos) Ciclos de reloj detención-memoria = (instrucciones/programa) x (fallos/instrucciones) x (penalización fallos) 32 Memoria Virtual La memoria principal actúa como una cache para el almacenamiento secundario en discos magnéticos. Se desea disponer de un ambiente eficiente y seguro para compartir la memoria entre diversos programas y disponer de una memoria mayor que la física para la ejecución de programas y procesamiento de los datos. 33 Memoria Virtual Esto puede lograrse ya que si se tienen varios programas en ejecución, éstos sólo usan (en un cierto intervalo de tiempo) una pequeña parte de la memoria que requieren, a pesar de que la suma de los requerimientos totales de memoria, de todos ellos, puedan exceder la memoria física disponible. El sistema operativo debe permitir a los programas compartir la memoria y garantizar que cada programa no invada el espacio que ocupan los otros. 34 Memoria Virtual Además las direcciones físicas que serán asignadas a los segmentos activos de los programas pueden ir cambiando en el tiempo; para permitir esta forma de emplear la memoria, cada programa, al ser compilado, emplea un espacio propio de direcciones. La memoria virtual es responsable de traducir las direcciones del programa a direcciones físicas. 35 Memoria Virtual Permite que el espacio de direcciones del programa sea mayor que el espacio de direcciones físico. Se puede considerar que el programa compilado reside en disco, y que sólo parte de esas direcciones del programa están mapeadas en direcciones físicas. Por esta razón un programa podría ser tan grande como el espacio en disco que se le permita ocupar (lo cual podría ser mucho mayor que la memoria física). Esta "ilusión" de una memoria, prácticamente ilimitada, la provee el sistema de memoria virtual. 36 Memoria Virtual La organización de memoria virtual y memoria cache es similar. Pero, por razones históricas se emplea el concepto de página en lugar de bloque. La dirección de las instrucciones y datos de un programa se denominan direcciones virtuales, las cuales son traducidas a direcciones físicas. 37 Memoria Virtual Se requiere un hardware dedicado y segmentos del sistema operativo para efectuar eficientemente el mapeo de páginas virtuales a páginas físicas. Para esto una dirección está dividida en campos: el número de página y la posición dentro de la página. El ancho del campo para el offset dentro de la página define el tamaño de ésta, y toma el mismo valor para la dirección virtual y física. Obviamente los bits dedicados al número de página en una dirección virtual son mayores que los de las direcciones físicas. 38 Memoria Virtual Tabla de páginas Para lograr la completa asociatividad se emplea una Tabla de Páginas residente en memoria, que tiene: como índice el número de página virtual y como contenido el número de página física, además de un bit para indicar si la página está o no presente en la memoria. 39 Memoria Virtual Tabla de páginas 40 Memoria Virtual Tabla de páginas Cada programa tiene su propia tabla de páginas, y se dispone un registro en el procesador para apuntar a la tabla de página activa. Un programa en ejecución, se denomina proceso, y requiere una tabla de página y el valor de los registros (adicionalmente información sobre prioridad de ejecución, estado del proceso, archivos que emplea, etc.), el sistema operativo es responsable de asignar memoria física y actualizar la tablas de página de tal modo que los diferentes procesos funcionen con sus propios espacios (es decir los programas sólo pueden leer y escribir las porciones de memoria principal que tienen asignadas). 41 Memoria Virtual Tabla de páginas El sistema operativo también es responsable de ir activando, con cierta política de itineración los diferentes procesos, de tal modo que sólo uno esté activo durante cierto intervalo de tiempo, para esto basta que mantenga información del estado de los diferentes procesos. Específicamente para activar el espacio de direcciones basta actualizar el registro que apunta a la tabla de páginas del proceso. 42 Memoria Virtual Tabla de páginas En caso de producirse una falla de página, se genera excepción. El sistema operativo debe: encontrar la página en el disco y decidir dónde colocarla en la memoria principal. Para facilitar esta tarea cuando se crea un proceso se almacena en una zona del disco todas las páginas de un proceso y a la vez una estructura de datos que asocie la página virtual con la dirección física del disco donde ésta se encuentra. Esta estructura puede ser la misma tabla de páginas del proceso. 43

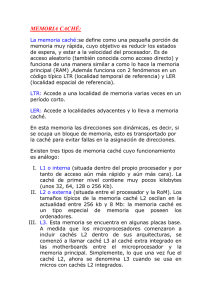

![COMPONENTES_DE_LA_CPU_OSWALDO_IBARRA[1]](http://s2.studylib.es/store/data/000896384_1-834ea5f7823f030c85a9c1dfdecaf524-300x300.png)