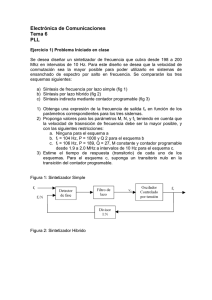

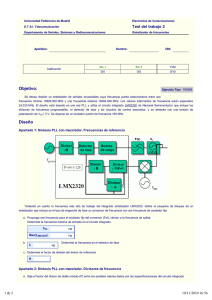

1 Introducción a los sintetizadores de frecuencia - e

Anuncio