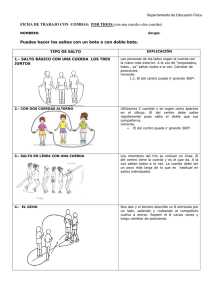

salto

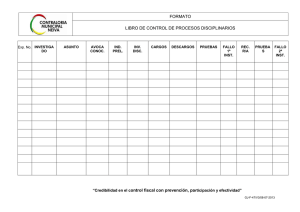

Anuncio

DEPENDENCIAS Y BLOQUEOS DE

CONTROL (Apartado 2.8)

1. Introducción.

2. Dependencias, riesgos y bloqueos de control.

3. Consideraciones de implementación.

4. Comportamiento de los saltos condicionales.

5. Implementaciones alternativas de saltos.

6. Visión de conjunto.

1.

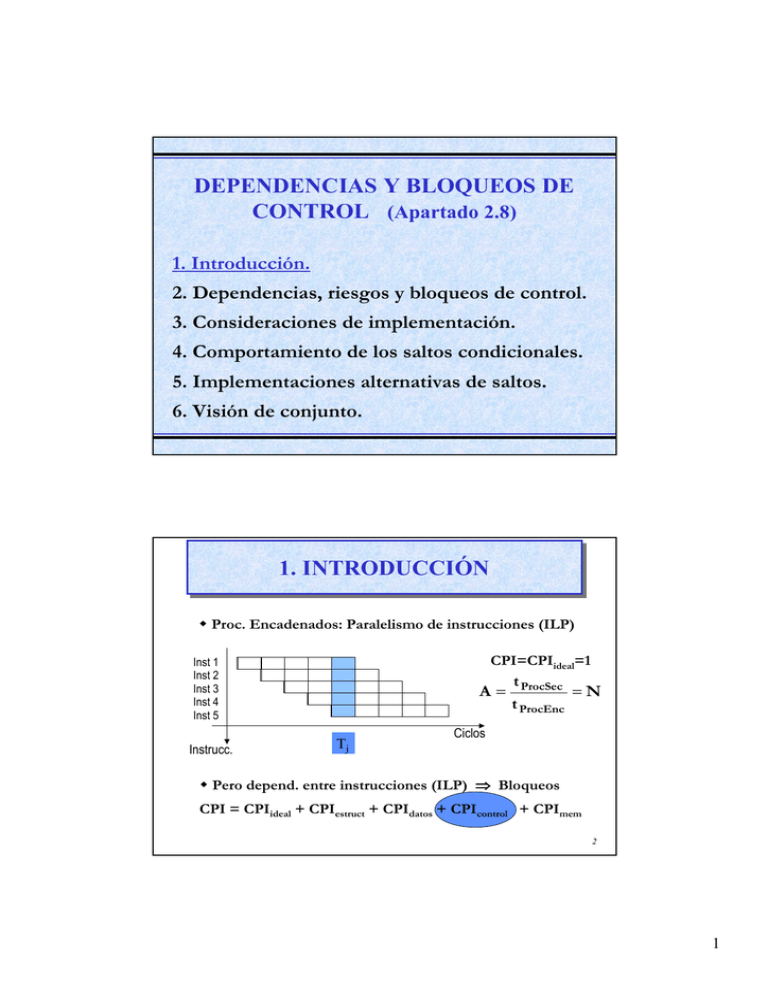

1. INTRODUCCIÓN

INTRODUCCIÓN

Proc. Encadenados: Paralelismo de instrucciones (ILP)

CPI=CPIideal=1

Inst 1

Inst 2

Inst 3

Inst 4

Inst 5

Instrucc.

A=

Tj

t ProcSec

=N

t ProcEnc

Ciclos

Pero depend. entre instrucciones (ILP) ⇒ Bloqueos

CPI = CPIideal + CPIestruct + CPIdatos + CPIcontrol + CPImem

2

1

¿Por qué instrucciones de control?

VISIÓN JERÁRQUICA. Lenguaje alto nivel (iterativo)

• Control del flujo de instrucciones (modifican el PC)

• Estruct. condic.: if-then ó if (cond) { ... } ⇒ Salto Cond.

if-then-else ó if (cond) { ... } else { ... }

EJERC.

⇒ Salto Cond. + Salto incond.

•

Ej.

if (cond)

{

…

}

⇒

; instrucciones que evalúan la condición

; (aquí es la contraria)

BEQZ ó BNEZ Rcond, etiq ;

cuerpo del ‘if ’

etiq: ; instr. tras el cuerpo

3

• Estruct. iterat.: for (… ; cond ;… ) { ... }

while (cond) { ... }

do { ... } while (cond);

EJERC.

⇒Salto cond+Salto incon.

ó Salto cond

• Saltos incond. dir. dest. fija: goto etiq

⇒Salto incond

‘CALL’ ó función (…)⇒

⇒Salto incond

(Guardar dir. retorno)

En el DLX: JAL etiq ; R31←PC+4;

• Saltos incond. dir. dest. var.: return ( … ) ⇒Salto incond

(extraer dir. retorno) DLX: JR R31

switch (var) { case: … } ⇒Salto incond

(calcular dir. dest)

4

2

Ejemplo: Sentencia do {...} while( )

n=0;

ADD R8, R0, R0

do {

Etiq:

...

...

n++;

ADDI R8, R8, 1

} while ( n<100 ) ;

SLTI R9, R8, 100

BNEZ R9, Etiq

NOTA: el bucle for( ) o while( )

análogo (nº fijo de iter.) se

puede traducir por el mismo

código ensamblador.

Bucles: saltos condicionales

hacia atrás muy frecuentes

5

Tipos de instrucciones de control

♦ Saltos RISC: sencillos, CISC: complejos

Frec. INT Frec. FP

SALTO

Formato Rango

(DLX)

(DLX)

16 bits

BEQZ/BNEZ

I

16%

8%

con signo

26 bits

J, JAL

J

1%, 1% 0.5%, 1%

con signo

JR, JALR

I

Registro

1%

1%

Muy frecuentes (1 de cada 4 a 7 instr.)

Usaremos: Fsaltos(INT) = 0.2

Fsaltos(FP) = 0.1

6

3

Definiciones y Nomenclatura

V

Cond

F

PC+4

Instr. sig.

PCdest

Instr. dest

PCdest

Instr. dest

•

•

•

•

SALTOS CONDICIONALES

Tomado/No Tomado (T/NT)

Rama Tomada/Rama No Tomada

Instr. de destino/Instr. siguientes

Tras resolver ⇒ Instr. Válidas

• Resolver salto: 1. Calcular PCdest

2. Evaluar la condición

3. Actualizar el PC

(IF buscará instr. válidas)

SALTOS INCONDICIONALES

7

Ejemplo de ejecución de instr. salto

• Resolver salto:

1. PCdest =NPC +Desplaz

(SUMADOR)

ADD R8, R0, R0

Etiq:

... ; Instr. de destino

...

ADDI R8, R8, 1

SLTI R9, R8, 100

BNEZ R9, Etiq

... ; Instr. Siguientes

Rama

Tomada

Compilador:

Desplaz = dir(salto)- dir(Etiq)- 4

Salto hacia atrás: Desplaz<0

Salto hacia delante: Desplaz>=0

2. Condición : R9≠

≠0 (Rf=0 ?)

3. Actualizar el PC: (MUX)

if (Cond) PC=PC+4 ;

else

PC= PCdest ;

Rama No ⇒ Siguiente fase IF buscará

instr válidas.

Tomada

8

4

Esquema del DLX

FASE

MEM

PCdest

Cond

PCdest

9

INDICE

INDICE

1. Introducción.

2. Dependencias, riesgos y bloqueos de control.

3. Consideraciones de implementación.

4. Comportamiento de los saltos condicionales.

5. Implementaciones alternativas de saltos.

6. Visión de conjunto.

10

5

Dependencias de control

Recordemos:

Dependencia

instr. 1

Ejec.

Secuencial

Ejec.

Encaden.

¿Qué es una

dependencia

de control? :

Uso del PC

Cond

F

Instr.

sig.

V

instr. 2

instr. 3

“Ve” todos los recursos ⇒

No depend.

Inst 1

Inst 2

Inst 3

Inst 4

Inst 5

Fichero.exe

Salto

Inst sig1

Inst sig2

Instr. Inst sig3

dest Inst sig4

Riesgo ⇒ Bloqueo de Control

Resuelve el salto:

Actualiza el PC

DLX

Salto

Inst sig1

Inst sig2

Inst sig3

IF

ID

IF

EX MEM WB

ID EX

IF ID

IF

Inst válida IF

ID

EX MEM WB

Abortar tres instr. siguientes ⇒ 3 ciclos de bloqueo:

TÉCNICA “CONGELAR” O “VACIAR” la cadena

12

6

¿Se pueden abortar? : NO todas

¿Es grave el riesgo?

Decodifica: detecta que es salto

Salto

Inst sig1

Inst sig2

Inst sig3

IF

ID

IF

EX MEM WB

Instr Válida

IF

ID

EX MEM WB

No se puede abortar

• Riesgo inevitable de ejecutar IF de Inst sig1:

• Acceso al caché de instr. (no debería haberse producido).

• Por lo demás, sólo se modifican registros temporales.

¿Puede aumentar la razón de fallos de caché? ¿Cuándo?

EJERC.

13

¿Cómo afecta al rendimiento ?

Resuelve el salto

Saltos son

muy comunes

Salto

Inst sig1

Inst sig2

Inst sig3

IF

ID

IF

EX MEM WB

ID EX

IF ID

IF

IF

Inst válida

CPI control =

ID

EX MEM WB

N º c.bq.(control ) N º c.bq.(control ) N º saltos

=

×

= Psaltos Fsaltos

N º instr.

N º saltos

N º instr.

PROGRAMAS INT: CPIcontrol = 0.2 * 3 cic = 0.6 c.bq./instr

A=

t ejec real

t ejec ideal

=

1 + 0.6

1

⇒ 60% más lenta ⇒ INTENTAR

MEJORAR

14

7

SOLUCIÓN: Adelantar Resolución

IDEAL

Resuelve

el salto

No hacen nada

Salto

Inst válida1

Inst válida2

IF

ID

IF

EX MEM WB

ID EX MEM

IF ID EX

0 c.bq.

∀salto

(intentar acercanos a lo anterior)

• Adelantar la resolución para evitar bloqueos.

• El coste adicional no debe ser alto.

15

INDICE

INDICE

1. Introducción.

2. Dependencias, riesgos y bloqueos de control.

3. Consideraciones de implementación.

4. Comportamiento de los saltos condicionales.

5. Implementaciones alternativas de saltos.

6. Visión de conjunto.

16

8

Esquema del DLX

TRASLADAR

PCdest

Cond

+

RE

PLI

CAR

PCdest

17

DLX con saltos adelantados

PCdest

Se alarga la fase ID

Selecc

18

9

Consideraciones de la nueva

implementación

EX

• ¿Incompatible? con lectura de registros en el

ID

2º semiciclo (WB, escritura en el 1º).

IF

• Mayor complejidad ⇒ Nuevo sumador,

Nuevos caminos de desvío (Operando Rcond

leído en fase ID).

• Nuevos bloqueos ⇒ estudiar nuevos bloqueos

de datos que han de introducirse.

EJERC.

Sol: ALU R1,…

⇒ 1 c.bq.

Prob1, B. 3

BEQZ R1, etiq

MEM WB

EX MEM

ID EX

IF ID EX

IF ID

⇒ 2 c.bq.

Load R1, [dir]

BNEZ R1, etiq

Load R1, [dir]

⇒ 1 c.bq.

instr sin dependencias

BEQZ R1, etiq

19

CPIcontrol tras el adelantamiento

TÉCNICA “CONGELAR” O “VACIAR” la cadena

No hacen nada

Salto

Inst sig1

Inst válida

IF

ID

IF

EX MEM WB

IF

ID

ABORT

1 c.bq.

EX

CPIcontrol = Fsaltos * Psaltos= 0.2 * (1) = 0.20 ⇒

A=

t ejec real

t ejec ideal

=

1 + 0.2

1

⇒ 20% más lenta

20

10

Mejorar aún más el rendimiento

• Los saltos son instr. muy comunes (“Acelerar el caso

común”).

• Muchas máquinas reales tienen muchas más fases que el

DLX: Resuelven el salto en la 3ª, 4ª o más.

• MIPS R4000 (1992, 8 fases), en la 4ª fase (EX).

• Pentium (1992, 5 fases), en la 4ª fase (EX).

• UltraSPARC III (1999, 12 fases), en la 8ª fase (EX), etc.

•

(hoy, tendencia hacia la supersegmentación...)

21

Ejemplo: intentar aumentar el

rendimiento por supersegmentación

EJERC.

P3 B.3

DLX2: TDLX2 → TDLX/2 (por similitud resolvería los

CPIcontrol = 0.2 * 3= 0.6

saltos al final de ID2)

No hacen nada

Salto T IF1 IF2 ID1 ID2 EX1 EX2 M1 M2 WB1 WB2

IF1 IF2 ID1

3 c.bq.

Inst sig1

IF1 IF2

Inst sig2

IF1

Inst sig3

IF1 IF2 ID1 ID2 EX1 EX2 M1 M2 WB1 WB2

Inst válida

A=

t ejec DLX

t ejec DLX2

=

N instr TDLX CPI DLX

2 × (1 + 0.2)

2.4

=

=

= 1.5

N instr TDLX2 CPI DLX2

(1 + 0.6)

(1.6)

¡La supersegmentación no tiene por qué ser la clave!

CPIcontrol mucho mayor. Cuantificar otros bloqueos y reducción de TDLX2

11

Principales soluciones para mejorar

aún más el rendimiento

• Muchos mecanismos de reducir más el CPIcontrol:

• Sofisticar saltos (tras estudiar su comportamiento,

desde el punto de vista estático y dinámico).

• Eliminándolos (se conoce con exactitud su

comportamiento, ej. bucles , se verá más adelante). Estática y

dinámicamente

• Técnicas dinámicas más avanzadas.

IDEA: Si se supiera el comportamiento de un salto (“predecir”)

⇒ intentar ejecutar instrucciones de la rama válida.

23

INDICE

INDICE

1. Introducción.

2. Dependencias, riesgos y bloqueos de control.

3. Consideraciones de implementación.

4. Comportamiento de los saltos condicionales.

5. Implementaciones alternativas de saltos.

• Saltos que apuestan.

• Saltos retrasados.

• Saltos retrasados con anulación.

6. Visión de conjunto.

24

12

Comportamiento medio de los saltos

condicionales

•Programas INT: Saltos Cond: %T = 60%-70% ; %NT= 40%-30%

⇒ T son el doble de frecuentes ⇒ CASO COMÚN

•Programas FP: Saltos Cond: %T = 65%-75%

PCdest : Saltos Hacia atrás (PCdest <= PCsalto) %T = 85%

Saltos Hacia adelante (PCdest >PCsalto) %T = 60%

⇒ Saltos hacia atrás casi siempre se Toman (bucles).

Estas estadísticas no varían mucho con las entradas de un prog.

ÚNICA CONCLUSIÓN GENERAL (∀

∀ salto):

TOMADO ES EL CASO COMÚN

25

Comportamiento individualizado de

los saltos (“profiling”)

Estadísticas de ejecuciones previas ⇒ Cada salto está muy

“polarizado” (bucles, condiciones de salida, etc.).

• Si se asocia un comportamiento individual a cada salto:

% error en la predicción (DLX) prog. INT: 15% ; prog. FP: 9%

En la media: (INT) 46 instr sin errar ; (FP) 173 instr sin errar.

• Estas estadísticas no varían mucho con las entradas.

• El compilador indicaría la predicción en un bit del opcode.

(Ej. Intel i960CA).

• IDEA BUENA, pero … PROBLEMAS:

• Realizar ejecuciones temporales en medio de la compilación

• Habría doble número de tipos de saltos.

⇒ Hoy se implementa esto con técnicas dinámicas

26

13

INDICE

INDICE

1. Introducción.

2. Dependencias, riesgos y bloqueos de control.

3. Consideraciones de implementación.

4. Comportamiento de los saltos condicionales.

5. Implementaciones alternativas de saltos.

• Saltos que apuestan.

• Saltos retrasados (“Delayed”).

• Saltos retrasados con anulación (“Cancelling”)

6. Visión de conjunto.

27

Saltos que apuestan

1

TÉCNICA “CONGELAR” O “VACIAR” LA CADENA

(Siempre se abortan las instr. siguientes).

c.bq.

NT

1

T

1

CPIcontrol = 0.2 * (1) = 0.2

Si se sabe que va a hacer ser un salto (predecir), se puede

“apostar” (implementación) empezando a ejecutar la rama

predicha:

• 2. APOSTAR POR NO TOMADO

• 3. APOSTAR POR TOMADO

28

14

2.TÉCNICA “APOSTAR” POR SALTO NT

Salto NT IF ID EX MEM WB

IF ID EX MEM

Inst sig1

IF ID EX

Inst válida (sig2)

IF ID EX MEM WB

Salto T

IF

Inst sig1

IF ID EX

Inst válida (dest)

0 c.bq.

ABORT

1 c.bq.

TÉCNICA “APOSTAR” POR SALTO NT (No abortar

instr. siguientes). NOTA: Implem normal del DLX es Ap.NT

2

CPIcontrol = Fsaltos * Psaltos= Fsaltos * (%NT * PsaltosNT+ %T * PsaltosT)

c.bq.

NT

0

T

1

CPIcontrol = 0.2 * (0.3*0 + 0.7*1) = 0.14

(no se mejora mucho, pues favorece el

caso menos común NT)

29

3. TÉCNICA “APOSTAR” POR SALTO T

Salto NT IF ID

IF

Inst dest1

Inst válida (sig1)

EX MEM WB

ABORT

IF

ID

EX MEM

1 c.bq.

IF ID EX MEM WB

Salto T

IF ID EX MEM

Inst dest1

0 c.bq.

Inst válida (dest2) IF ID EX

TÉCNICA “APOSTAR” POR SALTO T (Buscar instr de

destino).

3

CPIcontrol = Fsaltos * Psaltos= Fsaltos * (%NT * PsaltosNT+ %T * PsaltosT)

c.bq.

NT

1

T

0

CPIcontrol = 0.2 * (0.3*1 + 0.7*0) = 0.06

(se mejoraría bastante, favorecería caso común)

30

15

“APOSTAR” POR SALTO T NO SE

PUEDE IMPLEMENTAR EN DLX

Buscar instr. de destino no se puede realizar hasta que no se conozca

el PCdest (en fase ID). Flecha celeste: búsqueda IMPOSIBLE.

Siempre se cargará la inst. sig1 en el ciclo sig. (PC←PC+4)

Cond

PCdest No hacen nada

Salto

Inst sig1

Inst dest1

IF

ID

IF

EX MEM WB

IF

ABORT

1 c.bq.

ID

Inst válida

• Como PCdest y Cond se conocen en la misma fase, no tiene

sentido en DLX (en el ciclo en que se podrían buscar las instr de

destino, ya se conocen las válidas). Pero sí con técnicas dinámicas.

• En DLX sería equivalente en prestaciones a “congelar” la cadena.

EJERC.

Máquina que resuelva Cond y PCdest en fases difer. 31

INDICE

INDICE

1. Introducción.

2. Dependencias, riesgos y bloqueos de control.

3. Consideraciones de implementación.

4. Comportamiento de los saltos condicionales.

5. Implementaciones alternativas de saltos.

• Saltos que apuestan.

• Saltos retrasados.

• Saltos retrasados con anulación.

6. Visión de conjunto.

32

16

4. SALTO RETRASADO

Instr ant1

Instr ant2

Instr ant3

Salto IF ID

Inst sig1

IF

Instr

ant2

Inst válida

EX MEM WB

ID EX MEM WB

IF ID

IF

IF

HUECO DEL

SALTO (‘delay slot’)

•En DLX hay una instrucción dependiente del salto (HUECO).

•El compilador podría introducir una instrucción, p.ej. anterior

al salto en este “hueco” (planificación estática).

•Implementar un nuevo salto DBEQZ, DBNEZ que siempre

ejecuta la instrucción del hueco. (D=‘Delayed’)

33

4

TÉCNICA “SALTO RETRASADO” (Ayuda del compilador).

DBNEZ

Inst ant

Inst válida

IF

ID

IF

EX MEM WB

ID EX MEM WB

IF ID EX

IF ID

Pero: el número de instrucciones

anteriores para rellenar es pequeño.

La instr del hueco

SIEMPRE se ejecuta

0 c.bq. ∀ salto.

CPIcontrol =0

Nº instr Efectividad(Efant)

1

40%

2

10% (≈

≈ 0%)

Existen muchas dependencias reales y el bloque básico contiene muy

pocas instrucciones (en prog INT, un salto cada 4-7 inst). Ejemplo:

ADDI R1, R1, 4

Si la máq sólo DBEQZ. Si no hay inst ant:

SGT

R3, R1, R5 ⇒ - Rellenar con NOP (bloqueo software).

BEQZ R3, etiq

- Rellenar con instr de la “rama predicha”

¡Cuidado! El hueco se ejecuta siempre. 34

17

Otra opción: rellenar el hueco con

instrucciones de destino (caso común)

Instr. con depend.

Ej. ADDI R1, R1, 4

SGT R3, R1, R5

BEQZ R3, etiq

instr siguiente

...

etiq: instr dest1

instr dest2

ADDI R1, R1, 4

SGT R3, R1, R5

DBEQZ R3, (etiq+4)

INSTR. DEL

instr dest1

HUECO instr

instr siguiente

dest1 es

...

“Inofensiva”

etiq: instr dest1 para la rama NT

instr dest2

• Aumenta el tamaño del código.

• Si el salto no se toma, la ejecución de la instrucción del hueco no

es útil (como si fuera un bloqueo software).

• Recuerda a “Apostar por tomado”, pero estática (compilador)

• La efectividad es alta (Eframa 1 instr ≈ 75%) (ramas independ)

35

Ejemplos de CPIcontrol con saltos

retrasados

Ej.

c.bq.

Si sólo existen DBEQZ y todo hueco se rellena con instr.

destino (todas inofensivas)

NT

1

T

0

CPIcontrol = 0.2 * (0.3*1 + 0.7*0) = 0.06

EJERC.

Más realista: Si sólo existen DBEQZ que se rellena con instr

anteriores, y si no, con instr de destino, y si no, con NOP:

CPIcontrol = Fsaltos * (%no_rell_Ant* Pcaso_no + %rellenar _Ant * 0) =

= Fsaltos* %no_rell_Ant* ( (1-Efdest)* 1+ Efdest * (%NT*1+%T*0) )

= 0.2 *

0.6

* ( (1-0.75) * 1 + 0.75 * ( 0.3 * 1 + 0.7*0) ) =

= 0.12 * (0.25+0.225)=0.057

relleno con NOP. Inst destino ejec. inútilm.

Efdest =Efectividad de rellenar con instrucciones del destino=75%

CPIcontrol aún no muy bajo ⇒ otras alternativas para “aprovechar” hueco 36

18

INDICE

INDICE

1. Introducción.

2. Dependencias, riesgos y bloqueos de control.

3. Consideraciones de implementación.

4. Comportamiento de los saltos condicionales.

5. Implementaciones alternativas de saltos.

• Saltos que apuestan.

• Saltos retrasados.

• Saltos retrasados con anulación.

6. Visión de conjunto.

37

Salto retrasado con anulación

• Difícil rellenar el hueco (instr indep son pocas).

• Si el salto es capaz de anular o cancelar las

instrucciones del hueco ⇒ No tantos problemas para

rellenarlo con instr. de una u otra rama (Efectividad ≈ 90%)

• CBEQZ o CBNEZ (C de ‘cancelling’)

• Más complejo de implementar, pero más prestaciones.

• Aprovecha que los saltos están muy “polarizados”.

• Compilador introduce la instrucción de la rama predicha

⇒ CBNEZ.pt y CBNEZ.pnt

• Siguen valiendo los ejemplos de reordenación de instr.

(de destino o anteriores)

38

19

Cronogramas para saltos retrasados

con anulación

CBEQZ.pt (T) IF

Inst dest1 (hueco)

Inst válida

ID

IF

EX MEM WB

ID EX MEM

IF ID EX

CBEQZ.pt (NT) IF

Inst dest1 (hueco)

Inst válida

ID

IF

EX MEM WB

IF

ID

ID

IF

EX MEM WB

ID EX MEM

IF ID EX

CBEQZ.pnt (T) IF

Inst sig1

Inst válida(sig2)

ID

IF

EX MEM WB

ID

1 c.bq.

CANCEL

EX

CBEQZ.pnt (NT) IF

Inst sig1

Inst válida (sig2)

IF

0 c.bq.

0 c.bq.

1 c.bq.

CANCEL

EX

39

Penalidad saltos retrasados con

anulación

NOTA: CBEQZ.pnt ≡ BEQZ Apostar por NT (TÉCNICA 2)

CBEQZ.pnt

CBEQZ.pt

Ej.

NT

0

1

T

1

0

CBEQZ

Ac.

0

Fall

1

Calcular CPIcontrol medio para programas FP e INT. Suponer

la predicción se hace por ejecuciones previas (profiling) y

100% de efectividad.

INT: CPIcontrol = Fsaltos * (%Ac * 0 + %Fall * 1) =

= 0.2*(0.15 * 1) = 0.03 c.bq./instr

FP: CPIcontrol = Fsaltos * (%Ac * 0 + %Fall * 1) =

= 0.1*(0.09 * 1) = 0.009 c.bq./instr 40

20

Otros casos con más instr. en el hueco

Hoy es más realista: por ejemplo DLX que resuelve saltos

en la cuarta fase (MEM).

PCdest

Cond

D3BNEZ

Inst ant1

Inst ant2

Inst ant3

IF

ID

IF

EX MEM WB

ID EX MEM WB

IF ID EX MEM WB

IF ID EX MEM WB

Inst válida IF

SIEMPRE SE

EJECUTAN

• Encontrar tres instr anteriores es muy difícil

0 c.bq. Si fuera ∀

salto, entonces:

CPIcontrol =0

• Técnica estática, prob. de compatibilidad futura

41

Problemas de los saltos retrasados

• Problemas de herencia. Nuevos procesadores llevan ya

otros mecanismos ⇒ hardware tendrá que implementar

tales saltos para que el software antiguo sea compatible.

• Excepción retomable en instrucción del hueco (salto T):

Salto T IF

Inst hueco

Inst válidas

(de dest)

ID

IF

EX MEM WB

ID EX MEM

IF ID EX

IF ID EX

Excepción (fallo de pág)

Guardar:

PC1 o información.

PC2

•“Técnicas dinámicas son trasparentes al usuario (ventaja)”.

Hoy se sigue una técnica similar a CBEQZ pero

dinámicamente (caché de predicción). Muy efectiva.

42

21

INDICE

INDICE

1. Introducción.

2. Dependencias, riesgos y bloqueos de control.

3. Consideraciones de implementación.

4. Comportamiento de los saltos condicionales.

5. Implementaciones alternativas de saltos.

6. Visión de conjunto (máquinas reales).

43

Visión de conjunto

• Todas estas técnicas son la base para comprender técnicas

dinámicas más avanzadas (se verán en sig. apartado).

• Casi ningún procesador tiene tres tipos de saltos.

• HOY: los saltos retrasados sólo existen en máquinas que

los heredan (compatibilidad).

• Motorola 88000: DBEQZ + BEQZ (Apostar NT)

• Intel i860:

CBEQZ.pt + BEQZ (Apostar NT)

• SPARC (existe) : DBEQZ + CBEQZ.pt (Apostar NT)

• La deceleración debida al CPIcontrol se dispara cuanto

menor es CPI (en superescalares) ⇒ más énfasis.

44

22

NOTA: Concepto de “especulación”

de instrucciones y riesgos adicionales

• Ej: 2. TÉCNICA “APOSTAR” por salto NT en DLX que

resuelve saltos en fase MEM

Salto IF ID EX MEM WB

Inst sig1

IF ID EX

“ESPECULACIÓN”

IF ID

Inst sig2

IF

Inst sig3

Inst válida IF

• Se está especulando con algunas fases (ASP2: ampliación).

• Riesgos de acceder a instrucciones (caché), las cuales, si el salto

es T, nunca se debieron leer.

• Fases lanzadas: posibilidad de que se produzca excepción (ej DIV

por 0), que si es salto T nunca se debió producir.

• Si resolución aún más tardía ⇒ Más riesgos (se modifica el

estado del procesador en las fases MEM o WB de inst sig1,2,3...)

CONCLUSIONES

• SALTOS SON MUY COMUNES ⇒ CPICONTROL

ALTO (se nota más en superescalares).

• IMPORTANTE ADELANTAR LA RESOLUCIÓN

(PCdest y Cond)

• IMPORTANTE: CONOCIMIENTO DE SALTOS.

• SALTOS CON AYUDA DEL COMPILADOR :

PROBLEMAS (herencia, etc.)

• VEREMOS LA EXTENSIÓN DE ESTAS TÉCNICAS

DE FORMA DINÁMICA.

46

23