Contador asíncrono Contador síncrono

Anuncio

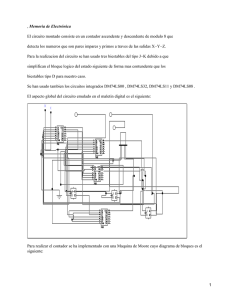

Circuitos contadores Contador asíncrono Contador síncrono Contadores síncronos l Un contador síncrono: l l l Incrementa/decrementa un valor de uno en uno (contador) Cada incremento se hace de acuerdo a un reloj (síncrono) Un contador síncrono se realiza mediante el uso de biestables l Por ejemplo, biestables ?po T o JK 2 Contadores síncronos l Entrada: l DEC/INC: determina si contamos hacia arriba o hacia abajo l l l C: señal de reloj l l Con cada transición a cero se produce un incremento/decremento Salida: l l DEC/INC=0 à incremento DEC/INC=1 à decremento Q=Qn…Q0: número de la cuenta Entradas adicionales: asíncronas y ac?vas por bajo l l l PRESET: si está ac?va, pone Q=1 CLEAR: si está ac?va, pone Q=0 HOLD: si está ac?va, pone Q(t+1)=Q (de?ene la cuenta) 3 Ejercicio 1 • Programad el siguiente contador de 4 bits, basado en biestables T • Podéis u?lizar el módulo T disponible en • hZp://avellano.usal.es/~compi/sol0901.htm • Verificad su correcto funcionamiento • Usad una variable de 4 bits en vez de cuatro variables de un bit para la salida 4 Ejercicio 1 ¡ ¿Qué se observa si, a mitad de la cuenta, modificamos la línea DEC/INC? § ¿Hay un cambio limpio de valores? ¡ Añadid las líneas PRESET, CLEAR y HOLD, ac?vas por bajo. § No modifiquéis el interior del biestable T, auxiliaros de las entradas PRESET y CLEAR de su interfaz ¡ Volved a modificar la cuenta con DEC/INC, pero ac?vando previamente HOLD § ¿Qué pasa ahora? 5 Ejercicio 2 • Modificad el programa para que realice la cuenta con?nuamente del 10 al 0 (en vez del 15 al 0), según el esquema: ¡ Observad que no realiza la cuenta correctamente: 10, 9, 8, 2, 1,0,10, 9, 8… § Esto ocurre porque es un contador asíncrono, y las transiciones tardan en propagarse a todos los biestables, dando estados intermedios no deseados que van a afectar a la puerta NAND § Solución1: añadir una quinta entrada a la puerta NAND, que conecte con el reloj § Solución2: introducir un pequeño retardo en la puerta NAND 6 Ejercicio 2 • ¿Por qué cuenta mal? • La puerta NAND, cuando la salida de los biestables es 1111 (15), resetea el 3 y el 1 para ponerlo a 1010 (10) • Si depuráis la salida del contador, podéis ver todos los estados intermedios: Estado intermedio (inocuo) Estado intermedio à implica la 1010 (10)! activación de NAND 1011, 1001 (9)! 1000 (8)! 1001, 1011, 1111, 0111 (7)! 0110 (6)! 0111, 0101 (5)! Eso hace que el 0111 (7) 0100 (4)! se “limpie” a 0010 (2) 0101, 0111, 0011 (3)! 0010 (2)! 0011, 0001 (1)! 0000 (0)! 0001, 0011, 0111, 1111, 1010 (10)! ¡ ¿Por qué funcionan las soluciones propuestas? 7 Ejercicio 3 • Comprobad, mediante Verilog, el correcto funcionamiento de este contador síncrono construido con biestables JK 8 9