Dispositivos de las tecnologías CMOS

Anuncio

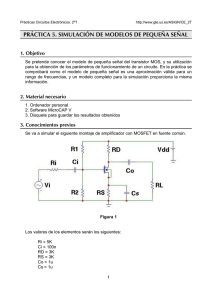

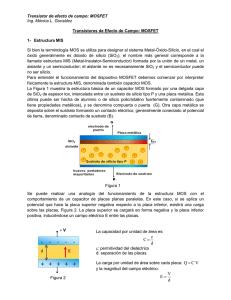

Dispositivos de las tecnologías CMOS MOSFET: canal N y canal P (únicos dispositivos en chips digitales) BJT: PNP de mala calidad (dispositivos parásitos. Se usan como diodos) Resistencias Condensadores Autoinducciones - Algunos dispositivos pasivos implican pasos adicionales de fabricación. - Las tecnologías BiCMOS incluyen además BJTs NPN y PNP de buena calidad Transistor BJT vertical z y x x C C B E P+ N+ P+ N B E N P Ic P BJT − PNP − El colector siempre es el sustrato − Muy poca ganancia (βF =5) Aplicaciones: − Referencias de tensión Band−Gap Transistor BJT Lateral E z x G B y x SUB SUB C SUB B C B E G P+ N+ N P+ Ic P+ Isub N P P − PNP − Terminales B y G conectados juntos para evitar conducción por MOSFET parásito − Hay un PNP vertical parásito que también conduce C G E RESISTENCIAS (Lámina conductora: 2 dimensiones) (5 cuadros) W Nº de cuadros = L / W R = ρ x Nº de cuadros 1c 1c 1c 1c 1c Parámetros: −L −W − N. of Bends (número de pliegues) L 1 c 1 c 1 c 1 c 1 c 0.6c (13.2 cuadros) 1c 1c 1 c 1 c 1 c 1 c 1 c 0.6c 1c 1c 1c 1c (11 cuadros) 1c 1c 1c 1c 1c 1c 1c S A P+ B N+ N+ RNWELL 1000 Ω / S P A B N+ A P+ RDIFFP B S N P A B A RPOLY 8Ω/ 50 Ω / B N S 140 Ω / A Oxido grueso P B Resistencias - Las resistencias construidas en el silicio (RNWELL, RDIFFP) se pueden considerar como transistores J-FET con una tensión de pinch-off muy grande. - Esto se traduce en unas dependencias de la resistencia con el voltaje y la temperatura malas. RNWELL RDIFFP RPOLY RPOLY HR METAL 1 ρ(Ω/) 1000 140 8 50 0.07 Coef. V (ppm/V) 10000 200 100 100 - Coef. T (ppm/K) 8000 1500 900 590 - Tolerancia 40 % 30 % 30 % 20 % 70 % CONDENSADORES MOS C UNION MOS cap. LF varactor HF P Acumulación V Condensador de INVERSION (transistor) Condensador de ACUMULACION (varactor) N+ ~1/3 Cox Inversión 0 N+ N+ P+ P+ N N P Cox P Condensadores MOS de acumulación No se necesitan pasos adicionales en su fabricación. (CMOS éstandar) Alta densidad de capacidad (f F/µm2). Mayor que otros tipos de condensador Tiene polaridad. Requiere un nivel de DC. Varactor. C(V). Coeficiente de voltaje malo. Coeficiente de temperatura malo. Aplicaciones: Varactor, Desacoplo de alimentación... Condensador de Doble Polisilicio Condensador MIM Z X Oxido grueso Condensador interdigitado Y X Poly 2 Poly 1 Metal N Siliciuro Condensadores de doble poly / MIM Necesitan pasos de fabricación adicionales No tienen polaridad Asimétricos. La capacidad parásita al sustrato es mucho mayor en la placa inferior Precisos Condensadores interdigitados No necesitan pasos de fabricación adicionales Simétricos Densidad de capacidad aceptable en tecnologías CMOS finas Poco precisos. Tolerancia: 40 % AUTO INDUCCIONES − Capas de metal grueso (menor resistencia serie) − Sustrato de alta resistividad (poco dopado) − Rango: decenas de nH (f > 1GHz) − Qmax ~ 10 − Modelado: ASITIC A B A B A L Rs C1 B C2 SUB TRANSISTOR MOSFET D ID G B VGS ID LINEAR TRIODO OHMICA VDS S I Dsat SATURACION SATURACION VGS CORTE CORTE VDS VT VGS TRANSISTOR MOSFET en SATURACION (VDS > VOV ) 2 ; Definimos: V ID = K2P W V − V ( ) OV = (VGS − VT ) GS T L ID = KP W 2 VOV 2 L KP depende de la tecnología y del tipo del transistor (canal N o P). KP = µ0COX unidades : A/V 2 µ0 : Mobilidad de los portadores en el canal (m2 /(V · s)). La mobilidad de los electrones suele triplicar a la de los huecos. 2) COX = ε0εtSiO2 : Capacidad del óxido de puerta por unidad de área (F/m ox W y L son el ancho y largo del canal del MOSFET TRANSISTOR MOSFET en SATURACION La corriente depende ligeramente de VDS : ID = KP W (VGS − VT )2 (1 + λVDS ) 2 L ID I D0 1/r ds = I D0 λ VGS VDS −1/λ 1 λ depende de la longitud del canal: λ ∝ L−L 0 Modelo simple de PEQUEÑA SEÑAL del MOSFET gm = ∂ID 1 = rds ∂VDS ∂ID ∂VGS G D vgs gm vgs rds S,B gm = K P W VOV L = s 2ID KP 1 rds = λID W L = 2ID VOV TRANSISTOR MOSFET en región TRIODO / LINEAL / OHMICA (VDS < VOV ) W 1 2 I D = KP (VGS − VT ) VDS − VDS L 2 VDS Para VDS → 0, tenemos: ID ≈ KP W V V = L OV DS rON rON = 1 KP W L VOV Efecto de la tensión del sustrato (VB 6= VS ) VD VG VB VS - El sustrato se comporta como la puerta de un JFET parásito - Aumenta la tensión umbral efectiva: VT = VT H0 + γ q φ − VBS − q φ - Transconductancia adicional (resta ganancia): γ gm gmb = √ 2 φ − VBS (φ ≈ 0,6V ) Modelo de pequeña señal incluyendo el efecto del sustrato G D vgs gm vgs S B vbs gmb vbs rds MOSFET en alta frecuencia: Capacidades parásitas SATURACION C GS C GB S C C GD G D C DB SB B Si la fuente y el sustrato están unidos: CGStot = CGS + CGB , CDS = CDB CGS ≈ 2 W · L · COX 3 CGD = Cover · W MOSFET en alta frecuencia: Modelo de pequeña señal C gd G D C gs gm vgs r ds C ds S gm 3 µ0VOV ωT ≈ = Cgs 2 L2 (∼ 14 GHz, canal N, VOV = 200 mV, L = 0,35 µm) MOSFET en alta frecuencia: Capacidades parásitas TRIODO (Interruptores, Condensadores MOS de inversión) Modelo no cuasi−estático Modelo normal G C GS S D D rON G C SB D 1/2 W·L·Cox C DB B CGS = W · L · COX 1/2rON G S 1/2 W·L·Cox W·L·Cox 1/2rON S MOSFET en débil inversión / conducción subumbral 1000 100 Débil inversión Id (uA) 10 1 KpW 2 Vov 2 L α exp(Vov) Fuerte inversión 0.1 0.01 0.001 -0.3 ID,wi = Conducción subumbral -0.2 W VOV It exp L nKT /q -0.1 ! 0 0.1 Vov (V) ( 0.2 0.3 0.4 n : slope f actor (∼ 1,5) It : corriente para VOV = 0 RUIDO vn Señales NO correlacionadas: Se suman las POTENCIAS: vn1 v 2n = v 2n1 + v 2n2 vn2 √ √ - Densidad espectral (unidades: V / Hz o A/ Hz ) - Ruido total en una banda de frecuencias (de f0 a f1): 2 VN,tot = Z f 1 f0 vn(f )2 df - Si vn(f ) = cte (ruido blanco) queda: 2 2B VN,tot = vn (B = f1 − f0 = ancho de banda) Ruido. Tipos. Fuentes físicas * Ruido blanco: densidad espectral constante Ruido térmico. Resistencias. Se debe al movimiento aleatorio de los electrones. 2 = 4KT R vn Ruido “shot”. Barreras de potencial (diodos, BJT...). Se debe al valor discreto de la carga del electrón. (el electrón pasa o no pasa la barrera). i2 n = 2qI (q : carga del electron) * Ruido “flicker”: densidad espectral ∝ 1/f . Ruido rosa Origen poco claro, aunque se cree que se debe a la captura y emisión de portadores desde impurezas, estados superficiales, etc. MOSFET: Fuentes de ruido 2 log(i d ) D (gmvnf ) 2 flicker vnf in G i 2n térmico S,B f corner Ruido térmico en el canal: i2 n = 4KT γ gm (0,66 < γ < 2,5) Ruido Flicker. Dominante para frecuencias bajas (f < fcorner ): vnf (f )2 = Kf 2 W Lf Cox log(f) MOSFET. Otras fuentes de ruido (importantes para LNAs) D vng RG G vnb RB S,B 2 = 4KT R - Las resistencias generan un voltaje de ruido vn - El polisilicio de la puerta puede tener una resistencia apreciable, R G , que da lugar a un ruido: ρ poly W/L 2 vn,poly = 4KT 12 n2 n: número de puertas del transistor (con un contacto a cada lado). - Sustrato poco dopado =>RB grande. El ruido térmico del sustrato da lugar a una corriente: 2 i2 = 4KT R g B nb mb MATCHING En el mundo analógico no existen dos valores iguales ( 1 − 1 6= 0 :) MISMATCH ≡ Variación de un parámetro de un dispositivo relativa al de otros dispositivos nominalmente idénticos del mismo C. I. Causas del MISMATCH • Variaciones sistemáticas ◦ Gradientes: Parámetros tecnológicos dependientes de la posición en la oblea ◦ Efectos de borde ◦ Efectos del entorno del dispositivo. Proximidad a otras estructuras • Variaciones estadísticas (aletorias) MATCHING de transistores ID + ∆ID = KP + ∆KP W + ∆W [VGS − (VT + ∆VT )]2 2 L + ∆L D Mismatch de corriente: ∆I I D ∆KP : debido a variaciones del espesor del óxido de puerta y del dopado del sustrato (movilidad de portadores) ∆VT : debido a variaciones en el dopado del sustrato y a la carga atrapada en el óxido de puerta ∆W , ∆L : Variaciones de la geometría del transistor debidas a la litografía Estrategias para el buen MATCHING Utilizar dispositivos idénticos (misma W , misma L ). Para obtener ratios 6= 1 se conectan dispositivos en paralelo o serie • De este modo los efectos de borde son los mismos en todos los dispositivos. • Dispositivo grande ≡ P I dispositivos pequeños 2I I MAL: BIEN: W/L 2W/L W/L 2I W/L W/L Estrategias para el buen MATCHING Los dispositivos deben estar próximos • Menor efecto de los gradientes • Layout entrelazado G1 G2 M1 M2 M1 M2 S1 D1 S2 D2 Estrategias para el buen MATCHING Layout de CENTROIDE COMÚN • Cancelación de efectos de gradientes (derivadas impares) M1 M2 M2 M1 Estrategias para el buen MATCHING Las corrientes deben fluir en la misma dirección • Gradientes de dopado =>Campo eléctrico en el sustrato =>movilidad dependiente de la dirección MAL I1 M1 BIEN I2 M2 I1 M1 I2 M2 Estrategias para el buen MATCHING Dispositivos DUMMY • No se conectan • Hacen que el entorno sea similar en todos los dispositivos activos (Un entorno distinto puede generar errores en la litografía) DUMMY DM DUMMY M1 M2 M3 M4 DM Estrategias para el buen MATCHING Mismatch estadístico √ • N dispositivos en paralelo =>σN = σ/ N • Mismatch inversamente proporcional al área activa del dispositivo Valores típicos para el matching (estimación muy grosera) Transistores 1% Resistencias 1% Condensadores MIM, doble poly 0.1 %