Microcontroladores PIC16FXX:

Anuncio

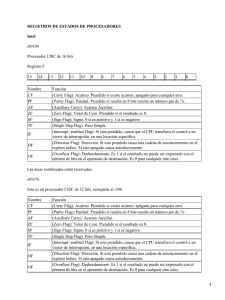

Microcontroladores PIC16FXX: Estructura, organización y set de instrucciones Estructura del microcontrolador Estructura de la CPU Organización de las memorias Memoria de programa Memoria de datos Organización de la memoria de datos Registros del procesador Registros del procesador Modos de direccionamiento Direccionamiento Indirecto El par de FSRnH y FSRnL generan una dirección de 16 bits que permite a 64K. La memoria está organizada en tres regiones: Traditional Data Memory Linear Data Memory Program Flash Memory Direccionamiento Indirecto Circuito de temporización OSCCON bits SPLLEN: Software PLL Enable IRCF: Internal Oscillator Frequency Select Bit 2 Unimplemented SCS: System Clock Select 1x = Internal oscillator 01 = Timer1 oscillator 00 = Clock determined by Configuration Word 1. OSCSTAT bits T1OSCR: Timer1 Oscillator Ready PLLR: PLL Ready OSTS: Oscillator Start-up Time-out Status HFIOFR: High Frequency Internal Oscillator Ready HFIOFL: High Frequency Internal Oscillator Locked MFIOFR: Medium Frequency Internal Oscillator Ready LFIOFR: Low Frequency Internal Oscillator Ready HFIOFS: High Frequency Internal Oscillator Stable Estructura del microcontrolador BORCON bits SBOREN: Software Brown-out Reset Enable Unimplemented: Read as ‘0’ BORRDY: Brown-out Reset Circuit Ready Status PCON bits STKOVF: Stack Overflow Flag STKUNF: Stack Underflow Flag Unimplemented: Read as ‘0’ RMCLR: MCLR Reset Flag RI: RESET Instruction Flag POR: Power-on Reset Status Power-on Reset occurs) BOR: Brown-out Reset Status Estructura de interrupciones INTCON bits GIE: Global Interrupt Enable PEIE: Peripheral Interrupt Enable TMR0IE: Timer0 Overflow Interrupt Enable INTE: External Interrupt Enable IOCIE: Interrupt-on-Change Enable TMR0IF: Timer0 Overflow Interrupt Flag INTF: INT External Interrupt Flag did not occur IOCIF: Interrupt-on-Change Interrupt Flag PIE1 bits TMR1GIE: Timer1 Gate Interrupt ADIE: A/D Converter Interrupt RCIE: USART Receive Interrupt TXIE: USART Transmit Interrupt SSPIE: Synchronous Serial Port Interrupt CCP1IE: CCP1 Interrupt TMR2IE: TMR2 to PR2 Match Interrupt TMR1IE: Timer1 Overflow Interrupt Estructura del microcontrolador INTCON: INTERRUPT CONTROL REGISTER OPTION_REG: OPTION REGISTER PIE1, 2, 3: PERIPHERAL INTERRUPT ENABLE REGISTER 1, 2, 3 PIR1, 2, 3: PERIPHERAL INTERRUPT REQUEST REGISTER 1, 2, 3 Set de Instrucciones Set de Instrucciones Set de Instrucciones Set de Instrucciones Set de Instrucciones Set de Instrucciones