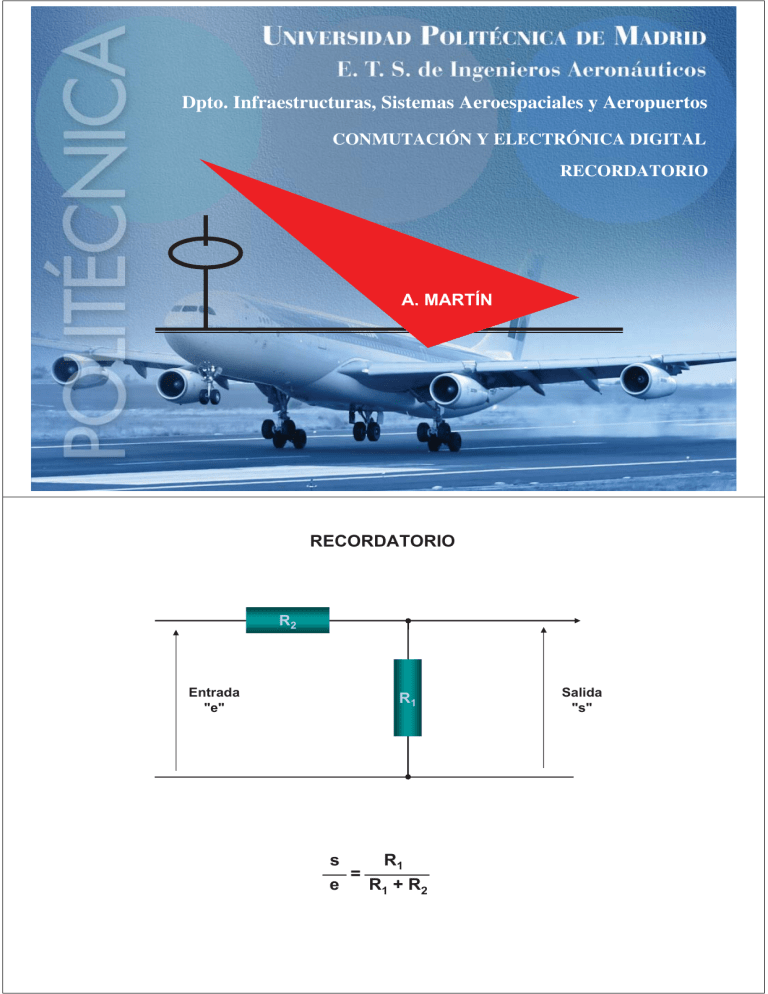

Dpto. Infraestructuras, Sistemas Aeroespaciales y Aeropuertos

CONMUTACIÓN Y ELECTRÓNICA DIGITAL

RECORDATORIO

A. MARTÍN

RECORDATORIO

R2

Entrada

"e"

R1

s

e

=

R1

R1 + R 2

Salida

"s"

RECORDATORIO

R2

R1R=1 f

Entrada

"e"

s

e

=

R1

R1 + R 2

Salida

"s"

= 1 al no haber intensidad

RECORDATORIO

Entrada

"e"

R1

Salida

"s1"

s1

e

=

R2 + R3

R1 + R 2 + R 3

R2

Salida

"s2"

s2

e

=

R3

R1 + R 2 + R 3

R3

s1 – s2

e

=

R2

R1 + R2 + R3

RECORDATORIO

En aplicaciones "pasa banda" se denomina filtro pasa bajos.

Si se aplica una señal continua a la entrada de forma instantánea, la respuesta

transitoria depende del estado del condensador

RECORDATORIO

R

I

E

C

s

Con el condensador descargado se

cierra el interruptor.

Aparece una intensidad que es decreciente a medida que el condensador

se carga.

El análisis del transitorio se realiza

planteando las ecuaciones.

s = E ( 1 – e –t/RC)

E–s=IR

I = C ds/dt

s/E

s (0) = 0

t/RC

RECORDATORIO

1

s/E

.63

s = E ( 1 – e –t/RC)

RC constante de tiempo

1

t/RC

RC >> carga lenta

RC << carga rápida

RECORDATORIO

Carga pulsada en función de la constante de tiempo

1s

Entrada

R

I

E

C

s

CR = 10 s

CR = 1 s

Nota: abierto no es lo mismo

que cero voltios en E0

CR = 1 ȝs

RECORDATORIO

RC

R

s

C

Con el condensador cargado a una tensión E, se cierra el interruptor,

aparece una intensidad a través de RC, que decrece con el tiempo al

ir disminuyendo la tensión entre las placas del condensador.

El proceso de descarga es similar al de carga y sigue la expresión:

s = E e –t/RcC

RECORDATORIO

1

s/E

s = E e –t/RcC

.37

RCC constante de tiempo

t/RCC

1

RCC >> descarga lenta

RCC << descarga rápida

RECORDATORIO

RC

R

s

C

E

El transitorio dependerá de los intervalos de conmutación de los interruptores,

así como de la relación RC-RCC.

Si RC >> R y los dos interruptores están conmutados, el condensador se cargará

a un valor ~E al cabo de un tiempo.

Si RC = R y los dos interruptores están conmutados, el condensador se cargará

al valor de E/2 al cabo de un tiempo, en el que la intensidad de carga se iguala

con la de descarga.

Si RC << R y los dos interruptores están conmutados, el condensador no podrá

cargarse al valor de E y la carga RC se alimentará a una tensión << E, ya que no

se puede entregar mas energía que la entrante.

RECORDATORIO

En aplicaciones "pasa banda" se denomina filtro pasa altos.

La ecuación del condensador I = C dV/dt indica que no puede soportar un salto

instantáneo de tensión entre sus placas. Inicialmente C está descargado.

C

E0

La forma de onda de la señal de salida:

s

I

E

Entrada

E

0

R

s

CR<<T

E

s

s

CR>>T

Final del Recordatorio

TEORÍA DE LA CONMUTACIÓN

(Febrero 2008)

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

DIODOS

Símbolo de representación

Sentido de conducción (sin efecto Zener)

Curva característica y su simplificación

http://electronred.iespana.es/diodo.htm

TRANSISTORES

Símbolo de representación

Conducción Ib/IC

Curva característica IC-VBE

Zona de corte. Rectificación

Zona exponencial. Amplificación variable (control)

Zona lineal. Amplificación y distorsión (amplificador)

Zona de saturación. El transistor como conmutador.

TEORÍA DE LA CONMUTACIÓN

Leer el Capítulo 11 de Ingeniería Electrónica de Julio González Bernaldo de

Quirós, Biblioteca Técnica Universitaria.

El transistor se comporta como un interruptor, tanto en la zona de corte como

en la de saturación.

En la zona de corte, la intensidad IC es cero, por lo que el transistor no consume potencia.

En la zona de saturación, la caída de tensión entre el colector y el emisor es

prácticamente despreciable. La potencia que debe de disipar es el producto de

la intensidad colector-emisor por la caída de tensión colector-emisor. En éstas

circunstancias es prácticamente cero.

El consumo inapreciable de potencia en las técnicas de conmutación a dado lugar al desarrollo a gran escala de circuitos integrados, que permiten la utilización de miles de transistores en un reducido espacio (técnicas LSI, VLSI, etc.)

donde en un cm2 se combinan aproximadamente 5000 componentes (transistores, diodos, resistencias y condensadores).

Para mayor información "Analysis and Design of Digital Integrated Circuits";David A. Hoges and Horace G. Jackson; 2ª Edición; MacGraw-Hill;1988.

http://perso.wanadoo.es/chyryes/glosario/vlsi.htm

Teoría de la Conmutación V.08

11

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Las pérdidas por conmutación

aumentan a medida que lo hace

la frecuencia de conmutación. La

velocidad está limitada por el

estado actual del arte (SOTA

State Of The Art). A veces es

necesario recurrir a la ventilación

forzada.

La ecuación general que gobierna la condición de conmutación

viene dada por:

siendo β la amplificación de corriente.

Las características mas importantes a tener en cuenta en el momento de

seleccionar un transistor para electrónica de conmutación son:

•

•

•

•

•

La tensión colector emisor en abierto VCEO

La intensidad IC

La tensión emisor base en abierto VEBO (relativo al efecto Zener)

La amplificación de corriente β

Tiempos turn-on/turn-off

“Características del Transistor 2N2219” puede ser descargado en:

http://www.digchip.com/members/parts/2n/parts_2n.php?s_id_member=101906

987104000228609

Teoría de la Conmutación V.08

12

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Ejemplo de aplicación de la ecuación general de conmutación utilizando un

transistor de valor β=10. Normalmente, son datos de partida la “carga” y el valor de la tensión suministrada por la fuente de alimentación, es decir Eb. La

incógnita suele ser la resistencia de base RB.

Es bastante normal que la tensión V0 de conmutación sea igual a Eb.

El emisor está a referencia cero, por lo que VB es VBE y VC es VCE, cuyos

órdenes de magnitud son similares y normalmente despreciables frente a Eb.

En estas condiciones, la ecuación se simplifica notablemente, hasta el

punto que para el cálculo de la resistencia de base se utiliza la expresión:

RB ≤ βRC

B

Supongamos que en el ejemplo planteado, RC vale 1 KΩ. Si se cumplen las

condiciones anteriores, el valor de la resistencia de base para que conmute el

transistor deberá de ser menor de 10 KΩ.

Si con ésta configuración se cambia a 330 Ω la resistencia de colector, el transistor deja de estar conmutado (pasa a la zona lineal utilizada en amplificación).

Para conmutar esta carga es necesario sustituir la resistencia de base por el

valor de 3,3 KΩ (ó menor).

Los valores de los componentes utilizados están comercializados, utilizándose

normalmente la serie de valores de tolerancia 20%.

Teoría de la Conmutación V.08

13

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

APLICACIONES

Los circuitos que se describen a continuación, se encuentran explicados en el

Capitulo 11, apartado 4 del libro “Ingeniería Electrónica” de J. González Bernaldo de Quirós.

Circuitos Cortadores ó Limitadores

Circuitos cortadores a nivel distinto de cero

Circuitos Restablecedores

Restablecedores automáticos

Cambio del nivel de polarización

Teoría de la Conmutación V.08

14

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Generadores de diente de sierra

Estos circuitos se emplean principalmente en los dispositivos de barrido y

de temporización, siempre que sean

prácticamente lineales. Para la descripción del circuito, ver apartado 11.5

IE-JGBQ.

El transistor conmuta en los niveles altos

de la entrada (si se cumplen las condiciones de conmutación), produciéndose la

descarga del condensador a través de la

resistencia interna colector-emisor del

transistor. Al ser una resistencia muy pequeña, se considera instantánea la descarga.

Cuando la señal de entrada produce el

corte del transistor, el condensador se

carga exponencialmente a la tensión Eb.

Barrido de un osciloscopio

Observando las curvas, para relaciones de t/RC > 4 se supone, a efectos de

cálculos, que la carga o descarga se ha producido totalmente. Es conveniente

memorizarlo, al igual que los valores correspondientes a t/RC = 1. Son valores

que se utilizarán con bastante frecuencia.

Teoría de la Conmutación V.08

15

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Se define como “alinealidad” al cociente de segmentos X/Y, siendo X el segmento interceptado entre la curva y tangente a la curva en t = 0, e Y el segmento entre la recta y el eje en ese instante. La alinealidad del diente de sierra

crece con el tiempo. Para pequeños valores de t/RC (~<0,3) se puede

considerar lineal en aplicaciones de medida de tiempo. La alinealidad es consecuencia de la carga del condensador a intensidad no constante. Con cualquier

procedimiento que logre cargar el condensador a intensidad constante, se

obtendría un diente lineal (integrador Miller, bootstrap, etc.) necesario en los

circuitos de barrido de tubos electrónicos.

MULTIVIBRADORES

La explicación de los circuitos que siguen a continuación se encuentra en los

apartados 11.6 - 11.9 de IE-JGBQ.

Flip-flop ó biestable (Memoria)

Hay dos estados estables. Si T1 conduce, entonces T2 está cortado y viceversa.

Para pasar de un estado a otro hay dos procedimientos:

•

Uno es hacer que deje de conducir el transistor que está conduciendo,

por ejemplo dando un impulso negativo en su base o bien tocando su

base con un punto de tierra.

•

Otro, que conduzca el transistor que está cortado dando un impulso positivo en su base (teniendo en cuenta que la amplitud del impulso debe

de cumplir la ecuación de conmutación en cuanto a intensidad).

Teoría de la Conmutación V.08

16

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Estas acciones de cambiar el estado se denominan de escritura, ya que el circuito mantiene su estado con el tiempo mientras no haya una acción externa

que lo modifique. El circuito tiene “memoria”.

Este tipo de memoria es volátil pues si se desconecta la tensión de alimentación Eb y se vuelve a conectar, no se sabe cual de los dos transistores entrará

en conmutación (siempre que no haya condiciones que favorezcan a alguno de

los dos transistores). Al conectar la memoria habrá que fijar un determinado estado mediante el proceso de escritura.

Si se utilizan señales lógicas, el estado alto H ó "1" equivale a 10 voltios por

ejemplo y el estado bajo L ó "0" equivale a cero voltios.

El circuito puede ser encapsulado (circuito

integrado IC) como se indica el la figura.

Las notaciones empleadas son R (Reset)

para escribir un cero en la salida Q y S (Set)

para escribir un uno en la salida Q.

La escritura siempre se hace con un impulso

positivo.

La salida “ Q ” tiene el valor lógico opuesto al de Q.

Este circuito, con ligeros cambios se verá en Electrónica Digital con el nombre

de Latch.

Multivibrador monoestable (Temporizador)

Tiene un estado estable que es la posición de reposo. Cuando se le saca de

este estado, pasa a otro estado inestable durante un tiempo hasta que alcanza

de nuevo la posición de reposo. El tiempo mientras está en la posición inestable se denomina “tiempo de temporización” que determina su característica

Teoría de la Conmutación V.08

17

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

como bloque (Un monoestable de 2 segundos significa que está 2 segundos

fuera de la posición de reposo cuando se le dispara).

En estado de reposo, el circuito está diseñado para que el transistor T1 esté

conmutado. En estas condiciones, la placa izquierda del condensador C está

aproximadamente a cero voltios (VBE de T1), mientras que la placa derecha

está a Eb.

En un determinado instante, mediante un impulso negativo en la base de T1 se

pasa a la zona de corte a este transistor (también puede hacerse con un impulso positivo en la base de T2, cumpliendo la ecuación de conmutación).

Al pasar a corte el transistor T1, pasa a saturación el transistor T2. La placa derecha del condensador que estaba a Eb voltios, pasa instantáneamente a tener

aproximadamente cero voltios (VCE en saturación). En consecuencia, en la

placa izquierda aparecerán –Eb voltios según la ecuación del condensador.

Esta placa izquierda comenzará a aumentar exponencialmente su potencial

eléctrico hasta el valor +Eb. Pero antes de que se pueda producir este hecho, al

estar la placa formando nudo con la base de T1, pasa por una tensión VBE

capaz de saturar este transistor, produciéndose la conmutación del mismo. De

esta forma se pasa al estado de reposo inicial.

Teoría de la Conmutación V.08

18

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

El tiempo que permanece fuera de la posición de reposo, se calcula, bien

gráficamente o aplicando ecuaciones.

Tiempo de Temporización

Tt = 0.69 CR11

Multivibrador libre ó astable (onda rectangular)

Teoría de la Conmutación V.08

19

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

El circuito está diseñado para tener dos estados inestables. Cuando el transistor T1 está conmutado, el T2 está cortado y viceversa. Los estados se suceden

alternativamente como consecuencia de la realimentación entre ellos.

Las salidas, como en todos los multivibradores, se toman en los colectores.

Cuando T1 está conmutado, la tensión en la base de T2 va creciendo como consecuencia del proceso de carga que tiene lugar en el condensador C1, hasta

que en el momento “t2” se cumplen las condiciones de conmutación de éste

(T2). Un instante anterior a t2, los condensadores C1 y C2 tienen el siguiente

potencial:

Un instante después de t2, con T2 conmutado y T1 cortado como consecuencia

de la tensión negativa que aparece en su base, los potenciales en los condensadores pasan a ser de:

El potencial en la placa izquierda de C2, va creciendo exponencialmente con

C2RB1 hasta que consigue conmutar a T1 en el tiempo “t3”. Siguiendo los

mismos razonamientos en el establecimiento de potenciales en los condensadores, se obtienen las formas de onda a lo largo del tiempo, de forma de los

tiempos de conmutación de los transistores vienen dados por las expresiones

T1

+

T2

T1

T2

T1

OSCILADOR

A

Salida 2

Pérdida aleatoria

de sincronización

FUENTE DE

ALIMENTACIÓN

T1

+ OSCILADOR

B

T2

T1

T2

T1

Salida 2

Teoría de la Conmutación V.08

20

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Si dos osciladores de periodos T1 y T2 se conectan simultáneamente, las formas de onda en sus salidas, por ejemplo la “Salida 2”, estarán desfasadas

pues la respuesta de cada multivibrador en el encendido depende de otros factores que no se han analizado. Este hecho es necesario tenerlo en cuenta en

determinadas aplicaciones donde la sincronización es determinante. En la

práctica es imposible tener dos osciladores idénticos debido a las tolerancias

de los componentes, condiciones ambientales y de trabajo, etc. La estabilidad

en la frecuencia y en la sincronización se realiza con circuitos que analizan las

salidas y aplican las correcciones necesarias en cada momento (no son objeto

de esta asignatura).

Circuito Schmitt-trigger (regenerador de frentes)

Es un multivibrador biestable en el que el cambio de estado sucede en dos umbrales de tensión de la señal de entrada.

El circuito se proyecta de tal forma que en ausencia de señal de entrada, el

transistor T2 esté en conmutación, por lo que (RC1+RB2) ≤ βRC2 (se han despreciado las caídas en el transistor).

Así mismo, es condición necesaria que el valor de la tensión en el emisor común cuando el transistor T2 esté conmutado, sea mayor que el valor que exista

cuando sea T1 el transistor que se encuentre en conmutación. Esta condición

se satisface siendo RC1 > RC2.

De la misma forma, para que T1 pueda estar conmutado,

(Ventr.- VE1)/RB ≥ Eb/β(RC1+RE)

(Se desprecian las caídas en el transistor)

El funcionamiento del circuito es como sigue: una vez conectado el circuito

(+Eb), el emisor estará a la tensión VE2. Por la entrada del circuito se introduce

una señal a la que se pretenden regenerar los frentes de subida y de bajada

(típico en las señales digitales).

Teoría de la Conmutación V.08

21

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Despreciando la caída de tensión que se

produce en la resistencia RB de entrada y

la caída entre base y emisor de T1, el circuito responderá de tal forma que cuando

la señal de entrada supere el valor de VE2

se producirá la conmutación de T1, el cual

permanecerá conmutado hasta que la tensión de entrada no descienda por debajo

de VE1.

Cuando T1 está conmutado, la señal de

salida toma el valor de +Eb, mientras que

cuando está cortado es VE2.

Circuitos OR, AND e Inversor (Puertas lógicas)

Los circuitos que siguen a continuación se encuentran en el apartado 11.3 de

IE-JGBQ.

Teoría de la Conmutación V.08

22

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Suponiendo despreciables las caídas en los diodos y transistores, estos circuitos representan las funciones de “suma lógica” (OR), “producto lógico” (AND)

e “inversión” (INV).

En el circuito OR, la salida es la mayor de las entradas. (Si las dos entradas

fueran negativas, la salida será cero)

Para el circuito AND, la salida es la menor de las entradas. (Si las dos entradas

son mayores que Eb, la salida será Eb)

Finalmente el circuito inversor proporciona una salida alta cuando la entrada es

baja y viceversa.

Si se forma un circuito con una “puerta” OR seguida de un inversor, el circuito

resultante es una NOR. De la misma forma una puerta NAND se obtiene con

una AND seguida de un inversor.

Familias de Circuitos Integrados

Apartado 11.4 de IE-JGBQ.

Teoría de la Conmutación V.08

23

A. Martín

PROBLEMAS DE CONMUTACIÓN

(Febrero 2008)

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 01

Dibujar la señal de salida S(t) del circuito representado, si la señal de entrada

es E(t). A la vista de la respuesta, proceda a enunciar cual será la respuesta

del circuito para cualquier entrada. Así mismo, indique que sucedería si el

diodo no fuera ideal y que se puede decir de la constante rC del circuito.

(Tiempo de realización 25 minutos. Puesto en examen)

Si no se tiene en cuenta la caída de tensión en el diodo, la señal de salida es el

resultado de sumar un nivel de continua positivo a la señal de entrada igual al

valor máximo negativo que se haya presentado a la entrada hasta el momento.

Si el diodo no fuera ideal habría que contabilizar la caída correspondiente a cada potencial (por ejemplo 500 mv + punto de trabajo = 700 mv) con lo que el nivel de continua positivo disminuiría en esta cantidad.

Respecto de la constante de tiempo rC, esta es cero al considerar el diodo

ideal (resistencia interna nula). Por eso la carga del condensador es instantenea.

Problemas de Conmutación V.08

1

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 02

El circuito de la figura representa un generador de dientes de sierra. Para la

señal de entrada que se indica, se pide:

1) Calcular la resistencia de base supuestas despreciables todas las caídas en

el transistor ( β >10)

2) Calcular y dibujar la onda de salida.

3) Determinar la alinealidad.

4) Analizar el caso real (caídas en el transistor, descarga del condensador,

pérdida de conmutación etc.…). ¿Qué sucede con la resistencia de base?.

(Tiempo de realización 25 minutos)

SOLUCIÓN

1) Para calcular la resistencia de base se aplica la ecuación de conmutación. Al

despreciar las caídas en el transistor se plantea

Entrada/Rb Eb/βR

Así pues

3v/Rb10v/10 KΩ

Rb será menor o igual a 3 KΩ (serie comercial del 5%)

2) Cuando la señal de entrada conmuta el transistor, la salida es cero voltios y

cuando la entrada es cero voltios, el transistor está cortado. La salida será la

carga del condensador C a través de la resistencia R.

La constante de tiempo del circuito RC vale 2ms, en consecuencia

t/RC = 1

La tensión que alcanza el diente (Ver curvas de carga o aplicar ecuación) es

0,632 Eb = 6,32 v. (Dibujar la señal de salida)

3) La alinealidad se obtiene fácilmente de la curva de carga, siendo esta del

36,8%.

Problemas de Conmutación V.08

2

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 03

Calcular los valores teóricos de las resistencias y condensador del generador

de dientes de sierra, así como los intervalos de tiempo del tren de impulsos de

entrada de amplitud 6 voltios, para que la salida sea la que se representa.

Datos del transistor: Intensidad de colector máxima 4 mA , β>50, siendo despreciables las caídas de tensión.

Tensión de alimentación Eb = 12 voltios.

(Tiempo de realización 25 minutos)

Los intervalos del tren de impulsos de entrada vienen determinados por la señal de salida. El transistor estará conmutado 0.1 ms. y en corte durante el internalo de 1 ms.

Al conocer la tensión de alimentación y el valor de tensión máximo del diente

de sierra, se conoce la constante de tiempo de carga del condensador C a través de la resistencia Rc mediante la expresión:

sustituyendo valores

se obtiene CRc = 1.14 ms

Por otro lado, la resistencia Rc está acotada por un valor mínimo al estar limitada la intensidad en el transistor a un valor de 4 mA, Rc(mín) ≥ Eb/Imáx (al despreciar pérdidas en el transistor)

Rc(mín) ≥ 12v/4 mA = 3 KΩ

Con lo que el condensador será de

0.38 µ F (≥12v)

Problemas de Conmutación V.08

3

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

“Lo que viene no forma parte del ejercicio, se piden valores teóricos”.

Para adaptar la solución a valores comerciales,

http://www.micropik.com/provisional/pag_cond_cer.htm

CMC330NF

Condensador cerámico 330 nF (0,33µF) 50V 5% tol

Con este condensador la resistencia comercial será de 3.48 KΩ 2% (Ver la tabla series de

resistencias normalizadas de Clase 02 de Conmutación

Para ajustar perfectamente, se retoca el valor de capacidad sin más que poner en paralelo un

trimmer a fin de obtener la constante de tiempo de 1.14 ms.

Para terminar el cálculo de componentes, hay que determinar la resistencia de

base Rb. Despreciando las pérdidas en el transistor

Entrada/Rb ≥ Eb/βRc

6v/Rb ≥12v/50 x 3 KΩ

Rb = 75 KΩ

(Este comentario tampoco se pide) Si la resistencia de colector elegida hubiese sido la de 3.48

KΩ 2%, el valor de la resistencia de base sería de 87 KΩ (8.66 KΩ). Así como la resistencia Rc

determina valor máximo de diente de sierra, la resistencia de base solo controla la conmutación,

por lo que económicamente no se suele bajar del 5% por lo que el valor a tomar sería de 82 KΩ

y 5%.

Problemas de Conmutación V.08

4

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 04

Diseñar el circuito que representa un generador de dientes de sierra, dibujando

el tren de impulsos de entrada (amplitud de impulsos, ancho y distancia entre

impulsos) para que la señal de salida sea la representada. Calcular el valor de

la tensión de alimentación (Eb), en el caso de que EC valga 10 voltios.

Determinar las características de los componentes teniendo en cuenta que la

máxima intensidad que va circular por el colector (debido a la carga) es 5 mA.

Despreciar pérdidas en el transistor.

(Tiempo de realización 25 minutos)

De la alinealidad se obtiene la ecuación

E – Ec = 0.1 E $ Ec = 0.9 E

De la pendiente en el origen en su corte con la asíntota

E/T = Eb/RC $ T/RC = E/Eb

Sustituyendo en la ecuación de carga del condensador

para t = T

Problemas de Conmutación V.08

5

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Haciendo E/Eb = z

0.9 z = 1 – e-Z

Para z <1, desarrollando en serie de Taylor la exponencial y despreciando términos de orden superior, se obtiene en primera aproximación:

Z = 0.2

Con lo que se obtiene el valor de Eb = E/0.2 = Ec/0.18 = 55.6 v

Eb = 55.6 v

Como también z = T/RC

RC = T/0.2 = 5 ms

Al estar R acotado por la Imáx del transistor

Rmín = Eb/Imáx ; Rmín = 11.1 KΩ

Y el condensador

C = 450 nF >55.5 v

Aunque en régimen de trabajo el condensador se carga hasta 10 voltios, pudiera suceder que por ausencia de pulsos de conmutación (fallo), el condensador

se cargase al valor final de la tensión de alimentación, motivo por el que debe

de soportar una tensión mínima de trabajo de más de 55.5 voltios.

Finalmente, la resistencia de base, se determinará dependiendo del transistor

elegido. Los requisitos que debe de cumplir serán que la tensión VCEO > 55,5 v

con una intensidad de colector mínima de 5 mA. Una vez elegido, se obtendría

el β, a partir del cual se calcularía Rb.

Problemas de Conmutación V.08

6

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 05 (Examen 06.09.99)

Determinar las señales de salida S1 y S2 de los circuitos que se representan,

para las señales de entrada A, B, y C (amplitud/tiempo).

Se despreciarán las caídas en los diodos.

Los valores de tensión, en voltios, están referidos a tierra

T1

T2

T3

T4

T5

T6

A

8

-2

15

5

-3

2

B

1

3

12

-7

-5

5

C

5

0

11

10

-6

-3

S1

8

3

15

10

0

5

S2

1

-2

10

-7

-6

-3

Los valores en rojo son consecuencia de las incompatibilidades con la

alimentación.

Problemas de Conmutación V.08

7

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 06

Determinar las señales de salida S1 y S2 de los circuitos que se representan,

para las señales de entrada A, B (amplitud/tiempo).

Suponer una caída de “1 voltio” en los diodos cuando conduzcan.

Los valores de tensión, en voltios, están referidos a tierra.

T1

T2

T3

T4

T5

A

5

0

5

2

0

B

2

2

5

5

0

S2

6

1

6

3

1

S1

3

1

4

4

0.5

SOLUCIÓN:

Se trata de un problema de bastante dificultad como consecuencia de la

resistencia que tiene el terminal conectado a tierra.

Los puntos A, B y +9 v, son puntos de generador ideal por lo que son tensiones

fijas invariables. (3.6 IE JGBQ).

Problemas de Conmutación V.08

8

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Los diodos ideales con 1 voltio de caída, conducen en un único sentido, pudiendo circular por ellos toda la intensidad que se requiera (pendiente infinita,

sin rotura) al aplicar las Leyes de Kirchoff a los nudos (3.7 IE JGBQ).

Al ser las entradas positivas respecto a tierra, la tensión en los dos nudos sienpre será mayor que cero, por lo que I3 tendrá el sentido que se indica.

Al ser también inferiores a 9 voltios, I1 deberá de tener el sentido indicado.

La I2 podrá ser en un sentido ú otro, incluso nula, dependiendo de las entradas.

Por último, cuando un diodo conduzca, al tener un terminal conectado a un

generador, cumplirá su ecuación haciendo que el otro terminal deba de tener el

potencial necesario.

Las soluciones en consecuencia, al no plantear ecuaciones, deberán de ser

coherentes.

Tiempo T1:

Si en A hay 5v, en el nudo superior, en adelante nudo 1, deberá de haber 6v. Al

haber en B 2v, podría haber en el nudo inferior, en adelante nudo 2, 1v. Si

suponemos que el valor de las resistencias es de 1 Ω, la I2 valdría 5A y la I3 1A,

hecho a todas luces incoherente. La única solución es que el diodo en B no

conduzca, con lo que la tensión en el nudo 2 es de 3v, haciendo que I2 = I3 =

3A.

Tiempo T2:

Si en A hay 0v, en el nudo 1 habrá 1v. Si en B hay 2v, en el nudo 2 habrá 1v,

en consecuencia I2 = 0A, I1 = IA = 8A e IB = I3 = 1A.

B

Los demás tiempos se analizan de la misma manera comprobando la

coherencia de las intensidades en los nudos, es decir, si I2 es hacia abajo, I3

deberá de ser mayor o igual. Si I2 es hacia arriba, IA debe de existir.

Problemas de Conmutación V.08

9

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 07 (Examen 26.06.00)

Determinar las señales de salida S1 y S2 de los circuitos que se representan,

para las señales de entrada A, B, C y D (amplitud/tiempo).

Se despreciarán las caídas en los diodos.

Los valores de tensión, en voltios, están referidos a tierra.

T1

T2 T3 T4 T5 T6 T7 T8 T9

A

15

5

0

12

5

5

0

15

0

B

12 12

2

12

2

0

0

12

0

C

15 15

0

12

1

3

3

3

0

D

12 12

1

12

0

5

5

5

0

5

0

11

2

0

0

10

0

S1 15 15

1

12

2

5

5

10

0

S2 12

SOLUCIÓN:

Este problema es muy sencillo, por lo que solo se analizan los casos que tienen

una pequeña dificultad.

Tiempo T5:

La conducción de C ó D obliga a que la intensidad vaya del nudo inferior al

superior. Como en el nudo superior hay 2v, no es posible la conducción de C ó

D, con lo que la tensión en el nudo 2 será de 2v (circuito abierto).

Tiempo T8:

Ninguno de los diodos conduce, con lo que S1 = S2 = 10v

Problemas de Conmutación V.08

10

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 08 (Examen del 22.6.98)

Para el circuito Schmitt de la figura, suponiendo despreciables todo tipo de caídas de tensión en los transistores y β = 40, se pide:

1º) (5 puntos) Dibujar la señal de salida, con sus valores característicos, para la señal de entrada representada.

Problemas de Conmutación V.08

11

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Los valores de las tensiones umbral, vienen determinados por

Tensión de emisor con T2 conmutado VE2 = 12(300/400) v = 9 v

Tensión de emisor con T1 conmutado VE1 = 12(300/900) v = 4 v

Cuando T2 esté conmutado, la salida valdrá 9 v y cuando esté T1 será de 12 v.

Representamos estos datos en valores y dibujamos la señal de salida.

2º) (3 puntos) Calcular el valor de todas las intensidades, así como las tensiones umbral, rellenando la tabla adjunta.

Las tensiones umbral han sido calculadas con anterioridad para dibujar la respuesta. En cuanto a las intensidades cabe distinguir dos casos

T1 Saturación T2 Saturación Unidades

I1

13

3

mA

I2

0

30

mA

I3

0

3

mA

I4

13

30

mA

VE

4

9

v

a) El transistor T1 está conmutado

I2 = I3 = 0

I1 = I4 = 12 v/900 Ω = 13 mA.

b) El transistor T2 está conmutado

I2 = I4 = 12 v/400 Ω = 30 mA.

I1 = I3 = (12-9) v/1000 Ω = 3 mA

3º) (2 puntos) Realizar los comentarios que procedan respecto de la resistencia R0 así como lo que sucedería con las “tensiones umbral” si se consideraran

pérdidas en la base de T1 del orden de 0.7 v

Comentarios R0:

Problemas de Conmutación V.08

12

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Una vez que la señal de entrada supere el valor de 9 v, despreciando pérdidas,

conmutará el transistor T1 y para que mantenga la conmutación, I0≥I1/β, que

sustituyendo da un valor de 325 µA lo que producirá una caída mayor de I0R0 =

3,25 v lo que daría en principio una falta de conmutación de T1, pero como al

conmutar la tensión de emisor pasa a 4 v, resulta que tiene en principio esa posibilidad de conmutar de forma real.

Desde el punto de vista del diseño, la resistencia es alta y debería de estar por

debajo de 1 KΩ para estar en el orden (0.3 v) de caída de transistor o de 100Ω

(0,03 v) para poder despreciar la caída en esta resistencia.

Como al conmutar T1 la tensión de emisor es de 4 v, todo el exceso de tensión

será absorbido por caída en R0 y por la resistencia Base-Emisor de T1.

Si se tienen en cuenta las caídas, las tensiones umbral quedan modificadas de

forma que aumentan en el valor que constituye la caída VBE de T1.

Problemas de Conmutación V.08

13

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 09 (Examen del 01.09.00)

Dibujar las formas de onda en las salidas S1 y S2 para las entradas A y B que

se indican. Suponer que β>100 y que las caídas en los transistores son despreciables. Indicar todos los valores característicos en número así como las

constantes de tiempo cualitativas de cargas y descargas

SOLUCIÓN:

Para los valores de tensión de las entradas, cuando hay 10 voltios el transistor

conmuta (β>100) y cuando 0 voltios está cortado (comprobar).

Problemas de Conmutación V.08

14

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Problema 10 (Examen del 26.06.00)

Dibujar las formas de onda en las salidas S1 y S2 para las entradas A y B que

se indican. Suponer que β>100 y que las caídas en los transistores son despreciables. Indicar todos los valores característicos en número así como las constantes de tiempo cualitativas de cargas y descargas

SOLUCIÓN:

Cuando T1 esté conmutado, T2 estará abierto (cortado) con lo que la señal en

S2 estará a cero o será exponencial dependiendo de cómo se encuentre T3

(conmutado o abierto respectivamente).

Cuando T1 este abierto, T2 estará conmutado con lo que la señal en S1 será

cero y la de S2 cero o descargando a través de T3 ó T2 según sus estados.

Problemas de Conmutación V.08

15

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

PROBLEMA DE APLICACIÓN

Obtener el tren de pulsos de ralentí necesario para manejar la bobina de un inyector de un motor mono cilíndrico de 4T según los apartados que se indican.

(Sistema de inyección intermitente. El inyector electrónico se activa mediante la

señala eléctrica recibida de la unidad de mando y se cierra por recuperación de

un muelle o resorte interior) Para mas información dirigirse a la dirección

http://www.canbus.galeon.com/motor/organigrinyecc.htm

http://www.iespana.es/mecanicavirtual/inyecci-gasoli-intro.htm

Se pide:

1º) Diagrama de bloques del sistema capaz de proporcionar la señal de inyección. (Un bloque se representa mediante un rectángulo, con entradas y salidas,

cuya denominación es el nombre del circuito electrónico. No se podrán utilizar

circuitos no estudiados hasta el momento).

2º) Características de cada bloque, especificando amplitudes, tiempos, etc.…

3º) Dibujar el circuito electrónico con todos sus componentes. Especificar los

criterios de diseño.

Problemas de Conmutación V.08

16

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

SOLUCIÓN:

1º) Diagrama de bloques

2º) Características

Lo importante es el tiempo de sincronismo, que lo marcaremos con el frente de

bajada del multivibrador libre. (Recordar que el frente de subida es exponencial

y en la formación de pulsos puede general impulsos de poca amplitud).

Problemas de Conmutación V.08

17

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

El multivibrador libre estará caracterizado exclusivamente porque la suma de

tiempos sea de 10 ms. Dará amplitud de alimentación, que por comodidad se

fijará en 12 voltios.

El inversor no tiene ninguna característica ya que está puesto para transformar

los frentes de bajada en frentes de subida antes de entrar en el conformador de

pulsos.

De la misma forma el conformador, que dará pulsos positivos, deberá de ser de

constante de tiempo muy pequeña y que vendrá fijado por la tolerancia del

pulso de 0.6 ms. Si fuera del 1% sería del orden de 6 µs. A medida que este

valor baje las técnicas diferenciales (RC) se hacen críticas en amplitud por su

forma y hay que recurrir a técnicas de retraso de propagación (ns).

Los multivibradores monoestables, alimentados a 12 v, tendrán la particularidad

de los tiempos de temporización y la salvedad en el de 3 ms de poner una resistencia en el emisor para que la salida sea 6 v ó bien, no poner la resistencia

de emisor y colocar un divisor de tensión en su salida.

Recordar que los tiempos en los multivibradores vienen dados por la expresión

RC Ln2, con lo que se procedería al diseño.

Se deja al alumno la elección de componentes y la curiosidad de montarlo en el

Laboratorio a fin de comprobar su funcionamiento.

Problemas de Conmutación V.08

18

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

PROBLEMA DE APLICACIÓN DE LA TEORÍA DE CONMUTACIÓN:

Obtener el código de interrogación formado por los pulsos P1 y P3 con

una frecuencia de repetición fR variable.

Este ejercicio tiene por objeto obtener la señal moduladora en toda su

extensión (modo, frecuencia de repetición y cadencia de modo), representando el diagrama de bloques con sus características determinantes y circuitos electrónicos,

basados exclusivamente en la teoría de conmutación, y determinación específica de los componentes que fijan las características de

la señal.

Introducción: el radar de vigilancia (MSSR Monopulse Secondary Surveillance

Radar) para el espacio aéreo, interroga (enlace ascendente) a las aeronaves

para conocer su indicativo (identificación) y altura de vuelo, proporcionando al

controlador aéreo la posición de cada una de ellas cuando envían la respuesta

(enlace descendente) Doc. 9684-AN/951

Para este fin interroga (enlace ascendente) con una señal modulada en amplitud (AM) de frecuencia 1030 MHz y cuya señal moduladora es el código de

interrogación que se pide en el enunciado. Hay distintos códigos. Para el tráfico

aéreo civil se utilizan el Modo A (Indicativo) y el Modo C (Nivel de vuelo: altura

de vuelo expresada en centenares de pies ó FL). Recientemente, en determinadas regiones de vuelo instrumental (IFR) se han adoptado otro modo a fin de

mejorar los anteriores (mayor capacidad y seguridad en el espacio aéreo). Es

el Modo S implantado, entre otros, en la Unión Europea.

La señal moduladora consiste en un par de pulsos (P1 y P3) separados en función del modo de interrogación, que se repiten cada cierto tiempo (frecuencia

de repetición de interrogaciones) normalmente diferente para cada estación radar (cobertura multiradar). El modo de interrogación es el mismo en cada giro

completo de la antena de exploración (~ 15 rpm) pero varía de unas vueltas a

otras. La cadencia en los modos de interrogación puede ser AAC, AC, ACC, etc.

(en AAC se interroga 2 vueltas en Modo A y una vuelta en Modo C y a sí

sucesivamente). Estas cadencias están en función del tráfico aéreo de la zona

y del momento (por ejemplo en las proximidades a un aeropuerto, donde hay

continuos despegues y aterrizajes, interesa conocer con más frecuencia la altura que el indicativo, con lo que se utiliza una cadencia ACC).

Problemas de Conmutación V.08

19

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

SOLUCIÓN:

La realización de las aplicaciones se resuelve normalmente empezando por el

final.

La señal moduladora es periódica al estar caracterizada por el periodo de repetición de TR, pero no lo es dentro del periodo. Para obtener la señal es necesario, normalmente, partir de señales totalmente periódicas de forma que al combinarlas por medio de sumas ó productos lógicos e inversiones se genere el resultado deseado.

Teniendo en cuenta este razonamiento, se utiliza una señal de anchura P1 y

periodo TR que se combina con otra de anchura P3 y periodo TR, sincronizadas

de tal forma que la segunda esté retrasada según el Modo.

El ancho de P1 es idéntico al de P3, por lo que el bloque que genera la señal de

ambos es el mismo, variando el momento del disparo. Este bloque es un multivibrador mono estable cuyo tiempo de temporización es de 0.8 µs y cuya salida

se toma en el colector del transistor que genera la onda perfectamente rectangular. (Módulo P1P3)

Tiempo “t0“ de referencia

P1

M. Monoestable

T = P1 = P3

S

u

m

a

“t0“

Entrada de disparo

“tM“

P3

M. Monoestable

T = P1 = P3

“t0“

Entrada de disparo

“t0“

L

ó

g

i

c

a

“t0“

“tM“

Salida

“tM“

Los impulsos que disparan los M. Monoestables se generan con el circuito

electrónico llamado “conformador de impulsos” ya utilizado en prácticas (es un

diferenciador para onda cuadrada, seguido de un rectificador y un seguidor de

emisor). Se necesita pues generar un impulso en “t0” y otro en “tM”.

Las referencias para establecer la sincronización están definidas por “t0” que en

principio es arbitrario y por “tM” que está retrasado en función del Modo de interrogación. Es un tiempo que tiene dos ligaduras, una respecto de t0 y otra el retraso del tipo de modo. Como el retraso en el tipo de modo tiene la referencia

de t0 son necesarios dos multivibradores monoestables con tiempo de temporización dados por TMA = 8 µs y TMC = 21 µs disparados por la referencia “t0”. Los

Problemas de Conmutación V.08

20

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

frentes de bajada de las señales de estos dos M. Monoestables esta-rán a 8

µs y 21 µs. La elección de uno ú otro dará la referencia “tM”. (Módulo de

Referencias tMA / tMC).

Como el impulso en “tM” tiene que ser seleccionado mediante la “Cadencia de

Modo” es necesario antes de generar el impulso seleccionar el Multivibrador de

TMA ó el de TMC. Este circuito es un “selector de dos canales” (multiplexor de

dos canales).

El circuito de cadencia de modo dará salida alta en Modo A y baja en Modo C,

produciéndose el cambio en el momento en el que la antena pasa por una marcación preestablecida, por ejemplo el Norte Magnético de la estación. Para evitarles alguna complejidad, digamos que es un interruptor de doble vía que da

10 voltios ó 0 voltios (Valores de continua que proporcionará la Fuente de Alimentación de todo el conjunto).

El selector de canales se realiza mediante un inversor, dos productos lógicos

para dos entradas y un sumador lógico de dos entradas:

Modo A

Modo C

10 v

0v

Cadencia de Modo

Inversor

Producto Lógico

de dos entradas

Salida Monoestable

de Modo C

Salida Monoestable

de Modo A

Producto Lógico

de dos entradas

S

u

m

a

L

ó

g

i

c

a

Si está activado el Modo A, la salida del inversor es “0 voltios” deshabilitando

en la entrada superior del sumador lógico la señal de salida del monoestable

Modo C (poner cero voltios) . En la entrada inferior del sumador está la señal

del Monoestable Modo A, pues la salida de un producto lógico es la menor de

las entradas compatible con la alimentación.

Problemas de Conmutación V.08

21

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Cuando se activa el Modo C, la salida del inversor es “10 voltios” habilitando en

la entrada superior del sumador lógico la señal de salida del monoestable Modo

C. En la entrada inferior está deshabilitada la señal del Monoestable Modo A,

pues la salida de un producto lógico es cero.

En la salida del sumador lógico estará la señal del monoestable Modo A ó la

del monoestable Modo C. Esta señal ya se puede pasar al conformador de impulsos. Se coloca un inversor entre ambos bloques para obtener impulsos positivos con el frente de bajada.

TMA

“tMA“

TMA

“t0“

“t0“

“t0“

Conformador

de Impulsos

Inversor

Salida Sumador Lógico

Modo C

Para establecer la referencia “t0” que falta es necesario conocer si tiene alguna

ligadura. Si necesitase estar sincronizada con alguna referencia de tiempo

(tiempo común a todas las estaciones radar, tiempo universal coordinado, tiempo GPSt, etc. ) tendría que ser suministrado. En el ejemplo de aplicación es

arbitraria: cada estación radar envía los datos correspondientes a los blan-cos

detectados con una etiqueta del tiempo en el que se producen (plots); en el

centro de Control de Tráfico Aéreo (ATC) se tratan los plots de un determinado

blanco provenientes de las distintas estaciones radar para presentar al controlador aéreo la posición en tiempo real del blanco identificado (pista radar).

Para generar la referencia “t0” arbitraria, pero variable al serlo la frecuencia de

repetición asignada a la estación radar (incluso por determinados motivos la estación puede tener fR variable), se necesita un oscilador de onda cuadrada de

frecuencia "fR", que se pasa por un diferenciador para obtener los impulsos positivos que fijan la referencia “t0”. El oscilador de onda cuadrada es un

multivibrador libre de periodo de repetición TR. (Módulo de Referencia t0).

“t0“

“t0“

“t0“

“TR“

“TR“

“TR“

Referencia t0

Multivibrador

Libre ó Astable

Conformador

de Impulsos

Inversor

El diagrama de bloques completo especificando las características más

importantes será:

Problemas de Conmutación V.08

22

A.Martín

Problemas de Conmutación V.08

23

Inv

Cadencia

de Modo

Inv

Producto

Lógico

Conformador

de Impulsos

Amplificador

1030 MHz

Módulo de RF

Inv

Módulo

de Referencias

tMA / tMC

Conformador

de Impulsos

ANTENA

Σ

Multiplexador

Producto

Lógico

ARP Pulsos de Revolución de Antena

Monoestable

T = TMA

Monoestable

T = TMC

Módulo tM

Multivibrador

Libre ó Astable

"TR" variable

Módulo de Referencia t0

Sintetizador

(Oscilador)

1030 MHz

Modulador

AM

Monoestable

T = P1 = P3

Σ

Monoestable

T = P1 = P3

Módulo P1P3

Señal

Moduladora

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

DIAGRAMA DE BLOQUES DEL INTERROGADOR MSSR

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Una vez obtenida la señal moduladora, pasa a un modulador de AM donde se

añade la señal portadora de 1030 MHz obtenida de un sintetizador de frecuencia (oscilador). Se amplifica y se envía a la antena de exploración. En la antena

existen sensores que determinan el apuntamiento del diagrama de radiación,

DDR, velocidad de giro, indicador de norte magnético NM y/o geográfico para

detectar giros completos (ARP: Antenna Revolution Pulse ), etc.

A continuación se describen los módulos con los circuitos completos y

características fundamentales:

Módulo de referencia “t0”. La característica es la frecuencia de repetición “fR”

variable. El periodo de repetición TR es la suma de los tiempos T1 y T2 de un

multivibrador Libre ó Astable. Lo más aconsejable es que sea simétrico (T1=T2).

Como fR tiene que poder ser variable, algún componente que determine el periodo de oscilación deberá de cubrir los márgenes para la frecuencia de repetición.

T1 = 0.69 C1RB2

T2 = 0.69 C2RB1

Tomando RB2 = RB1 = RB fijadas por el ecuación de conmutación, serán las capacidades las que fijen el valor de TR. En la figura se ha representado C1 como

el paralelo de dos condensadores, uno fijo C y otro variable CV (Banco de condensadores en paralelo seleccionados mecánica ó electrónicamente). Si C2 se

hace igual a C, la ecuación para fR será:

TR = 0.69 RB (2C + CV)

B

Supuesto, RB = 10 KΩ; sería C = (133 nF + 360 pF + Trimmer de 7-100 pF) y

CV un conjunto paralelo de 6 condensadores de (6,8 nF + 402 pF + Trimmer de

7-100 pF) cada uno. Con estos valores el periodo de repetición variará entre

1850–2150 µs en pasos de 50 µs, que cubre los ~2 ms de proyecto. (los

trimmers se utilizan para la calibración de fR). Tanta precisión es necesaria por

necesidades propias del MSSR.

http://www.micropik.com/provisional/pag_condensadores.htm

http://www.micropik.com/provisional/pag_cond_trim.htm

Problemas de Conmutación V.08

24

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

El inversor y el conformador de impulsos no tienen ninguna característica especial que los diferencia de los utilizados en prácticas. Solo se necesita tener la

suficiente energía para disparar los monoestables a los que ataca. Otra posibilidad se encuentra resuelto en el ejercicio de aplicación del los inyectores.

Módulo “tM”.

Está constituido por dos multivibradores monoestables con tiempos de temporización de

TMA = 8 µs y TMC = 21 µs.

Como la ecuación de tiempo es

T = 0.69 R11C

y supuesto R11 fijado por condición

de conmutación (10 KΩ), la capacidad para el Modo A sería de

1.16 pF (picofaradios) y para el Modo C de 3.04 pFque se realizarían con dos

capacidades paralelo para poder ajustar al valor exacto, similar a lo tratado en

fR (la precisión de estas capacidades no es tan crítica).

Módulo P1P3

Compuesto por dos monoestables idénticos (disparados en momentos distintos) y un sumador lógico. La característica a definir es el tiempo de temporización dado por T = 0.69 R11C. Como en otros casos, si la resistencia que se elije

es de 10 KΩ, para que T = 0.8 µs, deberá de ser C = 116 nF.

En todos los módulos las capacidades de los condensadores van ligadas a una

tensión de trabajo que sería en los casos mas desfavorables la de alimentación

en fallo, es decir la tensión pico del secundario del transformador empleado.

Por ejemplo, si la tensión continua son 12 voltios, es bastante normal la

elección de una tensión de trabajo para los condensadores de 24 voltios

(aunque depende de los criterios de diseño de la fuente).

En cuanto a las resistencias empleadas, su consumo siempre estará por debajo del vatio, por lo que no hay que tomar ninguna media especial.

En cuanto a los transistores se pueden utilizar los 2N2219, de β > 10; VCEO =

30 v, IC = 800 mA y efecto Zener en 5 voltios. Todos los requisitos los cumplen

y la resistencia en los colectores deberá de ser mayor a 1KΩ para que las intensidades de base puedan conmutar los transistores. En los diseños se ha

partido de RB’s de 10 KΩ.

Problemas de Conmutación V.08

25

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Para finalizar, los diodos serán de baja señal, por lo que no tienen nada de

especial.

Módulo Multiplexor (Multiplexador):

Cadencia de Modo

Modo C

Modo A

+

+

+

de la Salida

Modo C

+

de la Salida

Modo A

Nota: nF (nanofaradio) = KpF = 10-9 F (faradios)

pF (picofaradio) = 10-12 F

Comercialmente es bastante frecuente la confusión entre µF y mF. Para abreviar microfaradio emplean la unidad de milifaradio erróneamente.

FIN

Problemas de Conmutación V.08

26

A.Martín

EXÁMENES DE CONMUTACIÓN

(Febrero 2009)

A. Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

24.06.05

40 Minutos Hoja 1 (Test y Problema)

Test de Conmutación. Solo una respuesta es correcta. Correcta 1 punto, blanco 0

puntos e incorrecta -0.5, puede dar negativa y hace media con el problema.

.

1º) Si la constante de tiempo de un generador de diente de sierra sin linealizar es de un

segundo, se puede afirmar que la alinealidad expresada en tanto por uno es

< 0,2 al cabo de 1 seg.

> 0,3 al cabo de 1 seg.

< 0,02 al cabo de 0,5 seg.

Otros, especificar

Solución: Para t/RC = 1 la alinealidad es aprox. 0,37 > 0,3. >0,3 al cabo 1 seg,

2º) Suponiendo una caída de 0,5 v. en los diodos cuando están en conmutación, que la

tensión en el punto A respecto a tierra es VA = 4 v y en el punto VB = 3 v, la caída de

tensión VCD vale:

3 v.

2 v.

-1 v.

Otra, especificar

Solución: Si en A hay 4 v el diodo DA conmuta con una caída de 0.5 v,

lo que obliga a tener en C una tensión de 4.5 v respecto a tierra (en D

podría haber 2.25 v). Como en B hay 3 v conmuta por la referencia de

tierra, obligando al punto D a estar a un potencial de 2,5 v. Basta comprobar la coherencia de las intensidades en el nudo inferior. Así pues

VCD = VC – VD = 2 v

3º) En un generador de diente de sierra, el condensador de 1000 μF se carga en 1 seg a

la tensión de 7 v. aproximadamente, siendo Eb = 11 v. Si β=10 ¿qué se puede afirmar

de la resistencia de base si el tren de pulsos varía entre 0 y 5 v y se desprecian todas

las caídas en el transistor?:

2,2 KΩ < RB < 3,3 KΩ

15 KΩ < RB < 22 KΩ

33 KΩ < RB < 47 KΩ

RB > 47 KΩ

Solución: La relación V/Eb = 7/11 = 0,64 aproximadamente, lo que coincide con t/RC = 1

(V/Eb = 0,63). Como sucede para t = 1 s, RC = 1 s, la resistencia de carga del colector

vale 1 KΩ. Al ser β=10, Eb = 11 v y VEntrada = 5 v, la resistencia de base debe de ser

menor ó igual a 4,5 KΩ. (Plantear la ecuación general y despreciar caídas)

Exámenes de Conmutación V.09

1

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

4º) En un inversor, la resistencia de colector vale 1,2 KΩ. Si en el límite de la conmutación, la intensidad de base es de 10 mA con β=10, se puede decir:

RB> 12 KΩ

IC = 0.1 A.

Eb = 12 v.

Otros, especificar:

Solución: La intensidad de colector en el límite de la conmutación será IC = βIB, es decir

100 mA, por lo que despreciando las caídas de tensión en el transistor, determina el

valor de la tensión de alimentación Eb = RC.IC = 1,2 KΩ. 100 mA = 120 v. Solución IC =

0,1 A.

B

5º) En el circuito de la figura, el tiempo de temporización vale aproximadamente:

0,4 ms (milisegundos)

1 ms

2 ms

3 ms

Solución: En transistor T1 está conmutado en posición de reposo. Cuando se le saca de ésta, permanece un tiempo fuera de ella que viene determinado

por el valor

4,7 KΩ. 330 Kpf. Ln2 = 1 ms

2º) (5 Puntos) Problema de conmutación

a) Dibujar el circuito Schmitt, especificando entrada, salida y componentes.

b) Suponiendo despreciables todo tipo de caídas de tensión en los transistores, β>100,

Eb = 15 v, RE = 600 Ω, RB1 = RB2 = 4,7 KΩ, tensiones umbral VE2 = 10 v,

VE1 = 5 v, se pide determinar los valores óhmicos teóricos de las resistencias de

colector R1 y R2, así como la caída de tensión en RB1 en el momento de la conmutación.

Los valores obtenidos se indicarán en el circuito.

c) Dibujar la señal de salida, suponiendo despreciable la caída de tensión en RB1.

Exámenes de Conmutación V.09

2

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

SOLUCIÓN:

a)

b) Cálculo de las resistencias:

VE2 = Eb.RE/(RE + RC2);

10 v = 15 v . 600 Ω / (600 Ω + RC2); RC2 = 300 Ω

VE1 = Eb.RE/(RE + RC1);

5 v = 15 v . 600 Ω / (600 Ω + RC1); RC1 = 1,2 KΩ

En el momento de conmutación de T1, la intensidad a través de su colector vale ICT1 =

Eb/( RE + RC1) = 15 v/1800 Ω = 8,3 mA; por lo que la IB1 en ese momento será menor

que 83 μA (al ser β>100). Despreciando la VBE en la conmutación de T1 (por enunciado),

la caída de tensión en la resistencia RB1 será de

IB1 . RB1 = 83 μA . 4,7 KΩ = 400 mV

Suponiendo despreciable la caída en la RB1 así como la VBET1, la señal de salida será:

Exámenes de Conmutación V.09

3

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

07.06.06

30 Minutos Hoja 1 (Test y Problema)

1º ) Test de Conmutación (de -5 a + 5 Puntos). Solo una respuesta es cierta.

Correcta 1 punto, Blanco 0 puntos e incorrecta -0,5. Puede dar negativo que hace media

con el problema.

.

a) Si la constante de tiempo de un generador de diente de sierra sin linealizar es de un

segundo, se puede afirmar que la alinealidad es:

< 0,3 al cabo de 1 seg.

< 0,2 al cabo de 1 seg.

> 20% al cabo de 5 seg.

< 5% al cabo de 5 seg

Para t/RC = 1 la alinealidad en 1 seg es aprox. 0,37 y en 5 seg. mucho mayor. Solución

correcta: > 20% al cabo de 5 seg

b) Suponiendo una caída de 1 v en los diodos cuando están en conmutación, que la tensión en el punto A respecto a tierra es VA = 4 v y en el punto VB = 6 v la caída de tensión

VCD vale:

3 v.

2 v.

-1 v.

Otra, especificar VCD = VC – VD = 0 v

Si en A hay 4 v el diodo DA conmuta con una caída de 1 v, lo que obliga

a tener en C una tensión de 5 v respecto a tierra (en D podría haber 2,5

v). Como en B hay 6 v conmuta por la referencia de tierra, obligando al

punto D a estar a un potencial de 5 v. Así pues VCD = VC – VD = 0 v

c) En un inversor, la resistencia de colector vale 470 Ω. Si en el límite de la conmutación,

la intensidad de base es de 100 mA con β=10, se puede decir:

RB> 4,7 KΩ

IC = 4,7 A.

Eb = 470 v.

Otros, especificar:

La intensidad de colector en el límite de la conmutación será IC = βIB, es decir 1 A, por

lo que despreciando las caídas de tensión en el

transistor, determina el valor de la tensión de

alimentación Eb = RC.IC = 470 Ω. 1A = 470 v

d) En el circuito de la figura, el tiempo de temporización vale aproximadamente:

3,3 ms (milisegundos)

3,3 μs

3,3 s

Otros, especificar: 1 ms

Exámenes de Conmutación V.09

4

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

El transistor T1 está conmutado en posición de reposo. Cuando se le saca de esta posición permanece un tiempo fuera de ella que viene determinado por el valor

4,7 KΩ. 330 Kpf. Ln2 = 1 ms

e) En un generador de diente de sierra, el condensador de 100 μF se carga en 1 seg a

la tensión de 7 v aproximadamente, siendo Eb = 11 v. Si β=5 ¿qué se puede afirmar de

la resistencia de base si el tren de pulsos varía entre 0 y 11 v y se desprecian todas las

caídas en el transistor?:

RB > 47 KΩ

47 KΩ < RB < 470 KΩ

RB < 47 KΩ

RB > 4,7 KΩ

La relación V/Eb = 7/11 = 0,64 aproximadamente, lo que coincide con t/RC = 1 (V/Eb =

0,63). Como sucede para t = 1 s, RC = 1 s, la resistencia de carga del colector vale 10

KΩ. Al ser β=5, Eb = 11 v y VEntrada = 11 v, la resistencia de base debe de ser menor ó

igual a 50 KΩ. (Plantear la ecuación general y despreciar caídas).

2º) (5 Puntos) Problema

de conmutación

Dibujar la señal de salida S(t), indicando los valores de

tensión, cuando la señal de entrada E(t) es la que se

representa. El diodo tiene una caída de tensión para

conmutar de 1 voltio, con una resistencia interna "r" en

conmutación de 0 Ω (ideal). El condensador tiene una

carga en t = 0 al ser E(0) = 0. Situar el eje S(t) = 0.

SOLUCIÓN:

Para t = 0 la salida está a -2 v, encontrándose cargado el condensador, memorizando

una diferencia de potencial de 2v. El circuito es un restablecedor automático que va incorporando un nivel de tensión negativo a la señal de entrada. Los niveles se modifican

como se representan a continuación:

Exámenes de Conmutación V.09

5

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

Al llegar a la traza roja, la tensión en la entrada crece linealmente con lo que no se produce picotazo como en los dos picos iniciales. Las descargas son instantáneas al ser

nula la resistencia interna del diodo.

18.09.04

25 Minutos Hoja 1

Circuito Schmitt-trigger: Dibujar el circuito con todos sus componentes, descripción

del funcionamiento, criterios de diseño, dibujar la señal de salida con sus valores característicos si la entrada es una señal sinusoidal cuya amplitud varía entra 2 y 12 voltios

respecto a tierra y las tensiones umbral son de 3 y 8 voltios respectivamente (misma referencia).

SOLUCIÓN:

Es aplicación directa de la teoría particularizando para los valores del enunciado.

Exámenes de Conmutación V.09

6

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

13.09.06

30 Minutos Hoja 1

La señal del circuito rampa (V1, V2, Ta, Tar) se obtiene a partir de un generador variable

de señal rectangular (A, T, Tr) según el esquema:

donde Ta y Tar dependen exclusivamente de T y Tr. Suponiendo que la tensión de alimentación es Eb se pide:

a) (5 Puntos) Representar con todos sus componentes (transistores, resistencias y condensadores exclusivamente) el circuito rampa.

b) (1 Punto) Dibujar la señal de salida en función de la señal de entrada con la misma

base de tiempos.

c) (2 Puntos)Criterios de conmutación para la señal de entrada y para los componentes

del circuito rampa.

d) (2 Puntos) Determinar las funciones V1, V2, Ta y Tar en función de los parámetros de

la señal de entrada, de Eb y de los valores generales de los componentes del circuito

rampa.

(A efectos de representación gráfica se ha supuesto lineal el diente de sierra. Se pide

circuito basado en la teoría de la conmutación, no diagramas de bloques ni el uso de

amplificadores operacionales. Despreciar las caídas en los transistores. Para puntuar en

los apartados b, c ó d se necesita una puntuación favorable en el apartado a).

SOLUCIÓN

a) Una aplicación del problema

09 de los apuntes es el circuito

de barrido de una consola radar,

que necesita una señal como la

producida por el circuito rampa

que se pide. A la vista de la solución de este problema, es

inmediato el circuito:

Exámenes de Conmutación V.09

7

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

b) Suponiendo que con el valor "A" de la señal de entrada, los dos transistores T1 y T2

entran en conmutación, la salida toma valor "0 voltios" y el condensador se descarga

exponencialmente a través de la resistencia interna del transistor T2, que si se desprecia

produce una descarga instantánea. Cuando los transistores pasan al corte, el condensador C se carga exponencialmente a través de la resistencia serie R1 + R2. El Valor V1 se

consigue añadiendo al circuito tradicional de generación del diente de sierra, el transistor

T1 en la forma y actuación indicada.

c) Criterios de conmutación:

Si la tensión de alimentación es Eb, para utilizar la expresión simplificada de conmutación

(supuestas despreciables las pérdidas por conmutación en los transistores) es necesario

imponer como valor de amplitud de la señal de entrada A = Eb lo que se realiza con el

mando de amplitud del generador de señal rectangular.

Una vez ajustada la señal de entrada, para las conmutaciones de T1 es necesario que

RB1 ≤ βR1. Como los dos transistores conmutan a la vez, el criterio para T2 es función

exclusiva de la carga del condensador (el criterio de la asignatura es que mientras no se

diga lo contrario se desprecie) luego RB2 puede ser cualquiera. Si se tuviera en cuenta la

descarga real del condensador, se calcularía el máximo de intensidad en el momento de

conmutación, conocido el valor de tensión entre placas del condensador (V2) y la

resistencia dinámica colector-emisor de T2.

d) Determinación de funciones:

Ta = Tr - T

y

Tar = Tr

como se desprende del apartado b).

Para determinar V1 y V2 se calcula la tensión de salida Vs :

Si V es la ddp entre las placas del condensador durante la carga

(Eb - Vs) / R1 = C dV/dt

y

Vs = V + IR2 = V + CR2 dV/dt

V = Eb {1 - exp[-t/C(R1+R2)]}

Vs = V + {Eb R2/(R1+R2)} exp[-t/C(R1+R2)] = Eb {1- (R1/R1+R2).exp[-t/C(R1+R2)]}

V1 = Eb (R2/R1+R2) y

Exámenes de Conmutación V.09

V2 = Eb {1- (R1/R1+R2).exp[-Ta/C(R1+R2)]}

8

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

12.06.07

25 Minutos Hoja 1 (Test)

Solo una respuesta es cierta. (Bien 2, blanco 0 y mal -1 punto).MARCAR CASILLA.

a) Suponiendo despreciable la caída de tensión en diodos y transistores cuando están

en conmutación, que la entrada A está a cero voltios B a 3 v y que

+9v

en C hay una señal cuadrada de frecuencia 1 KHz y amplitud 0 ó

12 voltios,

+9v

La señal de salida son 3 voltios.

Al ser un multiplexor, la salida es C

La señal de salida son 9 voltios.

Otra, especificar: La señal de salida es cuadrada de 1KHz y

amplitud 0 ó 3 v.

A

B

En un producto lógico, la salida es la menor de las entradas

compatible con la alimentación. En el multiplexor de la figura la

salida no es C, pero se le parece, pues es una señal cuadrada de

frecuencia 1Kz y amplitud entre 0 y 3 v, sincronizada con C (si C es cero también lo es

la salida, y si C es 12 voltios la salida vale 3 voltios debido a la señal en B).

C

b) Si R=333 Ω, C=470 KpF, E=5 v y la señal de entrada es sinusoidal de 250 Hz y 9 v

pico, la señal de salida

Entrada

Son 5 v.

La señal de entrada con un nivel de 5 v.

Es de 250 Hz y 5 v pico

Otros, especificar: ___________________

C

Salida

R

E

La salida del circuito es la respuesta a la señal de entrada

supuesto un filtro pasa altos, a la que se añade un nivel de continua debido a la batería.

La frecuencia de corte del filtro son aprox. 1000 Hz. La señal de 250 Hz no pasa ó

queda reducida a amplitud cero. La salida son los 5 v de la batería.

c) El periodo de repetición de este multivibrador (β>20)

con RC=10 KΩ, RB=33 KΩ, C=35 KpF y CV=30 KpF

vale aproximadamente:

7 μs (microsegundos)

7 s (segundos)

2,3 ms (milisegundos)

Otro, especificar valor______________

El periodo de repetición viene determinado por la suma

de los periodos T1 y T2. En particular,

TR = (C + CV) RB Ln2 + C RB Ln2 = (2C +CV) RB Ln2

100 KpF 33 KΩ Ln2 ≈ 2310 10-6 s = 2.3 ms

B

Exámenes de Conmutación V.09

9

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

d) En un generador de diente de sierra, el condensador de 500 KpF se carga en 1 seg a

la tensión de 9.5 v aproximadamente, siendo Eb = 15 v. Si β>7 ¿qué se puede afirmar

de la resistencia de base si el tren de pulsos varía entre 0 y 9 v y se desprecian todas

las caídas en el transistor?:

6 MΩ < RB < 18 MΩ

RB < 14 MΩ

RB > 2 MΩ

RB < 7 MΩ

La relación V/Eb = 9.5/15 = 0,63 que coincide con t/RC = 1. Como sucede para t = 1 s,

RC = 1 s, la resistencia de carga del colector vale 2 MΩ. Al ser β>7, Eb = 15 v y VEntrada

= 9 v, la resistencia de base debe de ser menor ó igual a 8.4 MΩ. (Plantear la ecuación

general y despreciar caídas).

e) Con Eb 9 v, RC2 6 KΩ, RE 12 KΩ, β>10, RC1

15 KΩ, RB2 33 KΩ, RB 33 Ω y la tensión de

entrada 7.5 v

Las tensiones umbral valen 3 y 5 v.

La tensión de salida vale 6v.

No cumple las ec. de conmutación.

Otra, especificar: La tensión de salida

vale 9 voltios ó las tensiones umbral

valen 6 y 4 voltios.

Las ecuaciones de conmutación se cumplen

pues RC1 + RB2 < βRC2 y RB < βRC1. Las tensiones umbral valen 6v y 4v. Si la entrada es

de 7.5 v, T1 esta conmutado con lo que la salida vale Eb = 9v ó las tensiones umbral

son 6 y 4 voltios.

B

Exámenes de Conmutación V.09

10

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

13.09.2007 30 Minutos

Conmutación: A, B y C representan señales

triangulares de amplitud 10 VP y desfasadas 120º tal y

como se indica en la figura.

A

B

C

+ 10 v

C

0v

R=1Ω

I

A

+

E=5V

B

- 10 v

Estas señales se introducen en el circuito de la figura constituido por tres diodos ideales

(sin caída), una resistencia de potencia de 1 Ω y una batería ideal de 5 V.

a) (4 Puntos) Representar la señal de salida, indicando claramente valores cuantitativos.

b) (2 Puntos) Representar la intensidad que circula por la resistencia R con valores en

amperios.

c) (1 Puntos) Representar la intensidad producida por la señal A en el diodo.

d) (2 Puntos) Representar la intensidad que circula por la resistencia R con valores en

amperios si los diodos tienen una caída de 1 voltio.

e) (1 Puntos) Representar la intensidad producida por la señal A en el diodo si la caída

en éste es de 1 voltio.

Solución:

a,b y c)

El circuito representa un sumador lógico en el que la salida es la mayor de las entradas

por encima de 5 voltios que pone de referencia la batería. Para representar la salida, se

traza la línea de 5 voltios (rojo) y se traza la envolvente por encima de esta línea.

La intensidad IR será de 0 amperios cuando no conduzcan ninguno de los diodos. Irá

aumentando y disminuyendo hasta los 5 amperios según la forma de onda de las señales

de entrada tal y como se representa.

IR

+ 10 v

5v

0v

5A

C

0A

A

B

- 10 v

Exámenes de Conmutación V.09

11

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

La intensidad IA será distinta de cero cuando conduzca el diodo de entrada A, variando

entre 0 y 5 amperios según se representa. La señal en A está representada en verde.

IA

+ 10 v

5A

5v

C

0A

A

0v

B

- 10 v

d y e)

Si los diodos tienen una caída de 1 voltio, éstos no conducirán hasta que en sus entradas

la señal supere el valor de 6 voltios (línea azul). La salida será de 5 voltios cuando los

diodos no conduzcan, variando de forma triangular hasta los 9 voltios según se

representa. La intensidad variará entre 0 y 4 amperios.

IR

+ 10 v

6v

4A

C

0A

5v

A

0v

B

- 10 v

La intensidad IA será distinta de cero cuando conduzca el diodo de entrada A, variando

entre 0 y 4 amperios según se representa. La señal en A está representada en verde.

IA

+ 10 v

6v

4A

C

0A

5v

0v

A

B

- 10 v

Exámenes de Conmutación V.09

12

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

09.06.08 25 Minutos Hoja 1 (4 Ejerc.)

a) (2 Puntos) Representar la

señal de salida indicando los

valores de los distintos niveles. El

diodo se supone ideal sin caída.

El condensador está inicialmente

descargado. Los valores están

expresa-dos en voltios. (Cada

fallo quita un punto).

4

3

2

2

0

0

0

-1

-0.5

-2

4

-2

5

4

2

2

Salida

Entrada

0

0

-1

1

1.5

0

0

-1

b) (3 Puntos) Rellenar la tabla para el circuito de la figura, suponiendo despreciables todo

tipo de caídas de tensión en los transistores (β > 15). (Cada fallo resta un punto)

+12 v

T1 Conmutado T2 Conmutado

250 Ω

850 Ω

I3

10

0

0

I4

10

20

VSalida

22 Ω

I1

I2

350 Ω

β > 15

3.5

12

7

7

5

20

5

VE

150 Ω

Unidades

Unidades

v

v

mA

mA

mA

mA

c) (2 Puntos) Determinar las tensiones de salida S1 y S2 para las entradas representadas.

Suponer una caída de “1 voltio” en los diodos cuando conduzcan. Los valores de tensión,

en voltios, están referidos a tierra. Si las resistencias son de 1Ω, determinar las

intensidades que circulan por los diodos. (Solo se

obtienen los dos puntos si todas las soluciones son

+10 v

correctas).

2A

Escribir solo las soluciones

DA

8v

9v

4A

S2 = 8 voltios

6A

DB

S1 = 2 voltios

2v

1v

4A

2A

Exámenes de Conmutación V.09

¿Conduce el diodo DA?

SI

IDA = 4 A

¿Conduce el diodo DB?

SI

IDB = 4 A

13

A.Martín

Escuela Técnica Superior de Ingenieros Aeronáuticos-Universidad Politécnica de Madrid

d) (3 Puntos) Para la señal de entrada que se indica, suponiendo despreciables las

caídas en el transistor de β > 10, se pide rellenar el cuadro de valores y dibujar la onda

de salida con sus ten-siones. (Hay que responder todo para puntuar. Con un fallo 1 punto