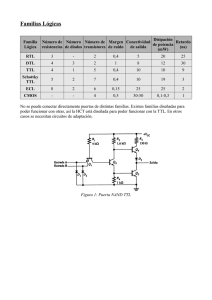

EJERCICIO TTL Teniendo el circuito anterior se pide: 1.- Función Lógica 2.- Potencia media consumida 3.- Factor de mérito 4.- Función de transferencia 5.- Márgenes de ruido 6.- Fan-Out CÁLCULOS TEÓRICOS Función Lógica: A B T1_A T1_B AD AD AD AI AI AD AI AI T2 OFF OFF OFF ON T3 ON ON ON OFF T4 OFF OFF OFF ON D1 ON ON ON OFF V0 Como podemos ver la función lógica que realiza sería NAND. Potencia media consumida: Tenemos que la potencia media consumida se calcula de la siguiente manera: 𝑃𝑀 = 𝑃𝐿 + 𝑃𝐻 + 𝑃𝑡 2 Donde el primer sumando es la potencia estática (P. consumida cuando esta a nivel L o H), el segundo sumando es la potencia dinámica (cuando la puerta cambia de nivel, de L a H, o de H a L). Este segundo sumando es despreciable en las familias lógicas bipolares. Pasamos a realizar el cálculo de las potencias en baja y en alta (elegimos los casos más desfavorables). -Potencia consumida con la salida a nivel bajo 𝑃𝐿 = 𝐼𝑅1 + 𝐼𝑅2 + 𝐼𝑅4 𝑉𝐶𝐶 Donde IR1, IR2 e IR4 son las intensidades que pasan por las resistencias R1, R2 y R4. 𝐼𝑅1𝐿 = 𝐼𝑅2𝐿 = 𝑉𝐶𝐶 − 𝑉𝐵𝐶 𝑇1 − 𝑉𝐵𝐸 𝑅1 = 0,725 (𝑚𝐴) 𝑉𝐶𝐶 − 𝑉𝐶𝐸 𝑇2 𝑆𝐴𝑇 𝑇2 − 𝑉𝐵𝐸 𝑅2 = 2,56 (𝑚𝐴) − 𝑉𝐵𝐸(𝑇4) 𝑇4 = = 5 − 3 · 0,7 (𝑉) = 4 (𝐾𝛺) 5 − 0,2 − 0,7 (𝑉) = 1,6 (𝐾𝛺) 𝐼𝑅4 = 0 La intensidad IR4 en baja es cero ya que el transistor 3 está en corte. Por tanto, tenemos que la potencia en baja es: 𝑃𝐿 = 0,725 + 2,56 + 0 (𝑚𝐴) · 5 𝑉 = 16,425 (𝑚𝑊) -Potencia consumida con la salida a nivel alto La calculamos de igual manera que en baja: 𝑃𝐻 = 𝐼𝑅1 + 𝐼𝑅2 + 𝐼𝑅4 · 𝑉𝐶𝐶 𝐼𝑅1𝐻 = 𝑉𝐶𝐶 − 𝑉𝐵𝐸 𝑇1 − 𝑉𝐼𝐿 5 − 0,7 − 0 (𝑉) = = 1,075 𝑚𝐴 𝑅1 4 (𝐾𝛺) 𝑉𝐼𝐿 = 0, ya que se considera el caso más desfavorable, cuando la entrada está conectada directamente a tierra. 𝐼𝑅2 = 0 𝐼𝑅4 = 0 Estas dos últimas son cero por que los transistores T2 y T4 están en corte, y aunque T3 se encuentre en zona activa, como la potencia se calcula sin carga, ambas intensidades son cero. 𝑃𝐻 = 1,075 𝑚𝐴 · 5 𝑉 = 5,375 (𝑚𝑊) Ya podemos calcular la potencia media consumida: 𝑃𝑀 = 𝑃𝐿 + 𝑃𝐻 16,425 + 5,375 (𝑚𝑊) = = 10,9 (𝑚𝑊) 2 2 Factor mérito: Para la familia TTL estándar el tiempo de propagación (hoja de datos) es de 10ns. 𝐹𝑀 = 𝑃𝑚 · 𝑇𝑃 = 10,9 𝑚𝑊 · 10 𝑛𝑠 = 0,109 (𝑝𝐽) Función de transferencia: 𝑉𝑂𝐻 = 𝑉𝐶𝐶 − 𝑉𝐷 − 𝑉𝐵𝐸 = 3,6 (𝑉) 𝑇3 − 𝐼2 · 𝑅2 = 5 − 0,7 − 0,7 − 0 Por los motivos antes indicados: 𝐼𝑅2 = 0 𝑉𝑂𝐿 = 𝑉𝐶𝐸 𝑇4 𝑆𝐴𝑇 = 0,2 𝑉 𝑉𝐼𝐻 = 𝑉𝐵𝐸 + 𝑉𝐵𝐸 𝑇2 + 𝑉𝐵𝐶 𝑇1 − 𝑉𝐵𝐸 𝑇1 = 0,7 + 0,7 + 0,7 − 0,7 = 1,4 𝑉 𝑇4 𝑉𝐼𝐿 = 0,7 𝑉 Función de transferencia obtenida en multisim: Con ambas entradas a nivel H, vemos que el programa toma para 𝑉𝐶𝐸 𝑇4 𝑆𝐴𝑇 = 200mV, un valor de 𝑉𝐼𝐻 = 1,3838𝑉 muy próximo a los 1,4V obtenidos. Cuando ambas entradas, o alguna de ellas están a nivel L, observamos que la salida en el simulador es 4,5856V. Difiere de los 3,6V calculados debido a que el programa considera valores de conducción de los semiconductores más bajo que los 0,7V teóricos que hemos considerado. Márgenes de ruido: 𝑁𝑀𝐻 = 𝑉𝑂𝐻 − 𝑉𝐼𝐻 = 3,6 − 1,4 (𝑉) = 2,2 𝑉 𝑁𝑀𝐿 = 𝑉𝐼𝐿 − 𝑉𝑂𝐿 = 0,7 − 0,2 (𝑉) = 0,5 𝑉 FAN - OUT: 𝐹𝑂𝐻 = 𝐼𝑂𝐻 𝐼𝐼𝐻 Dado que 𝐼𝐼𝐻 , es la corriente que entra en la puerta a través de los diodos y dados que en este caso los diodos están polarizados inversamente, ésta es muy pequeña, por lo tanto 𝐹𝑂𝐻 , es grande. Pasamos a calcular el 𝐹𝑂𝐿 . 𝐹𝑂𝐿 = 𝐼𝐼𝐿 = 𝐼𝑂𝐿 𝐼𝐼𝐿 𝑉𝐶𝐶 − 𝑉𝐼𝐿 − 𝑉𝐵𝐸(𝑇1) 5 − 0,2 − 0,7 = = 1,025 (𝑚𝐴) 𝑅1 4 Ahora si tomamos 𝑉𝐼𝐿 = 0,2𝑉, ya que la entrada se encuentra conectada a la salida de otra puerta. 𝐼𝑂𝐿 = 𝐼𝐶(𝑇4) = 𝐼𝐵(𝑇4) · 𝛽𝐹4 Para este cálculo tomamos la 𝛽𝐹4 = 50 (dato del problema, u obtenido de la hoja de datos), y pasamos a calcular 𝐼𝐵(𝑇4) : 𝐼𝐵(𝑇4) 𝑉𝐵𝐸 𝑇4 = 𝐼𝑅1𝐿 + 𝐼𝑅2𝐿 − 𝐼𝑅3 = 𝐼𝑅1𝐿 + 𝐼𝑅2𝐿 − 𝑅3 = 0,725 + 2,56 − 0,7 = 2,585 (𝑚𝐴) 𝐼𝑂𝐿 = 𝐼𝐶(𝑇4) = 𝐼𝐵(𝑇4) · 𝛽𝐹4 = 2,585 𝑚𝐴 · 50 = 129,25 (𝑚𝐴) 𝐹𝑂𝐿 = 𝐼𝑂𝐿 /𝐾 129,25/10 = = 12 𝑝𝑢𝑒𝑟𝑡𝑎𝑠 𝐼𝐼𝐿 1,025 Donde K es un factor de sobresaturación, para garantizar que T4 no salga de la saturación y se cumpla la condición: 𝐼𝐵 ≫ 𝐼𝐶 𝛽𝐹 , este factor se encuentra comprendido entre 5 y 10, hemos tomado éste último valor.