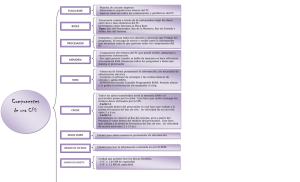

La arquitectura de una computadora se refiere a la disposición y organización de sus componentes internos, incluyendo la unidad central de procesamiento (CPU), la memoria, los dispositivos de entrada/salida, y los buses de comunicación entre ellos. Esta arquitectura es fundamental para determinar las capacidades y limitaciones de un sistema informático en términos de velocidad, capacidad de procesamiento y capacidad de almacenamiento. La máquina de Von Neumann es un diseño de arquitectura de computadora que fue propuesto por el matemático John von Neumann en 1945. Esta arquitectura se basa en la idea de que los programas y los datos se almacenan en la misma memoria y se acceden a través de la misma vía, lo que permite un acceso más rápido y eficiente a los datos. Esta arquitectura también incluye una unidad de control que interpreta las instrucciones y una unidad aritmético-lógica que realiza las operaciones matemáticas y lógicas. La máquina de Von Neumann fue utilizada en la construcción de EDSAC, la primera computadora de programa almacenado. Este diseño también se utilizó en la construcción de la máquina IAS, que fue construida en colaboración con Herman Goldstine. Desde entonces, la mayoría de las computadoras modernas se basan en la arquitectura de Von Neumann, aunque han surgido variantes y mejoras a lo largo del tiempo para adaptarse a las necesidades de diferentes aplicaciones y usuarios. La organización de computadoras se refiere a las unidades funcionales y sus interconexiones, que materializan especificaciones arquitectónicas. Modelo de arquitectura John von Neumann - Budapest, Imperio austrohúngaro, 28 de diciembre de 1903-Washington, D. C., Estados Unidos, 8 de febrero de 1957) fue un matemático húngaroestadounidense que realizó contribuciones fundamentales en física cuántica, análisis funcional, teoría de conjuntos, teoría de juegos, ciencias de la computación, economía, análisis numérico, cibernética, hidrodinámica, estadística y muchos otros campos. Las computadoras con arquitectura Von Neumann se realizan a partir de tres conceptos claves, que son: 1.- Los datos y las instrucciones se almacenan en una sola memoria de lectura escritura. 2.- Los contenidos de esta memoria se direccionan indicando su posición, sin considerar el tipo de dato contenido en la misma. 3.- La ejecución se produce siguiendo una secuencia de instrucción trasinstrucción (a no ser que dicha instrucción se modifique explícitamente) Segmentadas Consiste en la segmentación del procesador, a lo que llamamos "pipe-line", descomponiéndolo en etapas para poder procesar una instrucción diferente en cada una de ellas y trabajar con varias a la vez. La arquitectura en pipeline (basada en filtros) consiste en ir transformando un flujo de datos en un proceso comprendido por varias fases secuenciales, siendo la entrada de cada una la salida. Surgen por la necesidad de aumentar la velocidad de procesamiento. La arquitectura en pipeline es una técnica que divide el procesador en etapas para procesar instrucciones de forma paralela y mejorar la velocidad de procesamiento. Cada etapa recibe la salida de la anterior y se basa en la transformación secuencial de un flujo de datos. Esta técnica surge por la necesidad de mejorar el desempeño al realizar varias etapas del ciclo de instrucción al mismo tiempo. De multiprocesamiento. Las arquitecturas segmentadas buscan mejorar el desempeño realizando paralelamente varias etapas del ciclo de instrucción mismo tiempo. El procesador se divide en varias unidades funcionales independientes y se dividen entre ellas el procesamiento de las instrucciones. La arquitectura de multiprocesamiento es un diseño de computadora que utiliza varios procesadores para trabajar en conjunto en la resolución de tareas. Estos procesadores pueden compartir recursos y trabajar simultáneamente en diferentes partes de una tarea, lo que permite una mayor capacidad de procesamiento y una mejor eficiencia en el uso de recursos. Análisis de los componentes: CPU, arquitecturas, tipos, características y funcionamiento (ALU, unidad de control, registros y buses internos). Según Sanchis (2002) la estructura interna de un CPU contiene los siguientes bloques funcionales. Unidad Aritmética-Lógica (ALU): su función es realizar las operaciones aritméticas y lógicas. La operación por realizar, la indica la unidad de control. Los operandos se guardan en registro al igual que el resultado. Unidad de Control (UC): la tarea de la unidad de control es generar señales de control necesarias para organizar los flujos de información externos e internos entre la CPU y el resto del sistema. Registros: son elementos de memoria que sirven para guardar información importante y necesaria para la CPU. Interconexión interna de la CPU: son mecanismos que proporcionan comunicación entre la Unidad de Control, ALU y Registros. La unidad central de procesamiento (CPU) de un ordenador controla el flujo de acciones y datos del ordenador. Los procesadores de uso general son eficientes y económicos en la ejecución de tareas informáticas básicas como la navegación web, edición de fotos y programas de oficina. Son capaces de manejar la mayoría de las tareas informáticas sin problemas. Los procesadores convencionales o de gama media son más grandes y pueden manejar tareas de alto rendimiento como juegos 3D y edición de video. Sin embargo, consumen más energía y pueden no ser compatibles con componentes más antiguos. Actualizar el sistema puede mejorar el rendimiento. Los procesadores más rápidos, también conocidos como de gama alta o extreme, se usan para jugar a videojuegos, crear y editar vídeos profesionales, realizar análisis estadísticos y para los gráficos intensivos. Si va a actualizar un ordenador existente, preste especial atención a las especificaciones para componentes compatibles. Las CPU de gama alta consumen más energía y requieren más memoria. CPU un núcleo Su origen causó una gran revolución en el mundo de la tecnología, es aquel tipo de procesador que solo cuenta con un núcleo, lo cual hace que sea posible la realización de ciertas tareas, pero era un tanto lento. CPU de dos núcleos o dual core La palabra dual core o incluso denominado como simplemente dúo, hace referencia a que el procesador posee dos núcleos, es decir, que en su chip tiene 2 núcleos que realizan el trabajo. En este tipo de procesadores se puede destacar que contienen dos núcleos los cuales pueden procesar de una mejor manera, varias áreas, rindiendo mucho mejor que los procesadores que poseen sólo un núcleo. CPU de cuatro núcleos o quad core El término Quad indica que hay 4 núcleos en el procesador, ya sean Intel o AMD, se caracterizan por tomar muy en cuenta lo que es la relación entre la velocidad versus el consumo de energía, además estas poseen grandes capacidades para la realización de multitareas en comparación con los dos últimos CPU nombrados. Cabe mencionar que también existen los CPU de 6, 8 e inclusive de 10 núcleos, normalmente usados en la actualidad, esto es debido a que ofrecen una mayor rapidez para la realización de diferentes tareas sin ralentización. La CPU funciona en base a la operación de programas previamente diseñados y establecidos. Estos programas son organizados por números en serie y pueden representar cuatro pasos básicos: • Leer la información: juntar información o instrucciones sobre una operación. • Decodificar la información: dividir esa información en partes entendibles y significativas para la CPU. • Ejecutar la información: el momento más importante ya que en él se lleva a cabo la instrucción y se ponen a trabajar varias partes juntas de la CPU. • Mandar la información de vuelta: para dejar establecidos los resultados de la tarea realizada. Arquitectura básica y sus operaciones. En la figura vemos la estructura básica de este dispositivo se puede apreciar que pese a la complejidad de los microprocesadores su diagrama de bloques es muy sencillo. A grandes rasgos, esta es la estructura básica de los microprocesadores: La Unidad Aritmética Lógica (ALU), que ejecuta todas las operaciones solicitadas. Una serie de registros, donde se almacenan temporalmente los datos. De aquí, la ALU extrae las instrucciones sobre las operaciones específicas a realizar y sobre el segmento de la memoria RAM donde vaciará sus resultados una vez ejecutadas las instrucciones. Una serie de bloques de control (direcciones, datos, memoria), para comunicarse con el exterior. Estos bloques controlan el flujo de información y el orden de ejecución del programa. El circuito de reloj o Timer, sincroniza perfectamente la ejecución de todas las operaciones señaladas en los tres puntos anteriores. Memoria: Conceptos básicos del manejo de la memoria, memoria principal semiconductora y memoria caché. Es una unidad en la que se almacenen los datos, los resultados parciales y los resultados finales del proceso. Cuando el sistema digital de proceso es programable, además, han de memorizarse las instrucciones del proceso. Memoria: Parte del computador que almacena la información: instrucciones y datos. Es conjuntos de posiciones de memoria. Dirección: Posición de memoria en la que se almacena una información Punto de memoria: elemento que almacena un bit Palabra: número de bits que suele contener cada posición de memoria (8,16, 32 ó 64 bits) Operaciones básicas: lectura y escritura Parámetros característicos Capacidad: cantidad de información que puede almacenar un dispositivo Medidad más usuales: Kilobyte (KB)=2^10 bytes Megabyte (MB)=2^20 bytes Gigabyte (GB)=2^30 bytes Terabyte (TB)=2^40 bytes Velocidad o tiempo de acceso: tiempo que transcurre desde que se proporciona la dirección de la memoria y el momento en que el dato está disponible (lectura) o queda grabado (escritura). Ciclo de memoria: Tiempo que transcurre entre dos accesos consecutivos a memorial. Es superior al tiempo de acceso. Coste por bit: precio por cada bit de información Jerarquía de memoria Consiste en distribuir la información de diversos dispositivos de memoria, de forma que, cerca del procesador se ubique el modelo de memoria más rápido y de menor capacidad El dispositivo más lento y de mayos capacidad contiene la totalidad del código y los datos de un programa El procesador percibe que la velocidad del sistema es aproximadamente la velocidad del dispositivo más rápido Memoria principal semiconductora. La memoria es un bloque de construcción importante, encontrado en computadoras digitales y sistemas. Una memoria es necesaria para el almacenamiento de instrucciones, datos y resultados obtenidos durante el procesamiento de datos. Mientras que en el pasado los núcleos de ferrita fueron ampliamente utilizados, en la mayor parte de los sistemas digitales las memorias semiconductoras han venido a reemplazar a los núcleos. Se puede establecer la siguiente clasificación: • De lectura y escritura o RAM • • • Estáticas (SRAM) Dinámicas o con refresco (DRAM) De sólo lectura ROM SRAM-(MEMORIAS BIESTABLES): SRAM son las siglas de la voz inglesa Static Random Access Memory, que significa memoria estática de acceso aleatorio (o RAM estática), La tecnología de memoria RAM basada en semiconductores capaz de mantener los datos sin necesidad de circuito de refresco se llama memoria RAM estática (SRAM). Es opuesta a la memoria RAM dinámica (DRAM) que requiere refresco dinámico. Hay dos tipos de SRAM: volátiles y no volátiles, que difieren en si los datos permanecen o no en ausencia de energía eléctrica. DRAM: DRAM son las siglas de la voz inglesa Dynamic Random Access Memory, que significa memoria dinámica de acceso aleatorio (o RAM dinámica), para denominar a un tipo de tecnología de memoria RAM basada en condensadores, los cuales pierden su carga progresivamente, necesitando de un circuito dinámico de refresco que, cada cierto período, revisa dicha carga y la repone en un ciclo de refresco. ROM: La memoria de solo lectura, conocida también como ROM (acrónimo en inglés de read-only memory), es un medio de almacenamiento utilizado en ordenadores y dispositivos electrónicos, que permite solo la lectura de la información y no su escritura, independientemente de la presencia o no de una fuente de energía. Los datos almacenados en la ROM no se pueden modificar, o al menos no de manera rápida o fácil. Se utiliza principalmente en su sentido más estricto, se refiere solo a máscara ROM -en inglés, MROM- (el más antiguo tipo de estado sólido ROM), que se fabrica con los datos almacenados de forma permanente y, por lo tanto, su contenido no puede ser modificado de ninguna forma. Sin embargo, las ROM más modernas, como EPROM y Flash EEPROM, efectivamente se pueden borrar y volver a programar varias veces, aun siendo descritos como "memoria de sólo lectura" (ROM). Memoria caché Obejtivo de la memoria caché: dar la impresión de que las referencias a memoria se sirven a una velocidad muy cercana a la del procesador Diseño de la memoria Caché: - Se debe tener en cuneta la optimización de los siguiente parámetros: probabilidad de acierto, tiempo de acceso efectrivo, retardos debidos a fallos Está dividid lóficamente en: el directorio y los bloques de datos estableciendo la correspondencia entre bloques de MP y bloques de Caché Para trabajar con memoria caché, la memoria principal se organiza en bloques de palabras, de manera que cuando hay que trasladar datos de la memoria principal a la memoria caché se lleva un bloque entero de palabras de memoria, no se trabaja con palabras individuales. También se organiza bloques que se denominan líneas. Cada línea está formada por un conjunto de palabras más una etiqueta compuesta por unos cuantos bits. El contenido de la etiqueta permitirá saber qué bloque de la memoria principal se encuentra en cada línea de la memoria caché en un momento dado. La memoria caché es una memoria intermedia entre el procesador y la memoria principal que permite acceder más rápidamente a los datos. Cada vez que el procesador necesita acceder a un dato, primero busca en la memoria caché. Si lo encuentra, se produce un acierto y se proporciona al procesador. Si no lo encuentra, se produce un fallo y se trae el bloque de datos que contiene el dato desde la memoria principal a la caché para su posterior acceso. Cuando hay un fallo, el hardware de la memoria caché debe realizar la secuencia de tareas siguiente: 1) Solicitar a la memoria principal el bloque en el que está el dato que ha 1. producido el fallo. 2) Llevar el bloque de datos solicitado a la memoria caché. Las operaciones realizadas en esta tarea dependerán de las políticas de asignación y algoritmos de reemplazo que veremos más adelante. 3) El procesador obtiene el dato de la memoria caché como si se hubiera producido un acierto. Manejo de la entrada/salida, módulos de entrada/salida, entrada/salida programada, entrada/salida mediante interrupciones, acceso directo a memoria, canales y procesadores de entrada/salida Módulos de entrada/salida. Para llevar a cabo la operación de E/S, hemos de conectar el periférico al computador. Para hacerlo, es necesario que el computador disponga de unos dispositivos intermedios por donde ha de pasar toda la información que intercambia el computador con el periférico y que nos permite hacer una gestión y un control correctos de la transferencia. Estos dispositivos los llamamos de manera genérica módulo de E/S. Estructura del sistema de E/S del computador Los elementos principales que forman el sistema de E/S son los siguientes: • los periféricos, • los módulos de E/S, • los sistemas de interconexión externos y • el mapa de memoria e instrucciones de E/S. Periféricos: Los periféricos son dispositivos que se conectan al computador mediante los módulos de E/S y que sirven para almacenar información o para llevar a cabo un tipo determinado de comunicación con el exterior con humanos, con máquinas o con otros computadores. Un periférico consta de una parte mecánica y una parte electrónica que permite la conversión de datos entre el dispositivo y la computadora. La conexión física entre el periférico y la computadora se realiza mediante un sistema de interconexión de E/S que gestiona la transferencia de información a través del módulo de E/S de la computadora. En este módulo se analiza la transferencia de información entre el periférico y la computadora. Módulos de E/S Un módulo de E/S es un controlador que facilita la comunicación entre uno o varios periféricos y el computador a través de una interfaz. Su función es ocultar los detalles técnicos del periférico al resto del computador y establecer una comunicación eficiente entre ellos. Del módulo de E/S distinguimos tres partes básicas: 1. Una interfaz interna normalizada con el resto del computador mediante el bus de sistema que nos da acceso al banco de registros del módulo de E/S. 2. Una interfaz externa específica para el periférico que controla. Habitualmente la conexión con el periférico se realiza mediante un sistema de interconexión normalizado de E/S. 3. La lógica necesaria para gestionar el módulo de E/S. Es responsable del paso de información entre la interfaz interna y externa. En la siguiente figura el esquema general de un módulo de E/S. Sistemas de interconexión externos En un computador distinguimos dos tipos básicos de sistemas de interconexión: los internos del computador, que nos permiten conectar el procesador, la memoria y el sistema de E/S y que denominamos bus del sistema, y los externos al computador, que nos permiten conectar el sistema de E/S con los diferentes periféricos y que denominamos sistemas de interconexión de E/S o buses de E/S. Mapa de memoria e instrucciones de E/S Para identificar los registros del módulo de E/S hay dos posibilidades: Mapa común de memoria y E/S: En este sistema, no hay diferencia entre las direcciones de memoria y los registros de E/S. Se utilizan descodificadores que se activan mediante las líneas del bus de direcciones y se utilizan las mismas señales de control READ/WRITE para seleccionar la memoria y acceder a los puertos de E/S con las mismas instrucciones de transferencia que se utilizan para acceder a memoria. Esto permite aprovechar el amplio conjunto de instrucciones del procesador para acceder a memoria y hacer programas más eficientes, aunque requiere dedicar una parte del espacio de memoria a las direcciones de E/S, lo que puede limitar la cantidad de espacio disponible para la memoria. Sin embargo, este problema es cada vez menos importante debido al aumento del espacio de memoria disponible. Mapa independiente de E/S: Hay distinción entre direcciones de memoria y registros de E/S. Las líneas de direcciones se suelen compartir, pero hay que añadir algunas líneas de control para distinguir si un acceso es a memoria o a un puerto de E/S. También son necesarias instrucciones específicas de E/S. Las instrucciones utilizadas habitualmente son IN (para leer del puerto de E/S) y OUT (para escribir en el puerto de E/S). Este sistema tiene la ventaja de que la memoria dispone de todo el rango de direcciones y la clara desventaja de que dispone de un reducido número de instrucciones específicas de E/S que solo disponen de los modos de direccionamiento más básicos para acceder a los puertos de E/S. E/S programadas Para hacer la operación de E/S entre el procesador y el módulo de E/S, el procesador ejecuta un programa que controla toda la operación de E/S (programación, transferencia de datos y finalización). Sincronización: Durante la sincronización, el procesador, como responsable de la transferencia, ejecuta un programa que mira constantemente el estado del periférico consultando el registro de estado del módulo de E/S. Este método de sincronización se denomina sincronización por encuesta o espera activa. Mientras se lleva a cabo la sincronización, el procesador está dedicado al cien por cien a esta tarea y, por lo tanto, no puede atender a otros procesos o aplicaciones. Si esta espera es muy larga, puede degradar el nivel de prestaciones de todo el sistema. Intercambio del dato: Durante el intercambio del dato, si es una operación de lectura (entrada), el procesador lee el registro de datos del módulo de E/S para recoger el dato enviado por el periférico, y lo guarda en memoria; si es una operación de escritura (salida), el procesador toma de la memoria el dato que queremos enviar al periférico y lo escribe en el registro de datos del módulo de E/S. Entrada/salida mediante interrupciones. Usando la técnica de E/S por interrupciones la sincronización entre el periférico y el procesador es llevada a cabo por el módulo de E/S, de forma que se descarga al procesador de esta responsabilidad. Para utilizar esta técnica de E/S en un computador, es necesario considerar tanto aspectos del software como del hardware. El computador debe contar con una línea de petición de interrupción (INT) para recibir la señal del módulo de E/S indicando que está listo para la transferencia. Esta señal es activa a la baja y forma parte del conjunto de líneas de control del bus del sistema. El procesador debe tener un punto de conexión de entrada para recibir las interrupciones y el módulo de E/S debe tener un punto de conexión de salida para generar las interrupciones. Acceso directo a memoria. La técnica de E/S programada y la técnica de E/S por interrupciones requieren una gran cantidad de tiempo del procesador para realizar transferencias de datos, lo que puede limitar la velocidad de transferencia y la capacidad del procesador para realizar otras tareas. Una técnica más eficiente para transferir bloques de datos es el acceso directo a memoria (DMA), en el que el procesador programa la transferencia de datos entre el periférico y la memoria y un módulo de DMA se encarga de hacer toda la transferencia, liberando al procesador para realizar otras tareas. El módulo de DMA se encarga de la gestión de la transferencia de datos entre el periférico y la memoria. Utilizando la técnica de E/S por DMA se descarga al procesador de la responsabilidad de llevar a cabo la sincronización y el intercambio de datos entre el periférico y la memoria. Los canales de E/S son una mejora de los controladores de DMA. Pueden ejecutar instrucciones que leen directamente de memoria. Eso permite gestionar con más autonomía las operaciones de E/S y de esta manera se pueden controlar múltiples operaciones de E/S con dispositivos con una mínima intervención del procesador.Las dos configuraciones básicas de canales de E/S son las siguientes: • Canal selector: está diseñado para periféricos de alta velocidad de transferencia y solo permite una operación de transferencia simultánea. • Canal multiplexor: está diseñado para periféricos más lentos de transferencia y puede combinar la transferencia de bloques de datos de diferentes dispositivos. Las ventajas principales de los canales de E/S respecto a los controladores de E/S son las siguientes: • Permiten controlar operaciones de E/S simultáneas. • Se pueden programar múltiples operaciones de E/S sobre diferentes dispositivos o secuencias de operaciones sobre el mismo dispositivo, mientras el canal de E/S efectúa otras operaciones de E/S. Buses: tipos, estructuras, jerarquías e interrupciones Hay dos categorías de acuerdo con este tipo: bus paralelo y bus serie. Bus paralelo: Este tipo de buses de datos se envían en formato bytes de manera simultánea, con el soporte de diferentes líneas que poseen funciones específicas. En los ordenadores se ha empleado de forma intensa, desde bus del mismo procesador, de los discos duros, tarjetas de video y hasta las impresoras. El bus front side de los equipos informáticos de Intel es un tipo de bus de esta clase y tiene unas responsabilidades bien particulares: 1. Las líneas de dirección, que se encargan de señalar la ubicación de la memoria o el componente que se va a comunicar con el ordenador. 2. Las líneas de control, se encargan de emitir señales entre los componentes, ejemplo de este son los indicadores o señalizadores de estado. 3. Las líneas de datos, se encargan de transmitir los bits al azar. Bus serie: En este tipo de buses informática, los datos o la información es enviada bit a bit y son restaurados mediante registros. Está compuesto por algunos conductores. Se está utilizando desde hace poco tiempo en buses para discos duros, tarjetas de expansión y procesador. Tipos de buses por su uso: Bus de control: Este controla el empleo y acceso a las líneas de dirección y datos. Estas líneas que suministrarse de particulares dispositivos que gobiernan su empleo. Bus de dirección: Este es un medio del procesador independiente del bus de datos, donde se instaura la dirección de memoria de la información que se está transmitiendo. Bus de datos: Estos tipo de buses, es llamado bidireccional, ya que la información puede entrar o salir del ordenador. En algunas computadoras, el bus de datos se emplea para enviar otra información además de los datos como tal, ejemplo: bits de dirección o datos de condiciones Estructuración de los buses: Existen dos organizaciones físicas de operaciones E/S que tienen que ver con los buses que son: · Bus único · Bus dedicado La primera gran diferencia entre estas dos tipos de estructuras es que el bus único no permite un controlador DMA (todo se controla desde la CPU), mientras que el bus dedicado si que soporta este controlador. El bus dedicado trata a la memoria de manera distinta que a los periféricos (utiliza un bus especial) al contrario que el bus único que los considera a ambos como posiciones de memoria (incluso equipara las operaciones E/S con las de lectura/escritura en memoria). Este bus especial que utiliza el bus dedicado tiene 4 componentes fundamentales • • • • Datos: Intercambio de información entre la CPU y los periféricos. Control: Lleva información referente al estado de los periféricos (petición de interrupciones). Direcciones: Identifica el periférico referido. Sincronización: Temporiza las señales de reloj. Interrupciones Esta técnica de E/S pretende evitar que el procesador tenga que estar parado o haciendo trabajo improductivo mientras espera a que el periférico esté preparado para hacer una nueva operación de E/S y pueda aprovechar este tiempo para ejecutar otros programas. Usando la técnica de E/S por interrupciones la sincronización entre el periférico y el procesador es llevada a cabo por el módulo de E/S, de forma que se descarga al procesador de esta responsabilidad. En esta sección se describe cómo se realiza una operación de E/S utilizando la técnica de acceso directo a memoria (DMA). Se explica que se siguen los mismos pasos que en la E/S programada, pero durante la transferencia de datos, la gestión de las interrupciones afecta al intercambio de datos. Durante la fase de sincronización, el procesador ejecuta otro programa mientras espera a que el módulo de E/S esté preparado y active la señal de petición de interrupción (INT). Esto permite al procesador realizar trabajo productivo mientras se lleva a cabo la transferencia de datos. En resumen, durante la fase de sincronización de la E/S por interrupciones, el procesador comprueba periódicamente si el módulo de E/S pide la atención del procesador sin afectar a su dedicación. En el momento en que llega una petición de interrupción, el procesador detiene la ejecución del programa actual y transfiere el control a la rutina de servicio de interrupción (RSI), que accede al módulo de E/S para llevar a cabo la transferencia de datos y luego continúa la ejecución del programa detenido haciendo el retorno de interrupción. Gestión de una interrupción con un único módulo de E/S Cuando el módulo de E/S pide la atención del procesador, se produce una secuencia de acontecimientos que el procesador ha de gestionar. El procesador detiene la ejecución del programa actual y traslada el control a la rutina de servicio de interrupción (RSI), que accede al módulo de E/S correspondiente para realizar la transferencia de datos. Una vez finalizada la ejecución de la RSI, se realiza un retorno de interrupción para que el procesador pueda continuar con la ejecución del programa que había detenido. El procesador tiene una fase de comprobación de interrupciones en el ciclo de ejecución de instrucción para detectar si ha llegado una petición de interrupción. Petición del módulo de E/S. El módulo de E/S está preparado para hacer una transferencia y activa la INT. Entonces, cuando el procesador acaba la ejecución de la instrucción actual, en la última fase del ciclo de ejecución de la instrucción, la fase de comprobación de interrupción, detecta que se ha hecho una petición. Ciclo de reconocimiento de la interrupción. Esta es seguramente la parte más compleja de la gestión de interrupciones porque se producen muchos acontecimientos en poco tiempo y, como veremos más adelante, algunos de estos acontecimientos se pueden producir encabalgadamente en el tiempo y hay que estar atento a quién genera la acción, quién la recibe y qué respuesta da.

0

0

Anuncio

Documentos relacionados

Descargar

Anuncio

Añadir este documento a la recogida (s)

Puede agregar este documento a su colección de estudio (s)

Iniciar sesión Disponible sólo para usuarios autorizadosAñadir a este documento guardado

Puede agregar este documento a su lista guardada

Iniciar sesión Disponible sólo para usuarios autorizados