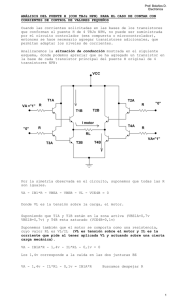

SolucionClase.pdf Anónimo Fundamentos Físicos y Tecnológicos de la Informática 1º Grado en Ingeniería Informática Escuela Técnica Superior de Ingenieros Informáticos Universidad Politécnica de Madrid Reservados todos los derechos. No se permite la explotación económica ni la transformación de esta obra. Queda permitida la impresión en su totalidad. a64b0469ff35958ef4ab887a898bd50bdfbbe91a-3748138 1. 1.1. Solución del problema de layout. Diagrama de barras. Vdd p p p p p Sal n n n n n Vss A B C D Figura 1: Diagrama de barras del circuito. Como es usual, los contactos de polarización se han recuadrado para distinguirlos. Dado que en el diagrama de barras no se señalan los pozos, hay que identificar de qué tipo son los transistores (las intersecciones entre policristalino y difusión) señalándolos con “p” o “n”. 1.2. Esquema circuito a nivel de transistores. Vdd A C B D Tps S1 C D Int A Sal Tns B Vss Figura 2: Esquema del circuito. 1.3. Función lógica. S1 = (A + B)(C + D) = A B + C D (1) Sal = (A + B)(C + D) (2) Reservados todos los derechos. No se permite la explotación económica ni la transformación de esta obra. Queda permitida la impresión en su totalidad. Fundamentos Fı́sicos y Tecnológicos a64b0469ff35958ef4ab887a898bd50bdfbbe91a-3748138 1.4. Tiempos de subida y bajada en el caso peor. Los peores tiempos de subida y bajada vienen definidos por las combinaciones de entrada que producen un camino a la alimentación y a masa respectivamente, con mayor resistencia. En el caso de subida ello ocurre, por ejemplo, cuando conducen los transistores pMOS gobernados por las señales A y B y no lo hacen los gobernados por las señales C y D. En el caso de bajada hay también varias combinaciones que producen un nivel bajo a través de caminos con máxima resistencia, por ejemplo, que se dé el caso de que conduzcan los transistores nMOS A y C y no connduzcan ni B ni D. Ası́ pues, las constantes de tiempo que nos interesan están dadas por: La capacidad de entrada del inversor de salida, que a su vez está formada por las dos capacidades de puerta de los transistores Tps y Tns. La combinación en serie de dos transistores pMOS en el caso de conmutación a nivel alto. La combinación en serie de dos transistores nMOS en el caso de conmutación a nivel bajo. En primer lugar debemos hallar las capacidades involucradas. Nos dan la capacidad por unidad de área (10fF/µm2 ), lo que significa que aproximamos las capacidades de entrada de los transistores por medio de la fórmula del condensador plano paralelo, es decir, las capacidades de entrada de los transistores son proporcionales al área de los mismos (al área del electrodo de puerta). Dado que el transistor pMOS mide 12λ × 2λ = 24λ2 y el nMOS mide 4λ × 2λ = 8λ2 , siendo λ = 0,06µm, la capacidad de uno y de otro será: Cp = 24 × (0,06)2 × 10fF = 0,864fF (3) 2 (4) Cn = 8 × (0,06) × 10fF = 0,288fF Luego la capacidad total que interviene, tanto en el proceso de carga como en el de descarga, es C = Cp + Cn = 1,152fF. La resistencia de un transistor MOS es proporcional a su relación de aspecto L/W , Longitud dividido por anchura (Width). Por dicho motivo, la resistencia se suele expresar, como en el problema, en ohmios por cuadro: dos transistores del mismo tipo y tecnologı́a con la misma relación de aspecto tienen la misma resistencia independientemente del tamaño que tengan. La relación de aspecto de los transistores pMOS es 2/12, mientras que la de los transistores nMOS es 2/4. Ası́ pues, la resistencia cada uno de estos transistores es: Rp = Rn = 2 1 × 3KΩ/2 = KΩ 12 2 2 1 × 1KΩ/2 = KΩ 4 2 (5) (6) Como hay dos transistores en serie en el caso peor, tanto en el caso de subida como en el de bajada, las constantes de tiempo involucradas resultan ser: 1 τ = 2 × KΩ × 1,152fF = 1,152pS 2 Llévate 1 año de WUOLAH PRO con BBVA. ¿Cómo? ¡+Info aquí! (7) Reservados todos los derechos. No se permite la explotación económica ni la transformación de esta obra. Queda permitida la impresión en su totalidad. El punto intermedio “Int” realmente no realiza ninguna función lógica definida: si la salida S1 está cero, entonces Int estará a cero, porque la única forma de poner un cero en la salida S1 pasa por que Int esté a cero. Sin embargo, si la salida está a uno, puede que ocurra porque todas las entradas estén a cero, en cuyo caso Int está desconectado tanto de la alimentación como de masa, es decir, no está a ningún valor definido.