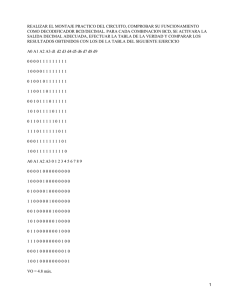

FUNDACIÓN UNIVERSITARIA KONRAD LORENZ-INGENIERÍA DE SISTEMAS LABORATORIO No. 4 Codificador de prioridad con visualización de 7 segmentos ELEMENTOS DEL COMPUTADOR Profesor: Héctor Arturo Flórez Fernández Presentado por: Javier Mauricio Gamboa Salgado Código: 544004 Facultad de Ingeniería de Sistemas Fundación Universitaria Konrad Lorenz Bogotá D.C. FUNDACIÓN UNIVERSITARIA KONRAD LORENZ-INGENIERÍA DE SISTEMAS 2007 OBJETIVOS Esta práctica tiene como objetivo principal la realización del diseño de un circuito que permita realizar la codificación a BCD con prioridad según el estado activo de las entradas, la “decodificación” y posterior visualización en un (1) Display de siete (7) segmentos. Para esto es necesario realizar el proceso de interpretación lógica de la operación de prioridad con base en los valores de entrada y las salidas BCD esperadas. A su vez es importante tener claros los conceptos de codificación con prioridad y el modelo del “Decodificador/Manejador”, así como el concepto de definición y manipulación de los Displays. En esta práctica se utilizará un circuito integrado que realiza la codificación a BCD y un decodificador/manejador para poder visualizar el resultado en el Display mencionado. En la etapa de implementación del circuito obtenido en el desarrollo teórico del ejercicio es necesario tener el conocimiento previo de los componentes a utilizar así como de sus propiedades. También debe existir una etapa de pruebas en la cual se determine el éxito del diseño o la reevaluación del mismo. FUNDACIÓN UNIVERSITARIA KONRAD LORENZ-INGENIERÍA DE SISTEMAS DISEÑO DE LA SOLUCIÓN Análisis del problema. Este problema se divide en dos etapas; la etapa de codificación con prioridad a BCD y la etapa de “decodificación” y presentación del resultado. Codificación con prioridad de diez (10) líneas a BCD. Inicialmente es necesario aclarar que a pesar de encontrar en los catálogos que el codificador 74147 es de diez (10) líneas decimales a cuatro (4) líneas BCD realmente solo tiene nueve (9) pines de entrada decimal. Esto es debido a que cuando no existe ninguna línea de entrada activa el código BCD de salida es 0000 lo cual muestra un cero (0) en el Display. Ahora bien la codificación con prioridad consiste en que se da prioridad a la línea activa de mayor peso dentro del conjunto de líneas de entrada. Por ejemplo si se encuentra activa la línea 8 y se activa simultáneamente la línea 4, la prioridad la mantiene la línea 8, pero en el mismo caso, si se activa simultáneamente la línea 9 la prioridad la tiene la línea 9. En resumen, cuando una línea está activa no importa que valor de entrada tienen las líneas de menor peso solo importará la activación de una línea de mayor peso. Dado esto, al tener nueve (9) líneas de entrada es posible obtener las combinaciones de salida en BCD como se muestra en la siguiente tabla de valores: Salidas (Código BCD) Entradas (Código Decimal) Decim al 9 8 7 6 5 4 3 2 1 B3 B2 B1 B0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 0 0 0 1 X 0 0 1 0 2 0 0 0 0 0 0 1 X X 0 0 1 1 3 0 0 0 0 0 1 X X X 0 1 0 0 4 0 0 0 0 1 X X X X 0 1 0 1 5 0 0 0 1 X X X X X 0 1 1 0 6 0 0 1 X X X X X X 0 1 1 1 7 FUNDACIÓN UNIVERSITARIA KONRAD LORENZ-INGENIERÍA DE SISTEMAS 0 1 X X X X X X X 1 0 0 0 8 1 X X X X X X X X 1 0 0 1 9 Es necesario tener en cuenta que el circuito integrado que permite realizar esta codificación es el 74147 y que tanto sus entradas como sus salidas están a nivel bajo, por lo tanto los valores de activación de las líneas de entrada deben ser aproximadamente de 0 V (Conexión a tierra) y los valores de no activación deben ser cercanos a 5 V (Conexión a Vcc con resistencia). Estos valores se ingresarán a través de pulsadores que simularán un teclado lineal que está descontinuado en el mercado. Por otra parte los valores de salida deben ser invertidos a través del circuito integrado 7404 para que ingresen a nivel alto al “Decodificador/Manejador”. “Decodificación” y presentación del resultado. Como se mencionó anteriormente las salidas del codificador con prioridad deben ser invertidas para ser las entradas del decodificador/manejador que en este caso es el circuito 7447. A su vez este circuito arroja las salidas a, b, c, d, e, f y g a nivel bajo que representan los siete (7) segmentos de un Display y específicamente uno de ánodo común. El Display utilizado es de la serie 5161 que tiene la siguiente distribución: Esta implementación permite visualizar los números del 0 al 9 en el Display dependiendo del pulsador que se oprima teniendo en cuenta que cada uno de ellos representa una línea de entrada al codificador con prioridad. Simulación. FUNDACIÓN UNIVERSITARIA KONRAD LORENZ-INGENIERÍA DE SISTEMAS Para llevar a cabo la simulación de la implementación del circuito se utilizó la herramienta Circuit Maker 2000. Anexo al archivo de este documento se encuentra un archivo llamado Práctica_4.ckt en el cual se encuentra el modelo del circuito completo. Sin embargo a continuación se muestra el dibujo del circuito obtenido de este software. FUNDACIÓN UNIVERSITARIA KONRAD LORENZ-INGENIERÍA DE SISTEMAS CONCLUSIONES Se pudo observar que es muy importante el análisis del problema de una forma correcta debido a que esto puede evitar la realización de un diseño que sea ineficiente en rendimiento o en costos. También está práctica deja como enseñanza que es muy importante revisar el nivel al que se manejan tanto las entradas como las salidas para poder evaluar los valores de estas dos etapas. Por otra parte fue muy importante conocer el funcionamiento y la distribución interna del circuito que permite realizar la codificación con prioridad así como las utilidades que pueden tener en casos reales de uso. Por último, fue de gran importancia conocer los comportamientos de los circuitos utilizados para obtener una implementación exitosa respecto al diseño realizado previamente.