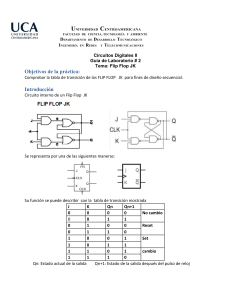

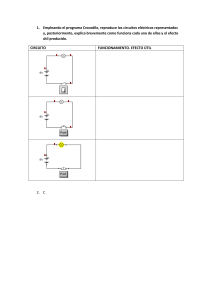

Entrega Final Sistemas Digitales y Ensambladores. Fecha límite de entrega: 11 de octubre Estudiante: Vanessa del Rocío Valencia Rincón El presente trabajo tiene como objetivo complemetar la formación en circuitos digitales por medio de la investigación y consulta, y también con la aplicación de conceptos estudiados en las seciones sincrónicas. El trabajo consta de tres puntos relacionados con el siguiente problema: Problema Para un evento programado para 10 familias debemos “contar” y mostrar el numero de familias que ingresaron con los tres integrantes completos, de acuerdo a las siguientes condiciones. 1. Una familia puede estar conformada maximo por tres personas, padre, madre e hijo. 2. Al evento prodá ingresar como minimo un integrante en representación de la familia. 1. Circuito Lógico que soluciona el problema Plantear un circuito lógico (compuertas - flip flops jk o contador, - decodificador BCD y dislay 7 segmentos) Que haga la tarea solicitad o se mostrar cuantas familia ingresaron completas. A continuación se adjunta el circuito logico de la solución, se utilizó la Logic.ly para llevar a cabo la simulación del circuito, en este se emplean flip flop tipo tipo T, Sin embargo, los flip flop tipo JK son los más comunmemente utilizados para estos contadores, se utilizan compuertas AND para las entradas, para el reset de los flip flop se usa una compuerta NOT, la cual se activa por medio de un pulsador. La tabla de la verda del flip flop es la que se presenta a continuación: K Q Q’ S C CLK J 0 0 X X X 1 0 0 1 X X X 0 1 1 0 X x X 1 1 1 1 0 0 Q Q’ 1 1 0 1 1 0 1 1 1 0 0 1 1 1 1 1 Toggle 1 1 1 x x Q Q’ El conteo se realizará de 0 a 9 por lo que las entradas de los flip flop se regiran por la siguiente tabla de verdad: Q3 Q2 Q1 Q0 Reset 0 0 0 0 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 1 0 1 0 0 En la siguiente tabla está el estado actual que se encuentra Qn, y el estado siguiente Qn+1. Asi tambien, el valor de Jn y Kn en la transicion de cada uno: Para Qn Q3 Q2 Q1 Q0 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 Para Qn+1 Q3 Q2 Q1 Q0 0 0 0 0 1 1 0 0 1 0 2 0 0 1 1 3 0 1 0 0 4 0 1 0 1 5 0 1 1 0 6 0 1 1 1 7 1 0 0 0 8 1 0 0 1 9 0 0 1 0 Q0 Q1 Q2 Q3 J0 K0 J1 K1 J2 K2 J3 K3 0 1 x 0 x 0 x 0 x 1 x 1 1 x 0 x 0 x 2 1 x x 0 0 x 0 x 3 x 1 x 1 1 x 0 x 4 1 x 0 x x 0 0 x 5 x 1 1 x x 0 0 x 6 1 x x 0 x 0 0 x 7 x 1 x 1 x 1 1 x 8 1 x 0 x 0 x x 0 9 x 1 0 x 0 x x 1 2. Circuito Real de la Solución Plantear el circuito real (con los circuitos integrados, sus referencias y componentes necesarios) mostrando las conexiones entre todos los pines. Para el circuito real, hecho en proteus, se utilizan 4 flip flops JK que llevaran el conteo de acuerdo a las familia que ingresen teniendo en cuenta las condiciones del enunciado. Estos ingresos se controlan en el circuito por medio de los pulsadores: 3. Máquinas de Estado Finito ¿Cómo relaciona el ejercicio anterior con una máquina de estado? (breve explicación) Las máquinas de estado finito constituyen un modelo abstracto para explicar el funcionamiento de una computadora o una máquina con una memoria simple o primitiva. En cuanto a los circuitos logicos combinatorios, como el visto en el ejercicio establecen relaciones lógicas entre los datos de entrada para producir un conjunto de datos de salida, sin tener en cuenta los cambios de estado en el sistema. Es por esto que se tenga más en consideración las máquinas de estado finito como un modelo teórico más completo. Por lo anterior, se deben incluir las máquinas de estado finito como un modelo para diseñar circuitos lógicos secuenciales. CONCLUSIONES - Los conocimientos teóricos se han comprobado mediante el desarrollo de cada uno de los circuitos, tanto lógicos como en los simuladores. - Los simuladores se convierten en una herramienta indispensable para probar el funcionamiento de los circuitos combinacionales y verificar la funcionalidad de cada compuerta, asi como de los integrados con los que se llevan los conteos (flip flops). - Se verificó de forma práctica la manera en que los Flip-Flops permiten almacenar valores en memoria. - Las tablas de verdad permiten para obtener ecuaciones en las que se basa el circuito mucho antes de llevar a cabo la simulación. - La utilización de del display 7 segmentos permite tener un visual clara de la salida del circuito ya que no es necesario el uso de leds individuales para interpretar las salidas que se esperan obtener de acuerdo a las condiciones del ejercicio. - Los circuitos integrados que se utilizaron en el simulador y que se consiguen en el mercado permiten con facilidad llevar a lo real esta práctica, por medio de protoboard y los integrados 7473 (flip flops), 7447 (Decodificador BCD), entre otros. BIBLIOGRAFIA - HIDALGO, E. S. DECODIFICADOR BCD A 7 SEGMENTOS. - Ugalde Saldaña, E. (2009). Caracterización del conjunto de salidas de una máquina finita. REPOSITORIO NACIONAL CONACYT. - Martínez, J. T., Villalobos, J. D. J. L., & Chaires, J. V. (2013). Análisis Térmico para un Circuito SoC de Disparo de un rectificador controlado de alta eficiencia. Difu100ci@, Revista de difusión científica, ingeniería y tecnologías, 7(2), 110-115. - Vázquez, M. A. (1975). Sintesis de Circuitos Secuenciales. Revista de la Universidad de Costa Rica.