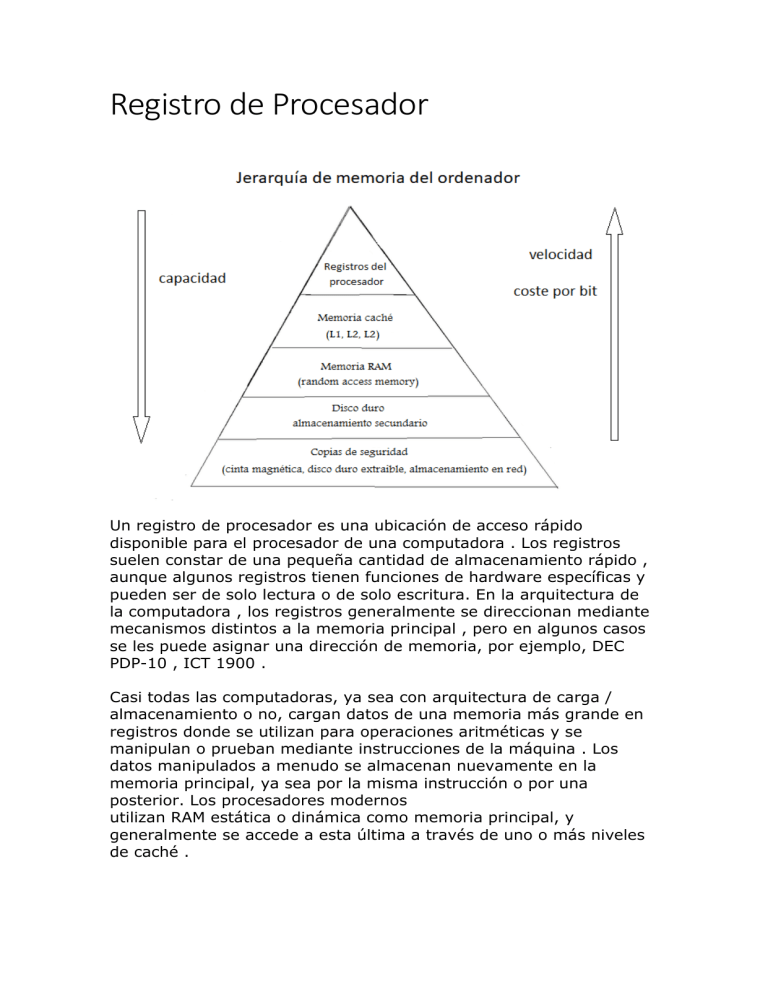

Registro de Procesador Un registro de procesador es una ubicación de acceso rápido disponible para el procesador de una computadora . Los registros suelen constar de una pequeña cantidad de almacenamiento rápido , aunque algunos registros tienen funciones de hardware específicas y pueden ser de solo lectura o de solo escritura. En la arquitectura de la computadora , los registros generalmente se direccionan mediante mecanismos distintos a la memoria principal , pero en algunos casos se les puede asignar una dirección de memoria, por ejemplo, DEC PDP-10 , ICT 1900 . Casi todas las computadoras, ya sea con arquitectura de carga / almacenamiento o no, cargan datos de una memoria más grande en registros donde se utilizan para operaciones aritméticas y se manipulan o prueban mediante instrucciones de la máquina . Los datos manipulados a menudo se almacenan nuevamente en la memoria principal, ya sea por la misma instrucción o por una posterior. Los procesadores modernos utilizan RAM estática o dinámica como memoria principal, y generalmente se accede a esta última a través de uno o más niveles de caché . Los registros del procesador normalmente se encuentran en la parte superior de la jerarquía de memoria y proporcionan la forma más rápida de acceder a los datos. El término normalmente se refiere solo al grupo de registros que se codifican directamente como parte de una instrucción, según lo definido por el conjunto de instrucciones . Sin embargo, las CPU modernas de alto rendimiento a menudo tienen duplicados de estos "registros arquitectónicos" para mejorar el rendimiento mediante el cambio de nombre de registros , lo que permite la ejecución paralela y especulativa . El diseño moderno x86 adquirió estas técnicas alrededor de 1995 con los lanzamientos de Pentium Pro , Cyrix 6x86 , Nx586 y AMD K5 . Cuando un programa de computadora accede a los mismos datos repetidamente, esto se llama localidad de referencia . Mantener los valores de uso frecuente en los registros puede ser fundamental para el rendimiento de un programa. La asignación de registros la realiza un compilador en la fase de generación de código o manualmente un programador en lenguaje ensamblador . Tamaño Los registros se miden normalmente por la cantidad de bits que pueden contener, por ejemplo, un " registro de 8 bits ", un " registro de 32 bits " o un " registro de 64 bits " o incluso más. En algunos conjuntos de instrucciones, los registros pueden operar en varios modos dividiendo su memoria de almacenamiento en otras más pequeñas (32 bits en cuatro de 8 bits, por ejemplo) en las que se pueden cargar múltiples datos (vector o matriz de datos unidimensional ). y operado al mismo tiempo. Por lo general, se implementa agregando registros adicionales que mapean su memoria en una más grande. Los procesadores que tienen la capacidad de ejecutar una sola instrucción en varios datos se denominan procesadores vectoriales . Tipos Un procesador suele contener varios tipos de registros, que pueden clasificarse según su contenido o las instrucciones que operan sobre ellos: Los registros accesibles para el usuario pueden leerse o escribirse mediante instrucciones de la máquina. La división más común de registros accesibles por el usuario es en registros de datos y registros de direcciones. o Registro de datos : puede contener valores de datos numéricos, tales como número entero y, en algunas arquitecturas, valores de coma flotante, así como los o o o o o o o personajes, pequeñas matrices de bits y otros datos. En algunas CPU más antiguas y de gama baja, un registro de datos especial, conocido como acumulador, se usa implícitamente para muchas operaciones. Registro de direcciones: de retención direcciones y son utilizados por las instrucciones que acceden indirectamente memoria primaria. Algunos procesadores contienen registros que solo pueden usarse para contener una dirección o solo para contener valores numéricos (en algunos casos se usan como un registro de índice cuyo valor se agrega como un desplazamiento de alguna dirección); otros permiten que los registros contengan cualquier tipo de cantidad. Existe una amplia variedad de posibles modos de direccionamiento , que se utilizan para especificar la dirección efectiva de un operando. El puntero de pila se utiliza para administrar la pila en tiempo de ejecución . En raras ocasiones, otras pilas de datos se direccionan mediante registros de direcciones dedicados, consulte la máquina de pila . Los registros de propósito general ( GPR ) pueden almacenar tanto datos como direcciones, es decir, son registros combinados de datos / direcciones; en algunas arquitecturas, el archivo de registro está unificado para que los GPR también puedan almacenar números de punto flotante . Los registros de estado contienen valores de verdad que se utilizan a menudo para determinar si alguna instrucción debe o no ejecutarse. De punto flotante registro s(FPRs) tienda de números de punto flotante en muchas arquitecturas. Los registros constantes contienen valores de solo lectura como cero, uno opi. Los registros vectoriales contienen datos para el procesamiento vectorial realizado por instrucciones SIMD(instrucción única, datos múltiples). Los registros de propósito especial ( SPR ) mantienen el estado del programa; generalmente incluyen el contador de programa , también llamado puntero de instrucción, y el registro de estado ; el contador de programa y el registro de estado pueden combinarse en un registro de palabra de estado de programa (PSW). El puntero de pila antes mencionado a veces también se incluye en este grupo. Los microprocesadores integrados también pueden tener registros correspondientes a elementos de hardware especializados. o En algunas arquitecturas, los registros específicos del modelo (también llamados registros específicos de la máquina) almacenan datos y configuraciones relacionadas con el propio procesador. Debido a que sus significados están asociados al diseño de un procesador específico, no se puede esperar que sigan siendo estándar entre generaciones de procesadores. o Registros de rango de tipo de memoria (MTRRs) Registros internos : registros a los que no se puede acceder mediante instrucciones, que se utilizan internamente para las operaciones del procesador. o Registro de instrucciones , que contiene la instrucción que se está ejecutando actualmente. o Registros relacionados con la obtención de información de la RAM , una colección de registros de almacenamiento ubicados en chips separados de la CPU: Registro de búfer de memoria (MBR), también conocido como registro de datos de memoria (MDR) Registro de direcciones de memoria (MAR) Registro arquitectónico- Los registros visibles para el software definido por una arquitectura pueden no corresponder al hardware físico, si el hardware subyacente está cambiando el nombre de los registros. Los registros de hardware son similares, pero ocurren fuera de las CPU. En algunas arquitecturas (como SPARC y MIPS), el primer o último registro en el archivo de registro de enteros es un pseudoregistro de una manera que está programado para devolver siempre cero cuando se lee (principalmente para simplificar los modos de indexación), y no puede ser sobrescrito. En Alpha, esto también se hace para el archivo de registro de punto flotante. Como resultado de esto, los archivos de registro comúnmente se citan como si tuvieran un registro más que cuántos de ellos son realmente utilizables; por ejemplo, se cotizan 32 registros cuando solo 31 de ellos se ajustan a la definición anterior de registro. La siguiente tabla muestra el número de registros en varias arquitecturas de CPU convencionales. Tenga en cuenta que en los procesadores compatibles con x86, el puntero de pila ( ESP ) se cuenta como un registro de números enteros, aunque hay un número limitado de instrucciones que pueden usarse para operar en su contenido. Se aplican advertencias similares a la mayoría de las arquitecturas. Aunque todas las arquitecturas enumeradas anteriormente son diferentes, casi todas son una disposición básica conocida como arquitectura de Von Neumann , propuesta por primera vez por el matemático húngaro-estadounidense John von Neumann . También es de destacar que la cantidad de registros en las GPU es mucho mayor que en las CPU. Arquitectura GPRs / datos + registros de direcciones Notas Registros FP AT&T Hobbit 0 pila de 7 Máquina de apilar Cray-1 [1] 8 datos escalares, 8 direcciones 8 escalares, 8 vectoriales (64 elementos) Los registros de datos escalares pueden ser enteros o de punto flotante; también 64 registros T escalares del bloc de notas y 64 registros B del bloc de notas de direcciones 4004 [2] 1 acumulador, otros 16 0 El registro A es de uso general, mientras que los registros r0 – r15 son para la dirección y el segmento. 8008 [3] 1 acumulador, otros 6 0 El registro A es un acumulador al que se hace toda la aritmética; los registros H y L se pueden utilizar en combinación como un registro de direcciones; todos los registros se pueden usar como operandos en las instrucciones de carga / almacenamiento / movimiento / incremento / disminución y como el otro operando en instrucciones aritméticas. No hay unidad FP disponible. 8080 [4] 1 acumulador, otros 6 0 Más un puntero de pila. El registro A es un acumulador al que se hace toda la aritmética; los pares de registros B + C, D + E y H + L se pueden utilizar como registros de direcciones en algunas instrucciones; todos los registros se pueden usar como operandos en las instrucciones de carga / almacenamiento / movimiento / incremento / disminución y como el otro operando en instrucciones aritméticas. Algunas instrucciones solo usan H + L; otra instrucción intercambia H + L y D + E. Los procesadores de punto flotante previstos para el 8080 fueron Intel 8231 , AMD Am9511 e Intel 8232 . También se podían utilizar fácilmente con el Z80 y procesadores similares. iAPX432 0 pila de 6 Máquina de apilar X86 de 16 bits [5] 6 pila de 8 (si hay FP presente) 8 086 / 8,088 mil , 80 186 / 80.188 , 80.286 , con 8.087 , 80.187 o 80.287 por punto flotante, con un 80-bit de ancho, 8 pila de registros profundo con algunas instrucciones capaces de utilizar los registros relativos a la parte superior de la pila como operandos; sin 8087/80187/80287, sin registros de coma flotante IA-32 [6] 8 pila de 8 (si está presente FP), 8 (si está presente SSE / MMX) 80386 requería 80387 para punto flotante, los procesadores posteriores tenían punto flotante incorporado, y ambos tenían una pila de registros de 8 bits de ancho y 8 de profundidad con algunas instrucciones capaces de usar registros relativos a la parte superior de la pila como operandos. El Pentium III y posteriores tenían el SSE con registros XMM adicionales de 128 bits. x86-64 [6] [7] dieciséis 16/32 Los registros FP son registros XMM de 128 bits, que luego se extendieron a registros YMM de 256 bits con AVX / AVX2 y registros ZMM0-ZMM31 de 512 bits con AVX512 . [8] Xeon Phi [9] dieciséis 32 Incluye 32 registros ZMM de 256/512 bits con AVX-512. Fairchild F8 un acumulador, 64 registros de scratchpad, un registro de scratchpad indirecto (ISAR) n/A Las instrucciones pueden hacer referencia directamente a los primeros 16 registros del scratchpad y pueden acceder a todos los registros del scratchpad indirectamente a través del ISAR [10] Geode GX 1 dato, 1 dirección 8 Geode GX / Media GX / 4x86 / 5x86 es la emulación de un procesador compatible con 486 / Pentium fabricado por Cyrix / National Semiconductor . Al igual que Transmeta , el procesador tenía una capa de traducción que traducía el código x86 al código nativo y lo ejecutaba. [ cita requerida ] No admite registros SSE de 128 bits, solo la pila 80387 de ocho registros de punto flotante de 80 bits, y admite parcialmente 3DNow! de AMD. El procesador nativo solo contiene 1 registro de datos y 1 dirección para todos los propósitos y se traduce en 4 rutas de registro de nombres de 32 bits r1 (base), r2 (datos), r3 (puntero trasero) y r4 (puntero de pila) dentro del scratchpad sram para operación de enteros y usa la caché L1 para emulación de código x86 (tenga en cuenta que no es compatible con algunas instrucciones 286/386/486 en modo real). [ cita requerida ] Más tarde, el diseño se abandonó después de que AMD adquiriera la propiedad intelectual de National Semiconductor y la marcara con el núcleo Athlon en el mercado integrado. SunPlus SPG 0 6 pila + 4 SIMD Un procesador de máquina de pila de espacio de direcciones de 32 bits de 16 bits de ancho de la empresa taiwanesa Sunplus Technology, que se puede encontrar en la línea V.Smile de Vtech con fines educativos y en la consola de videojuegos como Wireless 60, Mattel HyperScan y XaviXPORT. carece de registro de propósito general o registro interno para nombrar / renombrar, pero su unidad de punto flotante tiene una pila de 6 etapas de 80 bits y cuatro registros VLIW SIMD de 128 bits en un coprocesador de sombreado de vértices. VM Labs Nuon 0 1 un procesador de máquina de pila de 32 bits desarrollado por VM labs para fines multimedia especializados. Se puede encontrar en la propia línea de consolas de reproductores de DVD Nuon de la compañía y en el sistema de entretenimiento familiar Game Wave de los juegos ZaPit. El diseño tuvo una gran influencia de la tecnología MMX de Intel, contenía una caché de pila unificada de 128 bytes para instrucciones vectoriales y escalares. la caché unificada se puede dividir en 8 registros vectoriales de 128 bits o en registros escalares SIMD de 32 bits a través del cambio de nombre del banco; no se encuentra ningún registro entero en esta arquitectura. Nios II [11] [12] 31 8 Nios II se basa en el conjunto de instrucciones MIPS IV [ cita requerida ] y tiene 31 GPR de 32 bits, con el registro 0 conectado a cero y 8 registros de punto flotante de 64 bits [ cita requerida ] Motorola 6800 [13] 2 datos, 1 índice 0 Más un puntero de pila Motorola 68k [14] 8 datos (d0-d7), 8 direcciones (a0-a7) 8 (si FP presente) El registro de direcciones 8 (a7) es el puntero de pila. 68000, 68010, 68012, 68020 y 68030 requieren una FPU para punto flotante; 68040 tenía FPU incorporada. Los registros FP son de 80 bits. SH de 16 bits 1 6 Motor de emociones 3 (VU0) + 32 (VU1) 32 SIMD (integrado en UV1) + 2x 32 Vector (coprocesador vectorial dedicado que El núcleo principal de Emotion Engine (VU0) es un núcleo general DSP muy modificado para tareas generales en segundo plano y contiene un acumulador de 64 bits, dos registros de datos generales y un contador de programa de 32 bits. Un se encuentra cerca de su GPU) núcleo ejecutable MIPS III modificado (VU1) es para el control de protocolos y datos del juego y contiene 32 entradas, registros de uso general de 32 bits para el cálculo de enteros y 32 entradas, registros SIMD de 128 bits para almacenar instrucciones SIMD, valores de transmisión de datos y algunos números enteros. valor de cálculo. un registro acumulador para conectar el cálculo general de punto flotante al archivo de registro vectorial en el coprocesador. El coprocesador se construye a través de un archivo de registro vectorial de 32 entradas de 128 bits (solo puede almacenar el valor vectorial que pasa del acumulador en la CPU) y no hay ningún registro entero integrado. Tanto el coprocesador vectorial (VPU 0/1) como el motor de emoción completo El módulo del procesador principal (VU0 + VU1 + VPU0 + VPU1) se construye en base al conjunto de instrucciones MIPS modificado y el acumulador en este caso no es de propósito general sino de estado de control. CUDA [15] configurable, hasta 255 por hilo Las generaciones anteriores permitían hasta 127/63 registros por hilo ( Tesla / Fermi ). Cuantos más registros se configuren por subproceso, menos subprocesos se pueden ejecutar al mismo tiempo. Los registros tienen 32 bits de ancho, números de coma flotante de doble precisión y punteros de 64 bits requieren dos registros. Además, tiene hasta 8 registros de predicado por hilo [16] Serie CDC 6000 dieciséis 8 registros 'A' A0-A7 contienen direcciones de 18 bits; 8 registros 'B' B0-B7 contienen valores enteros de 18 bits (con B0 establecido permanentemente en cero); 8 registros 'X' X0-X7 contienen 60 bits 8 de datos enteros o de coma flotante. Siete de los ocho registros A de 18 bits se acoplaron a sus registros X correspondientes: establecer cualquiera de los registros A1 a A5 en un valor provocó una carga de memoria del contenido de esa dirección en el registro X correspondiente. Del mismo modo, la configuración de una dirección en los registros A6 o A7 provocó un almacenamiento de memoria en esa ubicación en la memoria desde X6 o X7. (Los registros A0 y X0 no se acoplaron así). Sistema / 360 , Sistema / 370 , Sistema / 390 , z / Arquitectura dieciséis 4 (si está presente FP); 16 en modelos G5 y posteriores S / 390 yz / Arquitectura FP era opcional en System / 360 y siempre estaba presente en S / 370 y posteriores. En los procesadores con Vector Facility, hay 16 registros vectoriales que contienen un número de elementos de 32 bits dependiente de la máquina. [17] A algunos registros se les asigna un propósito fijo mediante convenciones de llamada ; por ejemplo, el registro 14 se usa para direcciones de retorno de subrutina y, para ELF ABI, el registro 15 se usa como puntero de pila. El procesador S / 390 G5 aumentó el número de registros de coma flotante a 16. [18] MMIX [19] 256 256 Un conjunto de instrucciones diseñado por Donald Knuth a fines de la década de 1990 con fines pedagógicos. NS320xx [20] 8 8 (si FP presente) Xelerated X10 1 32 un procesador de red basado en una máquina de pila de 32/40 bits con instrucción MIPS modificada y una unidad de coma flotante de 128 bits. [ cita requerida ] Hélice Parallax 0 2 Un controlador de máquina de pila en rodajas de 8/16 bits de ocho núcleos con un circo lógico simple en el interior, tiene ocho contadores de engranajes (núcleo) y cada uno contiene tres registros de control especiales de 8/16 bits con ram de pila de 32 bits x 512, sin embargo, no lleva ningún registro general para propósitos de enteros. a diferencia de la mayoría de los archivos de registro de sombra en el procesador moderno y el sistema de múltiples núcleos, se puede acceder a todos estos ram de pila en cog en el nivel de instrucción, y todos estos cog pueden actuar como un gran núcleo único de propósito general si es necesario. La unidad de coma flotante es externa y contiene dos registros vectoriales de 80 bits. Itanium 128 128 Y 64 registros de predicado de 1 bit y 8 registros de rama. Los registros FP son de 82 bits. SPARC 31 32 El registro global 0 está cableado a 0. Utiliza ventanas de registro . IBM POWER 32 32 Y 1 enlace y 1 registro de recuento. Energía ISA 32 32 Y 1 enlace y 1 registro de recuento. Los procesadores que admiten la función Vector también tienen 32 registros vectoriales de 128 bits, Blackfin 8 datos, 2 acumuladores, 6 direcciones 0 Y apilar puntero y puntero de marco. Se utilizan registros adicionales para implementar bucles de sobrecarga cero y DAG de búfer circular (generadores de direcciones de datos). IBM Cell SPE 128 128 GPR, que pueden contener valores enteros, de dirección o de punto flotante [21] PDP-10 dieciséis Todos pueden usarse de forma general (entero, flotante, puntero de pila, salto, indexación, etc.). Cada palabra de memoria (o registro) de 36 bits también se puede manipular como media palabra, que puede considerarse una dirección (de 18 bits). Algunas instrucciones utilizan otras interpretaciones de palabras. En los procesadores PDP-10 originales, estos 16 GPR también correspondían a las ubicaciones de memoria principal (es decir, núcleo ) 0-15; una opción de hardware llamada "memoria rápida" implementó los registros como circuitos integrados independientes, y las referencias a las ubicaciones de memoria 0-15 se referían a los registros de circuitos integrados. Los modelos posteriores implementaron los registros como "memoria rápida" y continuaron haciendo que las ubicaciones de memoria 0-15 se refieran a ellos. Las instrucciones de movimiento toman operandos (registro, memoria) : MOVE 1,2es registroregistro y MOVE 1,1000es memoria a registro. PDP-11 8 0 R7 es en realidad el contador de programa. Cualquier registro puede ser un puntero de pila, pero R6 se usa para interrupciones y trampas de hardware. VAX dieciséis Alfa 31 31 Los registros R31 (entero) y F31 (punto flotante) están conectados a cero. 6502 1 dato, 2 índice 0 Contenido del 6502 Un registro (acumulador) para el almacenamiento de datos de propósito principal y la dirección de memoria (datos de 8 bits / dirección de 16 bits), X, Y son registros de índice indirecto y directo Los GPR también se utilizan para valores de punto flotante. Tres de los registros tienen usos especiales: R12 (puntero de argumento), R13 (puntero de cuadro) y R14 (puntero de pila), mientras que R15 se refiere al contador de programa. (respectivamente) y el registro SP son solo índices específicos. W65C816S 1 0 65c816 es el sucesor de 16 bits del 6502. X, Y, D (registro de página directa) son registros de condición y el registro SP son índices específicos únicamente. el acumulador principal extendido a 16 bits (C) [22] mientras mantiene 8 bits (A) para compatibilidad y el registro principal ahora puede direccionar hasta 24 bits (instrucción de datos de 16 bits de ancho / dirección de memoria de 24 bits). 65k 1 0 Sucesor directo de 6502, 65002 solo contenido A (acumulador) registro para almacenamiento de datos de propósito principal y extensión de datos a 32 bits y 64 bits de instrucciones de ancho, admite dirección virtual de 48 bits en modo software, X, Y siguen siendo registros de condición y permanecen en 8 bits y el registro SP son índices específicos pero aumentan a 16 bits de ancho. MeP 4 8 El procesador integrado en medios era un procesador de 32 bits desarrollado por toshiba, un conjunto de instrucciones 8080 modificado con solo registros A, B, C, D disponibles en todos los modos (8/16/32 bits) e incompatible con x86, sin embargo, contiene 80 bits Unidad de coma flotante compatible con x87. Microcontrolador 1 PIC 0 Microcontrolador 32 AVR 0 ARM de 32 bits (ARM / A32, Thumb-2 / T32) Varía (hasta 32) 14 r15 es el contador de programa y no se puede utilizar como GPR; r13 es el puntero de pila; r8-r13 se puede cambiar para otros (almacenados) en un conmutador de modo de procesador. Las versiones anteriores tenían direccionamiento de 26 bits, [23] y usaban bits superiores del contador de programa (r15) para las banderas de estado, lo que hacía que el registro fuera de 32 bits. ARM de 32 bits (pulgar) 8 dieciséis Versión 1 de Thumb, que solo admitía el acceso a los registros r0 a r7 [24] ARM de 64 bits (A64) [25] 31 32 El registro r31 es el puntero de la pila o está cableado a 0, según el contexto. MIPS 31 32 El registro entero 0 está cableado a 0. RISC-V 31 32 Registro entero 0 cableado a 0. La variante RV32E destinada a sistemas con recursos muy limitados tiene 15 registros enteros. Epifanía 64 (por núcleo) [26] Cada instrucción controla si los registros se interpretan como números enteros o como punto flotante de precisión simple. La arquitectura es escalable a 4096 núcleos con implementaciones de 16 y 64 núcleos disponibles actualmente. Uso El número de registros disponibles en un procesador y las operaciones que se pueden realizar utilizando esos registros tiene un impacto significativo en la eficiencia del código generado al optimizar los compiladores . El número de Strahler de un árbol de expresión proporciona el número mínimo de registros necesarios para evaluar ese árbol de expresión.