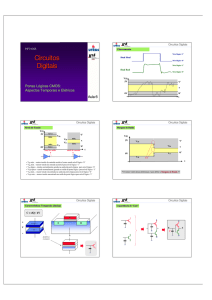

34. Elementos Básicos da Eletrônica Digital (Portugués) autor Frederico Oioli de Campos

Anuncio