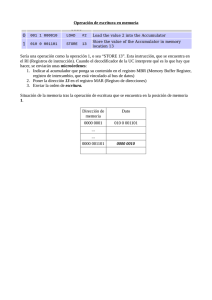

lOMoARcPSD|2193028 Examen 10 Octubre 2013, preguntas y respuestas Fundamentos de computadores (Universidad Complutense Madrid) StudeerSnel wordt niet gesponsord of ondersteund door een hogeschool of universiteit Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 FUNDAMENTOS DE COMPUTADORES 18 de junio de 2013. Examen parcial del 2º cuatrimestre. Nombre____________________________________________________________________________DNI_____________________________ Apellidos_____________________________________________________________________________________________Grupo________ Ejercicio 1 (3 puntos). Supongamos que definimos que un número natural es “bonito” si es menor que cien mil y además su valor puede obtenerse como una suma de números naturales de la forma 1+2+3+4+5+… Se pide: a) (1,5 puntos) Escribir un programa en lenguaje ensamblador del ARM tal que dado un número natural N decida si es o no bonito. El programa escribirá en la variable B un 1 si el número es bonito y un 0 en caso contrario. b) (1,5 puntos) Convertir el código anterior en una subrutina que reciba como entrada un número natural N y devuelva como salida un 1 si el número N es bonito y un 0 si no lo es. Escribir un programa en lenguaje ensamblador del ARM que llame a la subrutina, y tal que dado un vector A de M números naturales sea capaz de hallar cuántos números bonitos hay en el vector. El programa debe almacenar la cantidad de números bonitos hallada en la variable “cuenta_bonitos”. Nota: Se debe respetar el convenio del ARM visto en clase para llamadas a subrutinas. Además, en ambos apartados se deben incluir las directivas para reservar memoria y declarar las secciones (.data, .bss y .text) correspondientes. Ejercicio 2 (3 puntos). Se desea añadir al procesador multiciclo la instrucción movz, de tipo R: movz rd, rs, rt # si (BR[rt]==0) entonces BR[rd]BR[rs] Se pide: a) (1 punto) Completar la ruta de datos de la figura con los elementos que faltan para que se puedan ejecutar las instrucciones del procesador MIPS estudiadas en clase, incluyendo además los cambios que tendrían que realizarse para poder ejecutar esta instrucción. b) (1 punto) Añadir los estados necesarios a la máquina de estados (ver figura siguiente) para poder implementar el control de esta instrucción. c) (1 punto) Indicar los valores que van tomando todos los registros implicados en la ejecución de la instrucción MOVZ R1, R2, R3. El código de operación de la función MOVZ es 000000 y el valor de los campos SHAMT y FUNCT son 00000 y 100110, respectivamente. El estado actual de la máquina es: R1=0x00000017 R2=0x00110011 R3=0x00000000 PC=0x00003400 Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 Ejercicio 3 (3 puntos). Sea un computador con una memoria principal de 1MB, con una memoria cache de emplazamiento directo de 1KB con bloques de 128 bytes. La memoria es direccionable por bytes y el tamaño de palabra es de 4 bytes. Se pide: a) (0,5 puntos) Indicar el formato de la dirección para MP y para MC. b) (1 punto) En un momento dado sólo cuatro de las entradas de la cache contienen datos válidos, los contenidos del array de etiquetas de la cache (en hexadecimal) son los indicados en tabla inferior. Expresar en hexadecimal el rango de direcciones de memoria principal ubicadas en la memoria cache. Bloque de MC 0 1 2 3 4 5 6 7 Etiqueta 0x3A7 0x100 0x100 0x0D2 c) (1,5 puntos) Partiendo de la situación indicada en la tabla anterior, supongamos que un programa realiza la siguiente cadena de referencias en lectura (en hexadecimal): todas las palabras entre E9C38 y E9D7C ambos incluidos, todas las palabras entre las direcciones 4019C y 402AC, ambas incluidas, y todas las palabras entre las direcciones 34A84 y 34BC0, ambas incluidas. Indicar en cada caso los fallos que se producen e indicar cómo se queda el array de etiquetas de la memoria cache después de acceder a la última dirección. Ejercicio 4 (1 punto). El siguiente código en lenguaje ensamblador del ARM puede usarse para generar un retardo que permita la eliminación de rebotes en un pulsador, tal como hemos hecho por ejemplo en el laboratorio. bReb: finR: LDR R2,=200000 MOV R3,#0 CMP R3,R2 BEQ finR MUL R1,R0,R1 ADD R3,R3,#1 B bReb (salida del bucle, continua el programa) a) (0,75 puntos) Si sabemos que la frecuencia de reloj del ARM es de 66 MHz y hemos medido que desde que se produce la entrada en el bucle hasta que se produce la salida transcurren 2 décimas de segundo ¿cuál ha sido el valor de CPI en la ejecución del bucle? b) (0,25 puntos) Si en las mismas condiciones aumentamos la frecuencia del reloj hasta 100 MHz ¿cuánto tiempo transcurrirá desde que se entra en el bucle hasta que se sale? Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 FUNDAMENTOS DE COMPUTADORES 18 de junio de 2014. Examen parcial del 2º cuatrimestre. Nombre__________________________________________________________DNI___________________________ __ Apellidos_________________________________________________________________________Grupo________ Ejercicio 1 (2.5 puntos) Para el computador MIPS estudiado en clase, responder a las siguientes preguntas: a) (0.5 puntos) Qué instrucción/es, del repertorio de instrucciones del procesador MIPS estudiado en clase, se ven afectada/s y no se podrían ejecutar si se elimina de la ruta de datos el registro MDR, la entrada 1 del Mux que selecciona el dato que se escribe en el banco de registros, y por lo tanto dicho Multiplexor. b) (0.75 puntos) Partiendo de la ruta de datos completa del MIPS, se desea añadir una nueva instrucción Store con Direccionamiento Absoluto (SMDA). Se añade para ello un nuevo formato de instrucción con los siguientes campos (Op, Rs, dirección): El comportamiento de la instrucción SMDA sería el siguiente: SMDA Rs, dirección Mem[ExtCeros(dirección)] BR[rs] donde ExtCeros(dirección) extiende la dirección de 21 bits a 32 bits añadiendo ceros por la izquierda. Añade a la ruta de datos los cambios que tendrían que realizarse para poder ejecutar esta instrucción. c) (0.5 puntos) Añade los cambios necesarios en el diagrama de transición de estados del controlador para poder ejecutar correctamente esta nueva instrucción. d) (0.75 puntos) Indicar los cambios necesarios en la tabla de verdad del controlador (añadir las filas y columnas necesarias). Ejercicio 2 (3 puntos) Sea un computador con un procesador ARMv4. EL procesador cuenta con una memoria cache de emplazamiento directo de 256 bytes con bloques de 64 bytes, unificada para datos e instrucciones (se almacenan en la misma cache los bloques de instrucciones accedidos en la etapa FETCH y los bloques de datos accedidos durante las etapas que hacen acceso a memoria en las instrucciones ldr y str). a) (0.5 puntos) En dicho sistema se quiere ejecutar el siguiente programa. Explique razonadamente lo que hace el código. Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 .equ N, 16 .data A: .word N valores enteros separados por comas B: .word N valores enteros separados por comas .text start: b) c) d) e) ldr r0, =A ldr r1, =B mov r4, #N L1: ldr r2, [r0] ldr r3, [r1] add r2, r2, r3 and r2, r2, #0xF str r2, [r0] add r0, r0, #4 add r1, r1, #4 sub r4, #1 cmp r4, #0 bne L1 end: b. (0.25 puntos) Con direcciones de 32 bits, indicar el formato de la dirección para MP y para la MC. (0.5 puntos) El programa se enlaza ubicando la sección .data a partir de la dirección 0x0C000000, y la sección .text se coloca a continuación de la sección .data. Obtenga los rangos de direcciones que ocupan el array A, el array B y las instrucciones, indicando para cada rango el/los bloques de memoria correspondientes, y el marco de bloque (bloque de cache) y la etiqueta asociados. (1 punto) Determine el número de aciertos y fallos de cache que se producirían al ejecutar el código anterior, hasta la primera vez que se ejecuta la instrucción que está en la etiqueta end. (0.75 puntos) Suponga que el programador cambia el valor N por 32. Obtenga de nuevo los bloques de memoria en que se ubicarían los datos y las instrucciones. Explique cualitativa y razonadamente cómo afectaría este cambio a los fallos de cache (No es necesario calcular el nuevo número de fallos, sólo explicar lo que sucedería). Ejercicio 3 (3 puntos) Dado un vector V de N componentes se dice que es Melchoriforme si posee al menos un elemento Rubio. Un elemento V[i] es Rubio si satisface la siguiente expresión: N −1 ∑ v [ j ] =2∗v [ i ] j=0 Se pide: a) (1 punto) Una subrutina SumaVector( V, N ) que sume los N elementos del vector V, respetando el convenio de llamadas a subrutinas visto en clase. b) (2 puntos) Un programa que dado un vector V y su dimensión N decida si es Melchoriforme, utilizando la subrutina SumaVector. Ejercicio 4 (1.5 puntos) El código de un determinado programa está constituido por instrucciones máquina con la siguiente frecuencia de ejecución: aritméticas 50%, carga 20%, almacenamiento 10% y salto condicional 20% (donde la mitad de los saltos se toman). En cierto procesador las instrucciones consumen los siguientes ciclos: aritméticas 4, carga 5, almacenamiento 4, salto no tomado 3, salto tomado 4. a) (0.5 puntos) Calcula el CPI del procesador al ejecutar este programa. Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 b) (0.5 puntos) Sabiendo que el programa se ha ejecutado en 8.2ms, y que la frecuencia del procesador es de 1GHz, calcula el número de instrucciones que se han ejecutado. c) (0.5 puntos) Suponiendo que por cada 100 instrucciones ejecutadas se produce 1 fallo de cache, que implica una penalización de 300 ciclos de reloj, calcula el nuevo tiempo de ejecución del programa. ¿Cuál sería entonces el nuevo CPI? Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 FUNDAMENTOS DE COMPUTADORES 18 de junio de 2014. Examen parcial del 2º cuatrimestre. Nombre__________________________________________________________DNI___________________________ __ Apellidos_________________________________________________________________________Grupo________ Gedownload door Amor Sánchez ([email protected]) X 0010 0001 101011 (sw) X 0101 0001 000000 (tipo-R) X 0111 0001 000100 (beq) X 1001 0 0 1 00 (add) 1 1 MemtoReg MDRWrite 0 0 0 0 0 RegWrite 0 RegDest 0 0 X 0011 0 0 0011 XXXXXX X 0100 0 0 0 1 0100 XXXXXX X 0000 0 0 0 0 0101 XXXXXX X 0110 0 0 0 0 0110 XXXXXX X 0000 0 0 1 0 0111 XXXXXX X 1000 0 0 0 0 1000 XXXXXX X 0000 0 0 0 0 1001 XXXXXX 0 0000 1001 XXXXXX 1 1010 0 0 1 00 01 (sub) 0 0 0 1010 XXXXXX X 0000 0 1 0 11 00 (add) 0 0 0 1 10 00 00 (add) 10 (funct) 1 1 XXXXXX 1 00 (add) 0 0010 0 10 IorD 100011 (lw) 01 MemRead 0001 0 MemWrite 1 OutWrite PCWrite 1 ALUOp IRWrite 0001 ALUScrB Estado siguiente X ALUSrcA Zero XXXXXX BWrite op 0000 AWrite Estado actual lOMoARcPSD|2193028 1 1 Gedownload door Amor Sánchez ([email protected]) 1 1 0 1 0 1 0 1 0 0 0 1 1 lOMoARcPSD|2193028 FUNDAMENTOS DE COMPUTADORES 18 de junio de 2014. Examen final . Nombre__________________________________________________________DNI____________________________ _ Apellidos_________________________________________________________________________Grupo________ Ejercicio 4 (2.5 puntos) Para el computador MIPS estudiado en clase, responder a las siguientes preguntas: c) (0.5 puntos) Qué instrucción/es, del repertorio de instrucciones del procesador MIPS estudiado en clase, se ven afectada/s y no se podrían ejecutar si se elimina de la ruta de datos el registro MDR, la entrada 1 del Mux que selecciona el dato que se escribe en el banco de registros, y por lo tanto dicho Multiplexor. d) (0.75 puntos) Partiendo de la ruta de datos completa del MIPS, se desea añadir una nueva instrucción Store con Direccionamiento Absoluto (SMDA). Se añade para ello un nuevo formato de instrucción con los siguientes campos (Op, Rs, dirección): El comportamiento de la instrucción SMDA sería el siguiente: SMDA Rs, dirección Mem[ExtCeros(dirección)] BR[rs] donde ExtCeros(dirección) extiende la dirección de 21 bits a 32 bits añadiendo ceros por la izquierda. Añade a la ruta de datos los cambios que tendrían que realizarse para poder ejecutar esta instrucción. e) (0.5 puntos) Añade los cambios necesarios en el diagrama de transición de estados del controlador para poder ejecutar correctamente esta nueva instrucción. f) (0.75 puntos) Indicar los cambios necesarios en la tabla de verdad del controlador (añadir las filas y columnas necesarias). Ejercicio 5 (3 puntos) Sea un computador con un procesador ARMv4. EL procesador cuenta con una memoria cache de emplazamiento directo de 256 bytes con bloques de 64 bytes, unificada para datos e instrucciones (se almacenan en la misma cache los bloques de instrucciones accedidos en la etapa FETCH y los bloques de datos accedidos durante las etapas que hacen acceso a memoria en las instrucciones ldr y str). f) (0.5 puntos) En dicho sistema se quiere ejecutar el siguiente programa. Explique razonadamente lo que hace el código. Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 .equ N, 16 .data A: .word N valores enteros separados por comas B: .word N valores enteros separados por comas .text start: g) h) i) j) ldr r0, =A ldr r1, =B mov r4, #N L1: ldr r2, [r0] ldr r3, [r1] add r2, r2, r3 and r2, r2, #0xF str r2, [r0] add r0, r0, #4 add r1, r1, #4 sub r4, #1 cmp r4, #0 bne L1 end: b. (0.25 puntos) Con direcciones de 32 bits, indicar el formato de la dirección para MP y para la MC. (0.5 puntos) El programa se enlaza ubicando la sección .data a partir de la dirección 0x0C000000, y la sección .text se coloca a continuación de la sección .data. Obtenga los rangos de direcciones que ocupan el array A, el array B y las instrucciones, indicando para cada rango el/los bloques de memoria correspondientes, y el marco de bloque (bloque de cache) y la etiqueta asociados. (1 punto) Determine el número de aciertos y fallos de cache que se producirían al ejecutar el código anterior, hasta la primera vez que se ejecuta la instrucción que está en la etiqueta end. (0.75 puntos) Suponga que el programador cambia el valor N por 32. Obtenga de nuevo los bloques de memoria en que se ubicarían los datos y las instrucciones. Explique cualitativa y razonadamente cómo afectaría este cambio a los fallos de cache (No es necesario calcular el nuevo número de fallos, sólo explicar lo que sucedería). Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 FUNDAMENTOS DE COMPUTADORES 18 de junio de 2014. Examen final. Nombre__________________________________________________________DNI____________________________ _ Apellidos_________________________________________________________________________Grupo________ Gedownload door Amor Sánchez ([email protected]) X 0010 0001 101011 (sw) X 0101 0001 000000 (tipo-R) X 0111 0001 000100 (beq) X 1001 0 0 1 00 (add) 1 1 MemtoReg MDRWrite 0 0 0 0 0 RegWrite 0 RegDest 0 0 X 0011 0 0 0011 XXXXXX X 0100 0 0 0 1 0100 XXXXXX X 0000 0 0 0 0 0101 XXXXXX X 0110 0 0 0 0 0110 XXXXXX X 0000 0 0 1 0 0111 XXXXXX X 1000 0 0 0 0 1000 XXXXXX X 0000 0 0 0 0 1001 XXXXXX 0 0000 1001 XXXXXX 1 1010 0 0 1 00 01 (sub) 0 0 0 1010 XXXXXX X 0000 0 1 0 11 00 (add) 0 0 0 1 10 00 00 (add) 10 (funct) 1 1 XXXXXX 1 00 (add) 0 0010 0 10 IorD 100011 (lw) 01 MemRead 0001 0 MemWrite 1 OutWrite PCWrite 1 ALUOp IRWrite 0001 ALUScrB Estado siguiente X ALUSrcA Zero XXXXXX BWrite op 0000 AWrite Estado actual lOMoARcPSD|2193028 1 1 Gedownload door Amor Sánchez ([email protected]) 1 1 0 1 0 1 0 1 0 0 0 1 1 lOMoARcPSD|2193028 Fundamentos de Computadores 17 de Junio de 2015. Examen Parcial 2º Cuatrimestre Nombre:____________________________________ DNI: ________________ Apellidos: ___________________________________________ Grupo: _____ Ejercicio 1. (3 puntos) Responde a las siguientes cuestiones, suponiendo que el vector V está almacenado a partir de la dirección de memoria 0x0C000000 y que el código se encuentra a continuación de los datos. El código almacena en la variable CuentaTotal el sumatorio de todos los números positivos que contiene el vector. Para realizar este sumatorio, se utilizan dos subrutinas: Cuenta y Averigua. El estudiante sólo necesita saber de la subrutina Averigua que como parámetro de entrada recibe el entero V[i] y como resultado devuelve: (1) el valor de V[i], si V[i] es positivo; (2) 0, si V[i] es negativo. .data V: .word 1,2,­3,4,5,9,17,­15,20,12 N: .word 10 .bss CuentaTotal: .space 4 .text start: ldr r0,=V ldr r1,=N bl Cuenta ldr r1, =CuentaTotal str r0, [r1] end: b end Cuenta: bucle: fin_bucle: PRÓLOGO_1 mov r2, #0 mov r5, #0 ldr r4, [r1] cmp r2, r4 beq fin_bucle ldr r3, [r0, r2, lsl #2] bl Averigua add r5, r5, r0 add r2, r2, #1 b bucle move r0, r5 EPÍLOGO_1 mov pc, lr a) (0,5 ptos.) Indicar el valor de la dirección de la etiqueta Cuenta, es decir, a qué dirección salta la instrucción bl Cuenta. Razona la respuesta. b) (1 pto.) La subrutina Cuenta no es correcta considerando el estándar de llamadas a procedimientos de ARM. Modificar el código de dicha subrutina para que respete este estándar. c) (0,5 ptos.). Codificar el prólogo y el epílogo de la subrutina Cuenta, teniendo en cuenta las modificaciones del apartado b. d) (1 ptos.). Codificar en ensamblador la subrutina Averigua. Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 Ejercicio 2 (3 puntos) a) (1 punto) En la ruta de datos del procesador MIPS visto en clase se ha cambiado el banco de registros. Ahora el banco de registros tiene un sólo puerto de lectura en vez dos, como se muestra en la figura. Completa la ruta de datos para que puedan seguir realizándose en todas las instrucciones las transferencias A <­ Rs y B <­ Rt. b) (1 punto) Modifica el diagrama de estados para que se puedan ejecutar correctamente todas las instrucciones que hemos considerado para el diseño del procesador. Añade nuevos estados si es necesario e indica si es necesario añadir alguna señal de control nueva. Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 c) (1 punto) Indicar los valores que van tomando todos los registros internos de la ruta de datos al final de cada etapa en la ejecución de la instrucción Add R1, R2, R3, sabiendo que el código de operación (OP) de las instrucciones aritmético­lógicas es (000000)2, el valor de los campos SHAMT y FUNCT para la instrucción Add es (00000)2 y (100000)2 respectivamente, y que el estado actual de la máquina es: R1=0x00000017, R2=0x00110011, R3=0x00000000 y PC=0x00003400. Recordar que el formato de las instrucciones Tipo­R es: Ejercicio 3 (3 puntos) Una jerarquía de memoria está compuesta por una memoria principal de 16 Mbytes y una cache con emplazamiento directo de 16 Kbytes. El tamaño de bloque es de 256 bytes. Sobre esta jerarquía de memoria se ejecuta un millón de accesos de lectura, obteniéndose una tasa de aciertos de 0,995. Se supone que el tiempo de acceso a la memoria principal es de 20 ns, el tiempo de acceso a la cache es de 1 ns y la penalización por fallo es de 400 ns. Responde a las siguientes cuestiones (0,5 puntos cada apartado): Nota: Todos los datos numéricos del problema están en decimal. Las respuestas numéricas pueden darse en el sistema decimal o hexadecimal, a elección del estudiante. a) Muestra el formato de la dirección para la Mp y la cache. b) Si el bloque nº 87 de la Mp tiene que llevarse a la cache ¿qué nº de bloque de cache se le asigna? c) ¿A cuántos bloques de Mp le corresponde el mismo bloque en la cache? Indica el nº del primer y el último bloque de Mp a los que les corresponde alojarse en el bloque 22 de la cache. d) ¿Cuál es el tiempo medio de acceso a memoria? e) ¿Cuánto se tarda en ejecutar la secuencia de accesos a memoria descrita? f) ¿Qué ganancia de velocidad se obtiene respecto del mismo sistema, pero sin la cache? Ejercicio 4 (1 punto) Al ejecutar un programa, P, en un computador, C , el rendimiento obtenido ha sido 400 MIPS. La frecuencia de reloj es de 1,66 GHz. a) (0,5 puntos) ¿Cuál ha sido el número medio de ciclos de reloj por instrucción? b) (0,5 puntos) Suponemos que P está compuesto por tres tipos de instrucciones del repertorio de C, cuya frecuencia de ejecución y duración en ciclos de reloj es, respectivamente, la siguiente: · Acceso a memoria: 30% , 5 ciclos · Aritméticas: 50%, 4 ciclos · Salto condicional: 20%, 4 ciclos si el salto se toma, 3 ciclos si no se toma. En promedio, de cada 100 saltos condicionales ejecutados ¿cuántos se han tomado? Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 Fundamentos de Computadores 16 de Junio de 2016. Examen Parcial 2º Cuatrimestre Nombre:____________________________________ DNI: ________________ Apellidos: ___________________________________________ Grupo: _____ Ejercicio 1 (3 puntos) Un procesador cuenta con una jerarquía de memoria que está compuesta por una memoria principal de 64MB y una cache con emplazamiento directo de 4KB con 16 bloques. En dicho procesador se ejecuta un código que genera accesos de lectura a memoria consecutivos a todas las direcciones entre 0x0300800 y 0x03017FF. a) (0.25 puntos) Muestra el formato de la dirección para la Mp y la cache b) (0.75 puntos) Indica los fallos de cache que provocará la ejecución del código indicando los bloques sobre los que se produce el fallo, asumiendo que la cache está inicialmente vacía c) (0.75 puntos) Indica cuál será el contenido del directorio (array de etiquetas o tags) tras finalizar la ejecución Supongamos que a continuación vuelve a ejecutarse el mismo código una segunda vez: d) (0.5 puntos) ¿Cuántos fallos de cache se producirían la segunda vez? e) (0.75 puntos) Si el tiempo de acceso a la memoria principal es de 20 ns, el tiempo de acceso a la cache es de 1 ns y la penalización por fallo es de 400 ns, indica cuál sería el tiempo medio de acceso a memoria y la ganancia que se obtiene respecto a un sistema sin cache (teniendo en cuenta las dos ejecuciones del código). Ejercicio 2 (1 punto) En un determinado computador con procesador ARM a una frecuencia de reloj de 1.5GHz se ejecuta el siguiente programa: L1: mov r4, ldr r5, mov r6, cmp r4, bge L2 ldr r0, add r6, add r4, b L1 #0 =A #0 #128 [r5, r4, lsl #2] r6, r0 r4, #1 L2: b . a) Suponiendo que las instrucciones aritmético lógicas tardan 4 ciclos, las instrucciones de carga tardan 5 ciclos, los saltos tomados 4 ciclos y los no tomados 3 ciclos, obtener el número medio de ciclos por instrucción para este programa (CPI) (hasta la primera vez que se ejecuta la instrucción b . ). b) En el apartado anterior se suponía un comportamiento ideal en el que todos los accesos a memoria se realizan en 1 ciclo de reloj, en cuyo caso las instrucciones de carga tardan los 5 ciclos de reloj indicados. Supongamos ahora que el sistema tiene una memoria cache en la que se produce un fallo por cada 16 ejecuciones de la instrucción ldr r0, [r5, r4, lsl #2] y que la penalización por fallo es de 100 ciclos. Teniendo en cuenta el tiempo adicional debido a las penalizaciones, calcular de nuevo el CPI. Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 Ejercicio 3 (3 puntos) Dado un vector, A, de 3*N componentes, se desea obtener un nuevo vector, B, de N componentes donde cada componente de B es la suma módulo 32 de una tripleta de elementos consecutivos de A. Es decir: B[0] = (A[0]+A[1]+A[2]) mod 32, B[1] = (A[3]+A[4]+A[5]) mod 32, etc Se pide: a) (1.25 puntos) Escribir un programa en lenguaje ensamblador del ARM que implemente el cálculo descrito de acuerdo con el siguiente código C equivalente: #define N 4 int A[3*N] = {una lista de 3*N valores}, int B[N]; int i, j=0; void main (void) { for (i=0; i<N; i++){ B[i] = sum_mod_32(A, j, 3); j=j+3 } } donde la subrutina sum_mod_32(V,p,m) devuelve como resultado la suma módulo 32 de m elementos consecutivos del vector V tomados a partir de la posición p. b) (1.25 puntos) Escribir el código ensamblador de la subrutina sum_mod_32, de acuerdo al siguiente código C equivalente: sum_mod_32 (int A[ ], int j, int len) { int i, sum=0; for (i=0; i<len; i++) sum = sum + A[j+i]; sum=mod_power_of_2(sum,5); return sum; } donde la subrutina mod_power_of_2(num, exp), siendo num un entero positivo y exp un entero mayor que 0 y menor que 32, devuelve como resultado el valor de (num mod 2^exp). Por ejemplo, si invocamos a la función como: mod_power_of_2(34, 5), la función devolvería como salida: ((34) mod (2^5))=(34 mod 32)=2. c) (0.5 puntos) El siguiente código ensamblador es una implementación de la subrutina mod_power_of_2, sin prólogo ni epílogo. Añadir el prólogo, el epílogo y añadir también comentarios ilustrativos a las instrucciones que expliquen cómo se va realizando el cálculo. Ayuda: Para entender el flujo del programa se sugiere considerar un caso concreto; por ejemplo, el caso del cálculo de módulo 25. mod_power_of_2: .... prólogo .... loop3: endloop3: mov mov mov r3,#0 r4,#0 r2,#1 cmp bge add mov add b and r4,r1 endloop3 r3,r3,r2 r2,r2, lsl #1 r4,r4,#1 loop3 r0,r0,r3 .... epílogo .... Nota.- En todos los apartados se debe respetar el estándar de llamadas a subrutinas estudiado en clase, y las variables pueden ubicarse en registros o en memoria (global o pila según corresponda). Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 Ejercicio 4. (3 puntos) Se desea añadir al procesador MIPS estudiado en clase la instrucción Load Upper Immediate, cuyo nemotécnico sería: LUI Rx, Immediate codificada como una instrucción Tipo-I: 6 5 5 110011 not used Rx 16 Immediate y cuya descripción se correspondería con el siguiente movimiento registro a registro: BR(Rx) <- (Immediate << 16) , PC <- PC + 4 es decir, el contenido del campo Immediate de la instrucción se desplaza 16 posiciones a la izquierda, rellenando con ceros por la derecha, y se almacena en el registro destino. a) (1 punto) Indicar los cambios necesarios en la ruta de datos del MIPS estudiada en clase. b) (1 punto) Indicar los cambios necesarios en el diagrama de transición de estados del controlador. c) (1 punto) Indicar los cambios necesarios en la tabla de verdad del controlador. PCWrite IorD MemWrite IRWrite RegDst AWrite ALUSrcA OutWrite ALUop Control de ALU RegWrite 1 MUX 1 0 4 busW 1 2 0 MUX MDR 1 MDRWrite MemtoReg <<2 Instruc. [15-0] BWrite Extensión de signo MemRead 3 Gedownload door Amor Sánchez ([email protected]) ALUSrcB ALUout busB Zero ALU RW busA A 0 Instrucción [15-11] DW RB MUX DR Banco de registros Instrucción [20-16] IR 1 B RA ADDR MUX Instrucción [25-21] Memoria MUX PC 0 0 lOMoARcPSD|2193028 Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 1 a) 18 8 Bloque P Etiqueta 14 M P 4 8 b) Contamos un acceso por dirección entre 0x0300800 y 0x03017FF La primera dirección corresponde al comienzo del bloque 0x03008, que le corresponde el bloque de cache M = 8 con etiqueta 0x0300. La última dirección corresponde al final del bloque 0x03017, al que le corresponde el bloque de cache M = 7, con etiqueta 0x0301. Por lo tanto se han accedido todos los bloques entre 0x03008 y el 0x03017, 16 en total. Se produce un fallo por bloque accedido, por tanto 16 fallos. c) M 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 V 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 Etiqueta 0x0301 0x0301 0x0301 0x0301 0x0301 0x0301 0x0301 0x0301 0x0300 0x0300 0x0300 0x0300 0x0300 0x0300 0x0300 0x0300 d) Como todos los bloques accedidos están en cache, no se produce ningún fallo de cache e) Con cache: Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 T = Nº Accesos x Tiempo de acceso a cache + Nº de fallos x Penalización por fallo = = 2*2^12 x 1ns + 16 x 400 ns = 14,6 ms Sin cache: T = Nº Accesos x Tiempo de acceso a MP = 2*2^12 * 20 ns = 163,8 ms Speedup = 163,8 / 14,6 = 11,2 2 a) Nº de loads = 1 + 1*128 = 129 Nº de stores = 0 Nº de aritmetico lógicas = 2 + 3*128 + 1 = 387 Nº de saltos tomados = 1 + 1*128 +1 = 130 Nº de saltos no tomados = 128 CPI = (129*5 + 387*4 + 130*4 + 128*3) / (129+387+130+128) = 3097 / 774 = 4,0013 b) Tenemos que sumar al número de ciclos los ciclos adicionales de penalización: CPI = (3097 + 128/16 * 100) / 774 = 5,0349 3 .extern _stack .equ N, 4 .data A: .word .bss B: .space N*4 .text start: loop1: 20,12,63,45,140,34,20,30,40,45,55,65 ldr mov ldr ldr mov mov sp,=_stack fp,#0 r6,=A r7,=B r5, #0 r4, #0 @ r5 = loop counter i @ R4 = Index j cmp bge r5, #N endloop1 @ if loop exhausted, go to mov mov mov r0,r6 r1,r4 r2,#3 bl sum_mod_32 str add add b r0,[r7,r5,lsl#2] r5,r5,#1 r4,r4,#3 loop1 end @ prepare call parameters @ store B[i] @ i++ @ Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 endloop1: b . // Subroutine sum_mod_32 (non-leaf) sum_mod_32: push {r4-r8,fp,lr} add fp,sp,#4*(7-1) @ PROLOG mov mov mov mov r4,#0 r5,#0 r6,r0 r7,r1 @ @ @ @ mov r8,r2 @ number of elements to cmp bge add ldr add add b r4,r8 endloop2 r0,r7,r4 r3,[r6,r0,lsl#2] r5,r5,r3 r4,r4,#1 loop2 mov mov bl r0,r5 r1,#5 mod_power_of_2 r4 = i r5=sum dir A initial position of the addition add loop2: endloop2: sub pop mov sp,fp,#4*(7-1) {r4-r8,fp,lr} pc, lr @ r0 = i+j @ r3=A[i+j] @ increase sum @i++ @ EPILOG // Subroutine sum_mod_32 (leaf) mod_power_of_2: push {r4,fp} add fp,sp,#4*(2-1) @ PROLOG mov mov mov r3,#0 r4,#0 r2,#1 @ intialize the mask @ i: loop counter @ auxiliary value to create the cmp r4,r1 @ compare the counter to the bge add lsl endloop3 r3,r3,r2 r2,r2,#1 @ update the mask @ move the "one" to the next add b r4,r4,#1 loop3 @ i++ and r0,r0,r3 @ r0 = r0 mod 2^exponent mask loop3: exponent position endloop3: sub pop mov sp,fp,#4*(2-1) {r4,fp} pc,lr @ EPILOG .end 4 Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 a) PCWrite IorD IRWrite MemWrite RegDst AWrite ALUSrcA OutWrite ALUop Control de ALU RegWrite MUX 0 4 1 2 0 1 2 ALUSrcB <<2 BWrite 2 Extensión de signo << 16 Instruc. [15-0] MDRWrite 3 MUX MDR MemRead MemtoReg b) A <- BR( rs ) B <- BR( rt ) op = ‘110011 ’ 11 BR(rt) <-Inst[15-0] << 16 c) Gedownload door Amor Sánchez ([email protected]) ALUout busB busW 1 Zero 1 ALU RW busA A RB 0 Instrucción [15-11] DW Banco de registros Instrucción [20-16] DR MUX 1 IR Memoria ADDR B RA MUX Instrucción [25-21] MUX PC 0 0 X 0010 0001 101011 (sw) X 0101 0001 000000 (tipo-R) X 0111 0001 000100 (beq) X 1001 0 0 1 1 MemtoReg 0 1 0 0 0 1 0 0 0 0 0 0 00 (add) RegWrite 1 01 RegDest 0 0 MDRWrite IorD 100011 (lw) MemRead 0001 MemWrite 1 OutWrite PCWrite 1 ALUOp IRWrite 0001 ALUScrB Estado siguiente X ALUSrcA Zero XXXXXX BWrite op 0000 AWrite Estado actual lOMoARcPSD|2193028 0 0001 110011 (LUI) X 1011 0 0 0010 XXXXXX X 0011 0 0 0011 XXXXXX X 0100 0 0 0 1 0100 XXXXXX X 0000 0 0 0 0 0101 XXXXXX X 0110 0 0 0 0 0110 XXXXXX X 0000 0 0 1 0 0111 XXXXXX X 1000 0 0 0 0 1000 XXXXXX X 0000 0 0 0 0 1001 XXXXXX 0 0000 0 0 1 00 01 (sub) 0 0 0 1010 XXXXXX X 0000 0 1 0 11 00 (add) 0 0 0 1011 XXXXXX X 0000 0 0 0 0 1 0 1 1 10 10 00 00 (add) 00 (add) 10 (funct) 1 1 1 Gedownload door Amor Sánchez ([email protected]) 1 1 0 01 0 1 0 1 0 0 00 10 1 0 1 1 lOMoARcPSD|2193028 Fundamentos de Computadores 2ºC. 31 de mayo de 2019. Examen 2º Parcial (todos los apartados, 10 puntos). Examen Final (solo apartados en negrita, 5.5 puntos). Nombre:____________________________________ DNI: _________________ Apellidos: ____________________________FINAL/PARCIAL:_______________ Ejercicio 1. Queremos añadir una memoria cache a un procesador con arquitectura de 32 bits (bus de direcciones es de 32 bits y bus de datos de 32 bits). La Memoria Principal (MP) direcciona 4Gpalabras. La Memoria Cache (MC) direcciona 1 Kpalabras. Los bloques de memoria son de 16 palabras. a) (0.25 p) Muestra el formato de la dirección desde el punto de vista de la MP y de la MC. DirMP: 32bits : B:28bits, P:4bits DirMC: 10bits : E:22bits, M:6bits, P:4bits b) (0.25) ¿Cuál es el tamaño de la MP y de la MC en Bytes?(en la MC incluye las etiquetas del directorio y dos bits, uno de validez y otro de escritura por cada marco) MP: 2^32Palabras=2^32*2^2B =16GB MC: 2^10palabras*2^2B+2^6*(22+2)bits=4KB+64*4B=4KB+256B=1280B c) (0.25 p) ¿Qué bloques de MP ocupan los primeros 16KB? 16KB=4Kpal: 12 bits=> Nº de bloques ocupados 2^(12-4)=2^8=256 primeros bloques. d) (0.5 p) Traza a qué marcos de MC van los primeros 16KBytes de MP y con qué etiquetas. B0..B63 ->M0..M63 Etiqueta b0..00 B64..B127 ->M0..M63 Etiqueta b0..01 B128..B191 ->M0..M63 Etiqueta b0..10 B192..B255 ->M0..M63 Etiqueta b0..11 e) (0.25) Cuantos fallos se producen al leer las palabras que ocupan los primero 16KB de forma secuencial. Un fallo por bloque de MP que se trae a MC. 256 fallos f) (0.5) Si el TMP=20ns, TMC=1ns y Tfallo=100ns. ¿Cuantas veces es más rápido con MC que sin ella? TiempoMP=4Kaccesos*20ns=4*1024*20ns=81,92µs TiempoMC=4Kaccesos*1ns+256*100ns=29,696 µs SpeedUp=81,92µs/29,696 µs=2,76 veces más rápido con MC. g) (1 p) Disponemos de un Chip SRAM que tiene los siguientes puertos: CE#,OE# WE#, A9…A0 y D8…D0. Utilizando el chip anterior diseña una memoria cache (MC) que maneje 1Kpalabra (palabra=32bits). Nota: Solo direccionar palabras, no bytes. Las lineas de direcciones y de datos del chip indican que es capaz de direccionar 2^10 bytes. Tan solo habrá que situar 4 chips en paralelo (cuatro columnas) para conseguir 2^10 palabras. • No es necesario decodificador. • CE#,OE# WE# de cada módulo conectados directamente a CE#,OE# WE# de la entrada. • A11..A2 conectados directamente al puerto de entrada de direcciones (si el bus de direcciones es tamaño palabra sería las líneas A9..A0). Dar ambas soluciones por válidas. • El puerto de datos B31..B0 lo forman los 4 puertos de datos de los chips. B31..B24<->D8..D0 de 1ª columna, B23..B16<->D8..D0 de 2ª columna, B15..B8 <->D8..D0 de 3ª columna, B7..B0 <->D8..D0 de 4ª columna, Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 Ejercicio 2. Supongamos un programa de 256KB formado exclusivamente por instrucciones de 32 bits. Si se ejecuta en un procesador a una frecuencia de 1 GHz y se obtienen un rendimiento de 200 MIPS. a) (0.5) Calcula el CPI CPI= (10^9ciclos/s)/(200*10^6instr/s)= 5 b) (0.5 p) Calcula el tiempo de ejecución del programa suponiendo que cada instrucción se ejecuta una sola vez. Tiempo=256*2^10 B * 1instr/4B /(200 *10^6 instr/s)=327 µs Ejercicio 3. Añadir al procesador MIPS una instrucción que copie el valor de un registro en otro registro aplicando un número de desplazamientos aritméticos sobre el registro fuente, de forma similar a como lo hace la instrucción MOV de ARM. La instrucción en ensamblador sería: MOV Rt,Rs,#inmediato que se codifica como: y debe hacer la siguiente transferencia lógica: BR(Rt) <- DespArit(BR(Rs),inmediato), PC <- PC + 4 Se dispone de un módulo combinacional para implementar la función DespArit(Din,N), que hace N desplazamientos aritméticos, a la izquierda si N es positivo y a la derecha N si es negativo. 32 / / 32 Din Dout N 32 / Se pide: a) (1 punto) Indicar los cambios necesarios en la ruta de datos del MIPS estudiada en clase. Conectar: • Din a la salida del Registro A • N a la salida de ExtSign • Dout a la entrada b10 de Mux MemtoReg (Señal de control de 2 bits) Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 b) (1 punto) Indicar los cambios necesarios en el diagrama de transición de estados del controlador. Estado 1->Estado 11 si opcod=’MOV’ Estado11(BR(Rt) <- DespArit(BR(Rs),inmediato)) Como es un módulo combinacional se puede hacer todo en un ciclo (si da tiempo) Estado 11-> Estado 0 c) (1 punto) Indicar los cambios necesarios en la tabla de verdad del controlador. E0000 si OP=’MOV’ salto a E1011 (Señales de control igual) E1011: • Todas las escrituras en registros y memoria a 0 excepto RegWrite=1 • Todas las señales de control de multiplexores indiferentes excepto RegDst=0 y MemtoReg=10 (en esta columna habrá que completar a 2 bits) Gedownload door Amor Sánchez ([email protected]) X 0101 0001 000000 (tipo-R) X 0111 0001 000100 (beq) X 1001 0001 (mov) X 1011 0 0 MemtoReg 0 0 0 1 0 0 0 0 0 0 1 XXXXXX X 0011 0 0 0011 XXXXXX X 0100 0 0 0 1 0100 XXXXXX X 0000 0 0 0 0 0101 XXXXXX X 0110 0 0 0 0 0110 XXXXXX X 0000 0 0 1 0 0111 XXXXXX X 1000 0 0 0 0 1000 XXXXXX X 0000 0 0 0 0 1001 XXXXXX 0 0000 1001 XXXXXX 1 1010 0 0 1 00 01 (sub) 0 0 0 1010 XXXXXX X 0000 0 1 0 11 00 (add) 0 0 0 1011 XXXXXX X 0000 0 0 0 0 1 1 10 00 00 (add) 00 (add) 10 (funct) 1 0 0010 0 10 RegDest RegWrite 1 00 (add) MDRWrite IorD 101011 (sw) MemRead 0001 OutWrite 1 0010 01 ALUOp 1 X 0 0 ALUScrB 0 100011 (lw) 1 ALUSrcA 0 0001 0 BWrite 1 AWrite 1 MemWrite 0001 PCWrite X IRWrite XXXXXX 0000 Estado siguiente Zero op Estado actual lOMoARcPSD|2193028 1 1 1 1 0 01 0 1 0 1 0 0 00 10 1 1 1 1 Ejercicio 4. Se quiere cambiar una imagen de formato RGBA a formato CMYK para imprimirla. Para ello se utiliza el siguiente código de alto nivel. typedef struct _pixel_32_t { unsigned char R; %Canal de Rojo unsigned char G; %Canal de Verde unsigned char B; %Canal de Azul unsigned char A; %Canal de Transparencia } pixel32; %Un pixel ocupa una palabra de 32 bits. pixel32 rgba2cmyk(pixel32 rgba); %Se desconoce su implementación pues se suministra compilada %rgba es una palabra que contiene el pixel original RGBA. %Devuelve una palabra con el pixel en formato CMYK. void TraduceImagen(pixel32 *rgba,int N, int M) {%La imagen es un array de N*M pixeles(palabras) %pixel32 *rgba: será la dirección de memoria base del array. %N es el número de filas y M es el número de columnas for (int i=0;i<N*M;i++) rgba[i] = rgba2cmyk(rgba[i]); } a) (2 puntos) Escribir en ensamblador la subrutina TraduceImagen acorde al estándar AAPCS visto en clase. Gedownload door Amor Sánchez ([email protected]) lOMoARcPSD|2193028 b) (1 punto) Escribir un programa en ensamblador que prepare la pila y llame a la subrutina TraduceImagen. Debe asumir que las variables pixel32 mirgba[N],[M], int N e int M son variables creadas en otro fichero. .extern .extern .extern .extern .extern .global mirgba N M rgba2cmyk _stack start .text TraduceImagen: push {R4-R8,FP,LR} add FP,SP,#6*4 mov R4,R0 //&rgba mov R5,R1 //N mov R6,R2 //M mov R7,#0 //i=0 mul R8,R5,R6 //N*M fi: cmp R7,R8 bge finfi ldr R0,[R4,R7,LSL #2] bl rgba2cmyk str R0,[R4,R7,LSL #2] add R7,R7,#1 b fi finfi: pop {R4-R8,FP,LR} mov PC,LR start: ldr sp,=_stack mov fp,#0 ldr R0,=mirgba //&mirgba ldr R1,=N ldr R1,[R1] //Dato N ldr R2,=M ldr R2,[R2] //Dato M bl TraduceImagen b . .end Gedownload door Amor Sánchez ([email protected])