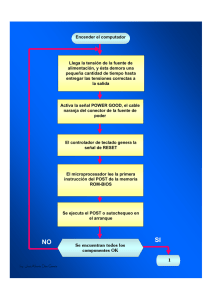

Departamento de Sistemas e Informática Microprocesador 8086 Digital II Presentación de Docentes y Material è è Docentes: è Ing. Silvia Domizi è Ing. Diego Alegrechi Material de Cátedra – (disponible en www.dsi.fceia.unr.edu.ar) 1. 2. 06/10/2014 Intel 8086 - Datasheet Los microprocesadores Intel - B. Brey – 3º Edición – Prentice Hall (Cap 7). Microprocesador 8086 – Digital II 2 Microprocesadores y Microcontroladores Microprocesador Dispositivo electrónico semiconductor que incluye la ALU, conjunto de registros y circuitos de control en un mismo chip. ➢ Incluye un set de instrucciones para manipular los datos y comunicarse con los periféricos. ➢ No incluye memorias internas. Posee buses de datos y direcciones que posibilitan la conexión con memorias de programas y datos externas al chip del microprocesador. ➢ Microcontrolador Microprocesador más memorias y periféricos específicos integrados en un mismo chip (temporizadores, conversores A/D, D/A, puertos UART, CAN, SPI, I2C, USB, ETHERNET, etc). ➢ Sistemas totalmente dedicados a resolver problemas específicos (sistemas embebidos). ➢ 06/10/2014 Microprocesador 8086 – Digital II 3 Microprocesador 8086 - Características Principales Características Procesador de 16 bits (puede operar en 8 ó 16 bits pero los buses internos son todos de 16 bits). ➢ Hasta 1 Mbyte de memoria direccionable (mapeable) – Bus de 20 lineas de direcciones. ➢ Espacio de memoria para periféricos de entrada salida de 64 Kbytes. ➢ Los buses de datos y direcciones están multiplexados temporalmente. ➢ La memoria o las memorias donde se aloja el código del programa y los datos es externa al microprocesador. El 8086 NO posee ningún tipo de memoria integrada para código o datos. ➢ ➢ Velocidad de operación (5MHz, 8MHz, 10MHz) ➢ Encapsulado de 40 pines. 06/10/2014 Microprocesador 8086 – Digital II 4 Microprocesador 8086 - Arquitectura Arquitectura del 8086 Estos microprocesadores tienen dos unidades inteligentes conectadas internamente: EU BIU Unidad de ejecución (Execution Unit). Unidad de interfaz con el Bus (Bus Interface Unit). 06/10/2014 Microprocesador 8086 – Digital II 5 Microprocesador 8086 - Arquitectura La unidad de ejecución (EU) Se encarga de decodificar las instrucciones cargadas (Fetched) por la BIU, generar las señales de control y ejecutar las instrucciones 06/10/2014 Microprocesador 8086 – Digital II 6 Microprocesador 8086 - Arquitectura La unidad de ejecución (EU) Proporciona las direcciones lógicas al BIU. Una dirección lógica está formada de dos direcciones, la primera indica el segmento en el cual se está trabajando y la otra indica el offset, o desplazamiento, de este segmento; esto es segment:offset. 06/10/2014 Microprocesador 8086 – Digital II 7 Microprocesador 8086 - Arquitectura La unidad de ejecución (EU) Posee una unidad aritmética lógica (ALU) de 16 bits, un registro de banderas y un conjunto de registros de propósito general. El registro de banderas contiene 6 banderas de estado y 3 banderas de control que se pueden manipular por los programas para alterar las operaciones del procesador . 06/10/2014 Microprocesador 8086 – Digital II 8 Microprocesador 8086 - Arquitectura La Unidad de Interfase con el Bus (BIU) Es la responsables de la comunicación externa del procesador. Esta unidad de proceso se encarga de traducir las direcciones lógicas a direcciones físicas de la memoria con ayuda de los registros de segmento DS, SS, ES, CS e IP. 06/10/2014 Microprocesador 8086 – Digital II 9 Microprocesador 8086 - Arquitectura La Unidad de Interfase con el Bus (BIU) Se encarga de todas las operaciones de Bus (comunicación con el exterior), que incluyen los ciclos de lectura y escritura, así como también la carga de las instrucciones para la EU (Instruction Fetching). Las instrucciones son cargadas en una cola de instrucciones. 06/10/2014 Microprocesador 8086 – Digital II 10 Microprocesador 8086 - Arquitectura La Unidad de Interfase con el Bus (BIU) La EU puede trabajar a una máxima eficiencia si se le provee constantemente de instrucciones y datos para procesar. Esa es la principal función de la cola de pre-carga de instrucciones de la BIU Concepto de Pipeline 06/10/2014 Microprocesador 8086 – Digital II 11 Microprocesador 8086 - Arquitectura MODELO DE PROGRAMACIÓN DEL 8086. 06/10/2014 Microprocesador 8086 – Digital II 12 Microprocesador 8086 - Arquitectura El modelo de programación del 8086 06/10/2014 Microprocesador 8086 – Digital II 13 Microprocesador 8086 - Arquitectura Registros de datos o de propósito general AX, BX, CX, DX: pueden utilizarse bien como registros de 16 bits o como dos registros separados de 8 bits (byte superior e inferior) cambiando la X por H o L según queramos referirnos a la parte alta o baja respectivamente. 06/10/2014 Microprocesador 8086 – Digital II 14 Microprocesador 8086 - Arquitectura Registros de datos o de propósito general AX = Acumulador. Es el registro principal, es utilizado en las instrucciones de multiplicación y división y en algunas instrucciones aritméticas especializadas, así como en ciertas operaciones de carácter específico como entrada, salida y traducción. Obsérvese que el 8086 es suficientemente potente para realizar las operaciones lógicas, la suma y la resta sobre cualquier registro de datos, no necesariamente el acumulador. 06/10/2014 Microprocesador 8086 – Digital II 15 Microprocesador 8086 - Arquitectura Registros de datos o de propósito general BX = Base. Se usa como registro base para referenciar direcciones de memoria con direccionamiento indirecto, manteniendo la dirección de la base o comienzo de tablas o matrices. De esta manera, no es preciso indicar una posición de memoria fija, sino la número BX (así, haciendo avanzar de unidad en unidad a BX, por ejemplo, se puede ir accediendo a un gran bloque de memoria en un bucle). 06/10/2014 Microprocesador 8086 – Digital II 16 Microprocesador 8086 - Arquitectura Registros de datos o de propósito general CX = Contador. Se utiliza comúnmente como contador en bucles y operaciones repetitivas de manejo de cadenas. En las instrucciones de desplazamiento y rotación se utiliza como contador de 8 bits. 06/10/2014 Microprocesador 8086 – Digital II 17 Microprocesador 8086 - Arquitectura Registros de datos o de propósito general DX = Datos. Usado en conjunción con AX en las operaciones de multiplicación y división que involucran o generan datos de 32 bits. En las de entrada y salida se emplea para especificar la dirección del puerto E/S. 06/10/2014 Microprocesador 8086 – Digital II 18 Microprocesador 8086 - Arquitectura Registros de segmento CS, DS, SS, ES: Definen áreas de 64 Kb dentro del espacio de direcciones de 1 Mb del 8086. Estas áreas pueden solaparse total o parcialmente. No es posible acceder a una posición de memoria no definida por algún segmento: si es preciso, habrá de moverse alguno. 06/10/2014 Microprocesador 8086 – Digital II 19 Microprocesador 8086 - Arquitectura Registros de segmento CS = Registro de segmento de código (code segment). Contiene la dirección del segmento que apunta a un área de memoria donde se encuentra el código, instrucciones del programa. Los programas de más de 64 Kb requieren cambiar CS periódicamente. 06/10/2014 Microprocesador 8086 – Digital II 20 Microprocesador 8086 - Arquitectura Registros de segmento DS = Registro de segmento de datos (data segment). Contiene la dirección del segmento que apunta a un área de memoria donde se encuentran datos del programa. (Variables, Cttes, etc) 06/10/2014 Microprocesador 8086 – Digital II 21 Microprocesador 8086 - Arquitectura Registros de segmento SS = Registro de segmento de pila (stack segment). Contiene la dirección del segmento que apunta a un área de memoria donde se guardarán datos temporales del programa (Ej. direcciones de retorno de subrutinas, etc) 06/10/2014 Microprocesador 8086 – Digital II 22 Microprocesador 8086 - Arquitectura Registros de segmento ES = Registro de segmento extra (extra segment). Segmento de ampliación para zona de datos. Es extraordinariamente útil actuando en conjunción con DS: con ambos se puede definir dos zonas de 64 Kb, tan alejadas como se desee en el espacio de direcciones, entre las que se pueden intercambiar datos 06/10/2014 Microprocesador 8086 – Digital II 23 Microprocesador 8086 - Arquitectura Registros punteros de pila SP = Puntero de pila (stack pointer). Apunta al inicio de la pila. Utilizado en las instrucciones de manejo de la pila. 06/10/2014 Microprocesador 8086 – Digital II 24 Microprocesador 8086 - Arquitectura Registros punteros de pila BP = Puntero base (base pointer). Es un puntero de base, que apunta a una zona dentro de la pila dedicada al almacenamiento de datos (variables locales y parámetros de las funciones en los programas compilados). 06/10/2014 Microprocesador 8086 – Digital II 25 Microprocesador 8086 - Arquitectura Puntero de instrucciones o contador de programa IP = Puntero de instrucción (instruction pointer). Marca el desplazamiento de la instrucción en curso dentro del segmento de código. Es automáticamente modificado con la lectura de una instrucción. 06/10/2014 Microprocesador 8086 – Digital II 26 Microprocesador 8086 - Arquitectura Registros índices: SI = Índice fuente (source index). Utilizado como registro de índice en ciertos modos de direccionamiento indirecto, también se emplea para guardar un valor de desplazamiento en operaciones de cadenas. 06/10/2014 Microprocesador 8086 – Digital II 27 Microprocesador 8086 - Arquitectura Registros índices: DI = Índice destino (destination index). Se usa en determinados modos de direccionamiento indirecto y para almacenar un desplazamiento en operaciones con cadenas. 06/10/2014 Microprocesador 8086 – Digital II 28 Microprocesador 8086 - Arquitectura Registro de estado o de indicadores (flags) Es un registro de 16 bits de los cuales 9 son utilizados para indicar diversas situaciones durante la ejecución de un programa. • Los bits 0, 2, 4, 6, 7 y 11 son indicadores de condición, que reflejan los resultados de operaciones del programa • los bits del 8 al 10 son indicadores de control y el resto no se utilizan. • Estos indicadores pueden ser comprobados por las instrucciones de salto condicional, lo que permite variar el flujo secuencial del programa según el resultado de las operaciones. • 06/10/2014 Microprocesador 8086 – Digital II 29 Microprocesador 8086 - Arquitectura Bit CF Acarreo ("Carry Flag") Uso Indicador de arrastre del bit de mayor orden, que puede ocurrir en las operaciones aritméticas suma y resta. PF Paridad ("Parity Flag") Si está activo Indica un número par de bits activos (bits cuyo contenido es 1). Esta información es útil cuando el procesador controla transmisiones de datos. AF Acarreo auxiliar Indicador de ajuste en operaciones aritméticas con cantidades BCD ZF Cero ("Zero Flag") Está activo si el resultado de operación es cero o resultado de comparación igual. SF Signo ("Sign Flag") Si está activo indica que el resultado de operación o de comparación son negativos. Detención ("Trap Flag") Si está activo, el procesador genera automáticamente una interrupción después de la ejecución de cada instrucción, lo que permite controlar paso a paso la ejecución del programa. Este bit debe estar normalmente inactivo (a 0). IF Interrupción ("Interrupt Flag") Este bit controla el estado del sistema de interrupciones enmascarables . Cuando está activo (1) permite las interrupciones; el estado inactivo (0) las deshabilita. DF Dirección ("Direction Flag") TF 06/10/2014 Indicador de: OF Desbordamiento Microprocesador 8086(Overflow – DigitalFlag") II Indica la dirección de las operaciones. Señala desbordamiento aritmético 30 Microprocesador 8086 - Arquitectura Bit Indicador de: Indicativo si bit 1 Indicativo si bit 0 CF Acarreo CY ("Carry yes") NC ("No Carry") PF Paridad PE ("Parity Even") paridad par PO ("Parity Odd") paridad impar AF Acarreo auxiliar AC ("Auxiliar Carry") NA ("No Auxiliar") ZF Cero ZR ("Zero") NZ ("No Zero") SF Signo NG ("Negative") negativo PL ("Plus") positivo IF Interrupción EI DI ("Disabled Interrupt") desactivada DF Dirección DN ("Down") decremento UP incremento OF Desbordamiento OV ("Overflow") NV ("No overflow") 06/10/2014 ("Enabled Interrupt") activa Microprocesador 8086 – Digital II 31 Microprocesador 8086 Segmentación de la Memoria en el 8086 06/10/2014 Microprocesador 8086 – Digital II 32 Microprocesador 8086 – Espacio Mapeable FFFFFh Bus de Direcciones Ao 220 = 1MByte Espacio Mapeable Mapa de Memoria A20 00000h 06/10/2014 Microprocesador 8086 – Digital II 33 Microprocesador 8086 - Segmentación Espacio de Memoria Un segmento es un área continua de memoria que puede tener hasta 64Kbytes, que debe comenzar en una localidad de memoria cuya dirección sea límite de 16 bytes (cantidad denominada párrafo) y que puede solaparse con otros segmentos. FFFFFh Fin del Segmento CS:FFFFh Segmento Físico de Código (64 Kbytes) CS:IP CS:0000h Inicio del Segmento Desplazamiento(Offset) 00000h 06/10/2014 Microprocesador 8086 – Digital II 34 Microprocesador 8086 - Segmentación Dirección Física y Dirección Lógica Cada localidad de memoria tiene dos tipos de direcciones : Dirección Física y Dirección Lógica o efectiva Una dirección Física es el valor único de 20 bits que identifica la localización de cada byte en el espacio de memoria de 1 Mbyte. Los programas tratan con dirección Lógicas mas que con la dirección Física. Para cualquier localidad de memoria, el valor base del segmento ubica el primer byte del contenido del segmento y el valor del offset es la distancia, en bytes , de la localización destino del principio del segmento. Los valores de la base del Segmento y del offset son cantidades no signadas de 16 bits; la dirección del byte más bajo del segmento tiene un offset 0. 06/10/2014 Microprocesador 8086 – Digital II 35 Microprocesador 8086 - Segmentación Formación de una Dirección Física Siempre que una memoria es accesada , se genera una dirección física a partir de la dirección lógica. Dirección efectiva, lógica u offset 4 bits Dirección de segmento EL REGISTRO DE SEGMENTO SE DESPLAZA 4 BITS HACIA LA IZQUIERDA (MULTIPLICACIÓN x16) 0000 0000 Dirección física 20 BITS 06/10/2014 Microprocesador 8086 – Digital II 36 Microprocesador 8086 - Segmentación Espacio de Memoria Segmentos Físicos → → → → Empiezan en direcciones físicas divisibles por 16. Tienen un tamaño fijo de 64 Kbytes. Utilizando direcciones lógicas, se puede acceder a todos los registros de un segmento físico sólo cambiando el desplazamiento. CS, DS, SS y ES son los registros del 8086 que contienen las direcciones de inicio de los respectivos segmentos físicos. Segmentos Lógicos → → FFFFF h SS:FFFF h Segmento Lógico de Pila Segmento Físico de Pila (64 Kbytes) SS:0000h CS:FFFF h Segmento Lógico de Código Segmento Físico de Código (64 Kbytes) CS:0000h Es una sección de memoria de tamaño VARIABLE y en general puede contener código, datos o pila. Para poder definir estos códigos son necesarios el uso de las directivas del ensamblador (emu8086) DS:FFFF h Segmento Lógico de Datos Segmento Físico de Datos (64 Kbytes) DS:0000h 00000h 06/10/2014 Microprocesador 8086 – Digital II 37 Microprocesador 8086 - Segmentación El segmento de código (tiene como base el contenido del registro CS). En este segmento se encuentran las instrucciones que forman el programa. Para acceder a los datos contenidos en él, se usa el registro IP como desplazamiento. El segmento de datos (que tiene como base el registro DS). Contiene los datos que utiliza el programa (variables, etc.) Para acceder a los datos contenidos en él, se suele utilizar los registros SI y DI como desplazamiento. 06/10/2014 Microprocesador 8086 – Digital II 38 Microprocesador 8086 - Segmentación SEGMENTOS SOLAPADOS CS CS SEGMENTO DE CÓDIGO PROGRAMA SEGMENTO DE CÓDIGO DS SEGMENTO DE DATOS OTRO SEGMENTO ES SEGMENTO EXTRA DE DATOS SS STACK MEMORIA 06/10/2014 MEMORIA Microprocesador 8086 – Digital II 39 Microprocesador 8086 - Segmentación Relocalización de un programa usando el registro CS 02000 600 PROGRAMA SEGMENTO DE CÓDIGO EN CURSO nuevo (CS)=1A30 1A300 600 PROGRAMA SEGMENTO DE CÓDIGO RELOCALIZADO MEMORIA 06/10/2014 Microprocesador 8086 – Digital II 40 Microprocesador 8086 Instrucción MOV y modos de direccionamiento 06/10/2014 Microprocesador 8086 – Digital II 41 Microprocesador 8086 – Instrucción MOV 06/10/2014 Microprocesador 8086 – Digital II 42 Microprocesador 8086 - Direccionamiento Tipos de Direccionamientos permitidos por el 8086 Por registro Inmediato Directo Indirecto – Por Registro Indirecto – Relativo a la Base Indirecto – Relativo a las base más índice Indirecto – Relativo a la base más índice con desplazamiento 06/10/2014 Microprocesador 8086 – Digital II 43 Microprocesador 8086 - Direccionamiento Direccionamientos por Registro e Inmediato En este tipo de operaciones no intervienen operandos que hagan referencia a una posición de memoria. MOV BX,CX Transfiere el contenido del registro CX al registro BX MOV AX,0x40h Transfiere 0x40h al registro AX En los restantes modos de direccionamiento SIEMPRE uno (y sólo uno) de los dos operandos hace referncia a una posición de memoria. Direccionamiento Directo DATO dw 1000h : : MOV BX,DATO Se transfiere la variable DATO al registro BX. El ensamblador interpreta a la variable DATO como un offset respecto del segmento de datos. Se transfiere un Byte de la posición DS:[1000h] a la parte baja del registro BX MOV BL,[1000h] 06/10/2014 Microprocesador 8086 – Digital II 44 Microprocesador 8086 - Direccionamiento Direccionamiento Indirecto – Por Registro MOV BX,1234h MOV AX,[BX] Transfiere 16 bits de la posición DS:[1234h] al registro AX Direccionamiento Indirecto – Relativo a la Base TBL_datos db 1,2,3 Transfiere el segundo Byte de la tabla “TBL_datos” a la parte baja del registro BX. La BIU calcula la dirección como: Dir = DS:(offset(TBL_datos) + DI) MOV DI,1 MOV BL,TBL_dato[DI] Direccionamiento Indirecto – Relativo a la Base + Indice TBL_datos db 1,2,3 MOV MOV MOV MOV AL,0xFFh BX,OFFSET TBL_datos DI,2 [BX][DI],AL 06/10/2014 Transfiere el valor guardado en AL al tercer Byte de la tabla “TBL_datos”. La BIU calcula la dirección como: BX = offset(TBL_datos) Dir = DS:( BX + DI) Microprocesador 8086 – Digital II 45 Microprocesador 8086 - Direccionamiento Direccionamiento Indirecto – Relativo a la Base + Indice con desplazamiento TBL_datos db 1,2,3 MOV MOV MOV MOV Transfiere el valor guardado en AL al tercer Byte de la tabla “TBL_datos”. La BIU calcula la dirección como: BX = offset(TBL_datos) Dir = DS:( BX + DI +1h) AL,0xFFh BX,OFFSET TBL_datos DI,1 1h[BX][DI],AL Resumen → Los únicos registros que pueden ser utilizados para el direccionamiento son BX, BP, SI y DI. Las combinaciones posibles para su uso se detallan a continuación. Desplazamiento 06/10/2014 Registro Base Registro Índice Combinaciones [BX] [SI] [BX][SI] [BP][SI] [BP] [DI] [BP][DI] [BX][DI] Microprocesador 8086 – Digital II 46 Microprocesador 8086 Espacio de Entrada/Salida 06/10/2014 Microprocesador 8086 – Digital II 47 Microprocesador 8086 – Espacio de I/O Espacio de Entrada/Salida → → → → El microprocesador 8086 posee también un espacio de direcciones válido, adicional al mapa de memoria de 1MBytes, cuyo rango va del 0000h al FFFFh (64 Kbytes). Sólo se utilizan 16 bits para direccionarlo A0 a A15. Un Pin (M/#IO) del 8086 indica si la operación de lectura o escritura fue realizada en el espacio de memoria o en el espacio de entrada/salida. Se utilizan sólo 2 instrucciones de Assembler para interactuar con este espacio (IN y OUT) 06/10/2014 Microprocesador 8086 – Digital II FFFFh 216 = 64KByte Espacio Mapeable Mapa de I/O 0000h 48 Microprocesador 8086 – Espacio de I/O 06/10/2014 Microprocesador 8086 – Digital II 49 Microprocesador 8086 – Espacio de I/O 06/10/2014 Microprocesador 8086 – Digital II 50 Microprocesador 8086 Pinout – Descripción Pin a Pin del 8086 06/10/2014 Microprocesador 8086 – Digital II 51 Microprocesador 8086 - PinOut Pines de Alimentación: ➢ VCC (5V) y GND Señal de Clock: ➢ El clock del 8086 dependiendo de su modelo podrá ser de 5MHz, 8MHz o 10MHz ➢ La señal deberá ser suministrada por un generador de clock externo (8284A) Bus de Direcciones: ➢ 20 líneas / pines (AD0 a AD15 y A16 a A19) ➢ Permiten direccionar 1MByte (220) Bus de Datos: ➢ 16 líneas / pines (AD0 a AD15) ➢ AD0 a AD15 son pines compartidos entre el Bus de Direcciones y el Bus de Datos. ➢ Para su utilización se requiere la multiplexación Temporal de los pines (Multiplexación del bus). 06/10/2014 Microprocesador 8086 – Digital II 52 Microprocesador 8086 - PinOut Pin de RESET: ➢ Manteniendo durante cuatro ciclos de clock este pin en un nivel ALTO producirá que el microprocesador se reinicie. ➢ Cuando el microprocesador se reinicia comienza a ejecutar instrucciones en la dirección FFFF0h del espacio de memoria. ➢ Se deshabilitan las interrupciones. Pin MN/#MX (Selección de Modo Máximo o Mínimo): ➢ Un nivel ALTO en este pin seleccionará el modo Mínimo. ➢ Un nivel BAJO en este pin seleccionará el modo Máximo. ➢ Dependiendo del modo seleccionado, se dará función específica a los pines 24 al 31. Pin #BHE (Byte High Enable): ➢ Habilita la escritura de la parte alta del bus de datos del 8086 bit 8 a bit 15. Pin READY: ➢ Se emplea para introducir estados de espera (Wait-State) en los ciclos de bus del microprocesador. ➢ Este pin en un nivel BAJO introducirá ciclos de espera. ➢ Este pin en un nivel ALTO no tiene efectos en el funcionamiento del microprocesador. 06/10/2014 Microprocesador 8086 – Digital II 53 Microprocesador 8086 - PinOut Modo Mínimo Modo Máximo Pin de RESET: ➢ Manteniendo durante cuatro ciclos de clock este pin en un nivel ALTO producirá que el microprocesador se reinicie. Single Processor mode Multiprocessor mode ➢ Cuando el microprocesador se reinicia comienza a ejecutar instrucciones El 8086 es responsable Un Controlador de Bus externo al en la dirección FFFF0h del espacio de memoria. de generar ➢ Se deshabilitan las interrupciones. todas las señales de control para 8086 será responsable de generar accesos a memoria y I/O. todas las señales de control para Pin MN/#MX (Selección los de Modo Máximo o Mínimo): los accesos a memoria y I/O. ➢ Un nivel ALTO en este pin seleccionará el modo Mínimo. ➢ Un nivel BAJO en este pin seleccionará el modo Máximo. Aplicaciones simples Aplicaciones complejas ➢ Dependiendo del modo seleccionado, se dará función específica a los pines 24 al 31. Pin #BHE (Byte High Enable): No es posible la conexión de un Procesadores adicionales pueden ➢ Habilita la escritura de la parte alta del bus de datos del 8086 bit 8 a bit procesador adicional ser conectados Ej. 8087 ( Co15. Procesador matemático) Pin READY: Pin # 33 es conectado a +5V Pin # 33 conectado a GND ➢ Se emplea para introducir estados de espera (Wait-State) en los ciclos de bus del microprocesador. ➢ Este pin en un nivel BAJO introducirá ciclos de espera. ➢ Este pin en un nivel ALTO no tiene efectos en el funcionamiento del microprocesador. 06/10/2014 Microprocesador 8086 – Digital II 54 Microprocesador 8086 - PinOut (Modo MN) Pin de #RD: ➢ Este pin de salida cuando está en un nivel BAJO indica que el microprocesador puede recibir datos del espacio de memoria o de Entrada/Salida. Pin de #WR: ➢ Este pin de salida cuando está en un nivel BAJO indica que el microprocesador está sacando datos para ser escritos en un dispositivo del espacio de memoria o de Entrada/Salida. Pin M/#IO: ➢ Este pin de salida indica si la operación de lectura/escritura se realizará con los dispositivos del mapa de memoria (nivel ALTO) o con los dispositivos del mapa de Entrada/Salida (nivel BAJO). Pin DT/#R: ➢ Este Pin de salida indica si el microprocesador se encuentra transmitiendo datos (DT/#R = 1) o recibiendo datos (DT/#R = 0). Esta señal es útil para habilitar los circuitos de acoplamiento del canal de datos. Pin #DEN: ➢ Este Pin de salida con un nivel en BAJO indica que el bus de datos se encuentra habilitado. Esta señal es útil para habilitar los circuitos de acoplamiento del canal de datos. 06/10/2014 Microprocesador 8086 – Digital II 55 Microprocesador 8086 - PinOut (Modo MN) Pin ALE (Address Latch Enable): ➢ Este pin de salida indica que los pines AD0 a AD15 y A16 a A19 contienen una dirección válida (Memoria o Entrada/Salida). ➢ Este pin se utiliza para grabar dicha dirección en un registro externo al microprocesador antes de que el microprocesador la retire. Pin HOLD: ➢ Este pin de entrada indica al microprocesador que se solicita un acceso directo a memoria. Un nivel en ALTO en este pin provocará que el microprocesador deje de ejecutar instrucciones y lleve su bus AD y de control a un estado de alta impedancia. Con un nivel BAJO en este pin el microprocesador ejecuta normalmente su programas. Pin HLDA: ➢ Este Pin de salida indica si el microprocesador reconoció el pedido de HOLD y que se han concedidos los canales. Pin #TEST: ➢ Este pin de entrada funciona en conjunto con la instrucción de assembler WAIT. Si #TEST = 1 entonces la instrucción WAIT esperará hasta que #TEST = 0 para continuar con el flujo de programa. ➢ Es útil para sincronizar con algún elemento externo al cual el microprocesador debe esperar que termine de realizar alguna tarea específica 06/10/2014 Microprocesador 8086 – Digital II 56 Microprocesador 8086 - PinOut (Modo MN) Pin INTR (Solicitud de Interrupción): ➢ Este pin de entrada se utiliza para solicitar una interrupción por hardware al microprocesador. ➢ La solicitudes de interrupciones que ingresen por este pin podrán ser enmascaradas (estado del bit del registro de banderas IF – Interrupt Flag). Pin #INTA (Reconocimiento del pedido de interrupción): ➢ Este Pin de salida indica con un nivel BAJO que el microprocesador reconoció el pedido de INTR. El dispositivo externo que solicitó la interrupción deberá colocar en el bus de datos el número del vector de interrupciones para que el microprocesador identifique la rutina de servicio de interrupciones que deberá ejecutar. Pin NMI (Interrupción No Enmascarable): ➢ Este pin es similar al INTR excepto que que no verifica cual es el estado del flag IF, por lo que cualquier pedido de interrupción que ingrese por este pin no podrá ser enmascarado. ➢ Esta entrada utiliza el vector de interrupción 2. 06/10/2014 Microprocesador 8086 – Digital II 57 Microprocesador 8086 - PinOut (Modo MN) Pines de Estado (Status Bus – S3 a S7): ➢ S3 y S4 se utilizan para identificar que registro de segmento se está utilizando en ese ciclo de bus. S5 indica el estado del flag IF (Interrupt Flag). ➢ S6 siempre es un CERO lógico. ➢ S7 siempre es un UNO lógico. ➢ 06/10/2014 Microprocesador 8086 – Digital II 58 Microprocesador 8086 Generador de Clock - 8284A 06/10/2014 Microprocesador 8086 – Digital II 59 Generador de Clock - 8284A El microprocesador 8086 no tiene integrado un generador de clock, por lo que será necesario el uso de uno externo. ➢ El fabricante (INTEL) recomienda en el manual del microprocesador el uso del 8284A. ➢ Las principales funciones que brinda este generador de clock son las siguientes: ➢ ✔ ✔ ✔ ✔ Generar la señal de clock al microprocesador (5MHz, 8MHz o 10MHz). Genera una señal de clock auxiliar para los periféricos del sistema. Maneja la señal de RESET del microprocesador. Maneja la señal de READY del microprocesador con la finalidad de insertar tiempos de espera (T-WAIT) en los ciclos de bus del 8086. 06/10/2014 Microprocesador 8086 – Digital II 60 Generador de Clock - 8284A Pines X1 y X2: ➢ Pines de conexión para el oscilador a cristal de la frecuencia correcta. Pin EFI: ➢ Entrada externa de clock. Esta entrada puede utilizarse como fuente de clock del 8284A en lugar del oscilador a cristal. Pin F/#C: ➢ Este pin de entrada puesto a un nivel BAJO se selecciona el oscilador a cristal como fuente de reloj para el 8284A. Con un nivel en ALTO se selecciona la entrada externa de clock EFI. Pin CLK: ➢ Este pin de salida es el que proporciona la señal de clock para el microprocesador 8086. La frecuencia de esta señal es de 1/3 de la frecuencia del oscilador a cristal o de la señal EFI. Pin PCLK: ➢ Este pin de salida es el que proporciona la señal de clock para los periféricos del sistema. La frecuencia de esta señal es de 1/6 de la frecuencia del oscilador a cristal o de la señal EFI. Pin OSC: ➢ Este pin de salida presenta una señal acondicionada (niveles TTL) de la misma frecuencia que el oscilador a cristal o de la señal EFI. 06/10/2014 Microprocesador 8086 – Digital II 61 Generador de Clock - 8284A Pines #AEN1 y #AEN2 (Address Enable): ➢ Estos pines (habilitación de direcciones) funcionan en conjunto con los pines RDY1 y RDY2 para generar la señal de READY del microprocesador. Pines RDY1 y RDY2: ➢ Estos pines indican que los canales están listos. Funcionan en conjunto con los pines #AEN1 y #AEN2. ➢ Este dispositivo permite tener dos grupos de periféricos que requieran insertar una cantidad distinta de T-WAITS. Pin READY: ➢ Este pin de salida que se conecta con el pin de READY del microprocesador. ➢ Cuando #AEN tiene un valor bajo y RDY un valor alto, se activará en forma sincrónica la señal READY. Pin #RES: ➢ Entrada de reset del 8284A. Se conecta una red RC que proporciona la temporización y acondicionamiento de la señal para el reset. Pin RESET: ➢ Este pin de salida proporciona la señal de RESET para el microprocesador. Esta señal es #RES sincronizada con el CLK. 06/10/2014 Microprocesador 8086 – Digital II 62 Generador de Clock - 8284A Pin CSYNC: ➢ Entrada de sincronización de la señal de clock EFI. Si se utiliza el oscilador a cristal este pin debe estar a GND. ➢ Esta entrada se utiliza en sistemas multiprocesadores. Pin #ASYNC: ➢ Es una entrada que permite seleccionar una o dos etapas de sincronización para la señal de READY. Pines VCC y GND: ➢ Pines de alimentación del 8284A. 06/10/2014 Microprocesador 8086 – Digital II 63 Generador de Clock - 8284A Aplicación típica del 8284A para la generación de las señales de Clock y Reset del microprocesador PCLK PCLK OSC 06/10/2014 2.5MHz 15MHz Microprocesador 8086 – Digital II 64 Microprocesador 8086 Multiplexado del Bus Esquemas típicos de Conexión 06/10/2014 Microprocesador 8086 – Digital II 65 Multiplexado del Bus y Buffering Demultiplexado del Bus Los buses de Dirrecciones/Datos (AD0 a AD15) y Direcciones/Estados (A16/S3, A17/S4, A18/S5, A19/S6) son multiplexados temporalmente por el microprocesador para minimizar la cantidad de pines del encapsulado. ➢ ➢ ¿Qué implica la Multiplexación temporal de los buses? ✔ ➢ Implica que en un momento/tiempo del ciclo de bus del microprocesador los pines del mismo (AD0 a AD15, A16/S3, A17/S4, A18/S5, A19/S6) se comportarán como bus de direcciones y en otro momento/tiempo del ciclo de bus se comportarán como bus de datos y de estados (los mismos pines!). ¿Es necesario demultiplexar los Buses?¿Por qué? ✔ ✔ Cualquier dispositivo que se encuentre conectado al microprocesador (ej. una memoria), requiere que la dirección siga siendo válida en sus pines de entrada mientras se lleva a cabo una operación de lectura o escritura del mismo Debemos salvar (grabar) la dirección válida que presenta el microprocesador en sus pines cuando este se comporta como bus de direcciones en un dispositivo externo (Latch/Registro). 06/10/2014 Microprocesador 8086 – Digital II 66 74LS373 – Registros 3 estados (3-States Octal D-types Transparent Latches) ALE (Address Latch Enable) Este pin de salida indica que los pines AD0 a AD15 y A16 a A19 contienen una dirección válida (Memoria o Entrada/Salida). Bus de Control ● M/IO: Memoria o Entrada/Salida ● #RD: Lectura (READ) ● #WR; Ecritura (WRITE) Sistema Totalmente Buffereado 74LS374 – Registros 3 estados (3-States Octal D-types Transparent Latches) 74LS245 – Transceiver (bidireccional) con salida de tres estados. Este tipo de configuración es requerido cuando las memorias o periféricos son lentos. DIR Direction 1: 0: è 06/10/2014 Gracias! Microprocesador 8086 – Digital II 69