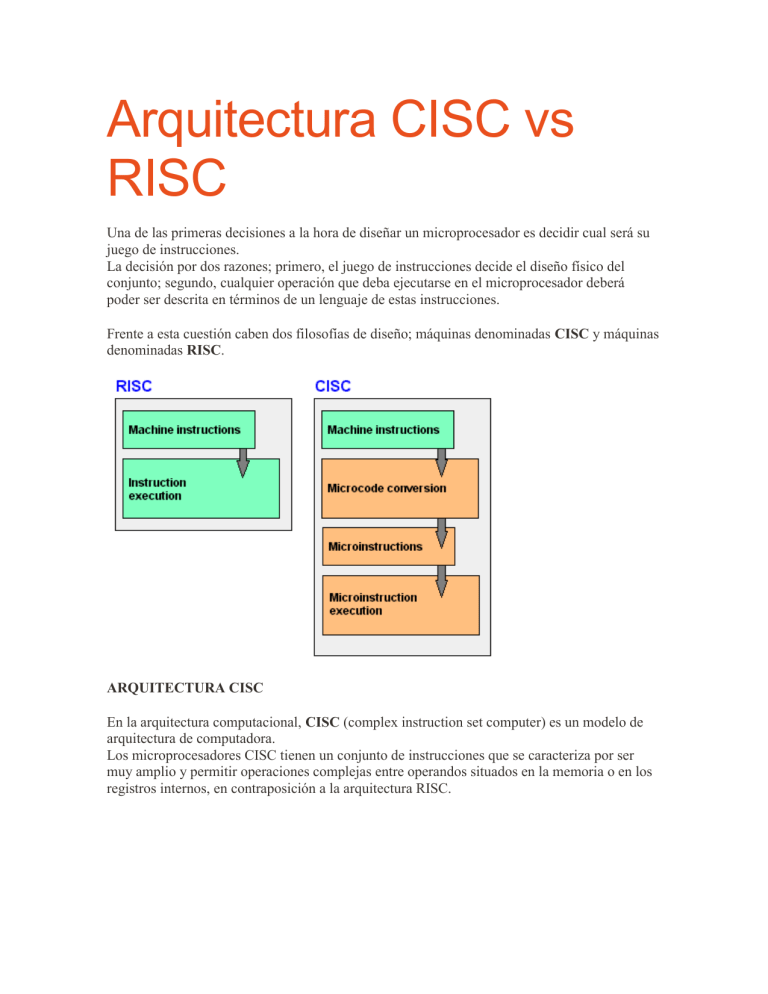

Arquitectura CISC vs RISC Una de las primeras decisiones a la hora de diseñar un microprocesador es decidir cual será su juego de instrucciones. La decisión por dos razones; primero, el juego de instrucciones decide el diseño físico del conjunto; segundo, cualquier operación que deba ejecutarse en el microprocesador deberá poder ser descrita en términos de un lenguaje de estas instrucciones. Frente a esta cuestión caben dos filosofías de diseño; máquinas denominadas CISC y máquinas denominadas RISC. ARQUITECTURA CISC En la arquitectura computacional, CISC (complex instruction set computer) es un modelo de arquitectura de computadora. Los microprocesadores CISC tienen un conjunto de instrucciones que se caracteriza por ser muy amplio y permitir operaciones complejas entre operandos situados en la memoria o en los registros internos, en contraposición a la arquitectura RISC. Este tipo de arquitectura dificulta el paralelismo entre instrucciones, por lo que, en la actualidad, la mayoría de los sistemas CISC de alto rendimiento implementan un sistema que convierte dichas instrucciones complejas en varias instrucciones simples del tipo RISC, llamadas generalmente microinstrucciones. Los CISC pertenecen a la primera corriente de construcción de procesadores, antes del desarrollo de los RISC. Ejemplos de ellos son: Motorola 68000, Zilog Z80 y toda la familia Intel x86 usada en la mayoría de las computadoras personales actuales. Para realizar una sola instrucción un chip CISC requiere de cuatro a diez ciclos de reloj. Entre las ventajas de CISC destacan las siguientes: Reduce la dificultad de crear compiladores. Permite reducir el costo total del sistema. Reduce los costos de creación de sftware. Mejora la compactación de código. Facilita la depuración de errores. Ejemplo de microprocesadores basados en la tecnología CISC: Intel 8086, 8088, 80286, 80386, 80486. Motorola 68000, 68010, 68020, 68030, 6840. ARQUITECTURA RISC: En la arquitectura computacional, RISC (del inglés reduced instruction set computer) es un tipo de microprocesador con las siguientes características fundamentales: Instrucciones de tamaño fijo y presentadas en un reducido número de formatos. Sólo las instrucciones de carga y almacenamiento acceden a la memoria de datos. El objetivo de diseñar máquinas con esta arquitectura es posibilitar la segmentación y el paralelismo en la ejecución de instrucciones y reducir los accesos a memoria. Las máquinas RISC protagonizan la tendencia actual de construcción de microprocesadores. PowerPC, DEC Alpha, MIPS, ARM, SPARC… son ejemplos de algunos de ellos. RISC es una filosofía de diseño de CPU para computadora que está a favor de conjuntos de instrucciones pequeñas y simples que toman menor tiempo para ejecutarse. El tipo de procesador más comúnmente utilizado en equipos de escritorio, el x86, está basado en CISC en lugar de RISC, aunque las versiones más nuevas traducen instrucciones basadas en CISC x86 a instrucciones más simples basadas en RISC para uso interno antes de su ejecución. Entre las ventajas de RISC tenemos las siguientes: La CPU trabaja mas rápido al utilizar menos ciclos de reloj para ejecutar instrucciones. Utiliza un sistema de direcciones no destructivas en RAM. Eso significa que a diferencia de CISC, RISC conserva después de realizar sus operaciones en memoria los dos operandos y su resultado, reduciendo la ejecución de nuevas operaciones. Cada instrucción puede ser ejecutada en un solo ciclo del CPU. Ejemplo de microprocesadores basados en la tecnología RISC: MIPS, Millions Instruction Per Second. PA-RISC, Hewlett Packard. SPARC, Scalable Processor Architecture, Sun Microsystems. POWER PC, Apple, Motorola e IBM. En Conclusión: Hoy en día, los programas cada vez más grandes y complejos demandan mayor velocidad en el procesamiento de información, lo que implica la búsqueda de microprocesadores más rápidos y eficientes. INTRODUCCIÓN A LOS MULTIPROCESADORES CISC ,RISC Los procesadores se agrupan hoy en dos familias, la más antigua y común de las cuales es la "CISC" o "Complex InstructionSet Computer": computador de set complejo de instrucciones. Esto corresponde a procesadores que son capaces de ejecutar un gran número de instrucciones pre-definidas en lenguaje de máquina (del orden del centenar). Desde hace unos años se fabrican y utilizan en algunas máquinas procesadores "RISC" o "Reduced Instruction Set Computer",es decir con un número reducido de instrucciones. Esto permite una ejecución más rápida de las instrucciones pero requiere compiladores (o sea traductores automáticos de programas) más complejos ya que las instrucciones que un "CISC" podría admitir pero no un "RISC", deben ser escritas como combinaciones de varias instrucciones admisibles del "RISC". Se obtiene una ganancia en velocidad por el hecho que el RISC domina instrucciones muy frecuentes mientras son operaciones menos frecuentes las que deben descomponerse. Dentro de muy poco los usuarios dejaran de hacerse la pregunta ¿ RISC O CISC ?, puesto que la tendencia futura, nos lleva a pensar que ya no existirán los CISC puros. Hace ya tiempo que se ha empezado a investigar sobre microprocesadores "híbridos", es decir, han llevado a cabo el que las nuevas CPU's no sean en su cien por cien CISC, sino por el contrario, que estas ya contengan algunos aspectos de tecnología RISC. Este propósito se ha realizado con el fin de obtener ventajas procedentes de ambas tecnologías (mantener la compatibilidad x86 de los CISC, y a la vez aumentar las prestaciones hasta aproximarse a un RISC), sin embargo, este objetivo todavía no se ha conseguido, de momento se han introducido algunos puntos del RISC, lo cual no significa que hayan alcanzado un nivel optimo. Realmente, las diferencias son cada vez mas borrosas entre las arquitecturas CISC y RISC. Las CPU's combinan elementos de ambas y no son fáciles de encasillar. Por ejemplo, el Pentium Pro traduce las largas instrucciones CISC de la arquitectura x86 a microoperaciones sencillas de longitud fija que se ejecutan en un núcleo de estilo RISC. El UltraSparc-II de Sun, acelera la decodificacion MPEG con unas instrucciones especiales para gráficos; estas instrucciones obtienen unos resultados que en otros procesadores requerirían 48 instrucciones. Por lo tanto a corto plazo, en el mercado coexistirán las CPU's RISC y los microprocesadores híbridos RISC - CISC, pero cada vez con diferencias mas difusas entre ambas tecnologías. De hecho, los futuros procesadores lucharan en cuatro frentes : -Ejecutar mas instrucciones por ciclo. -Ejecutar las instrucciones en orden distinto del original para que las interdependencias entre operaciones sucesivas no afecten al rendimiento del procesador. -Renombrar los registros para paliar la escasez de los mismos. -Contribuir a acelerar el rendimiento global del sistema, ademas de la velocidad de la CPU. CISC. La tecnología CISC (Complex Instruction Set Computer) nació en los años 70 de la mano de Intel, creador en 1971 del primer microchip que permitiría el nacimiento de la informática personal. Más concretamente, sería en 1972 cuando aparecería el 8080, primer chip capaz de procesar 8 bits, suficiente para representar números y letras. Con la posibilidad de colocar todos los circuitos en un solo chip y la capacidad de manejar número y letras nacería la cuarta generación de ordenadores, la de los conocidos como PC u ordenadores personales. El diseño de esta arquitectura estuvo orientado por las condiciones de mercado de aquella época y muy especialmente por la limitación en oferta y precio de la memoria de acceso aleatorio del ordenador, la RAM. Así pues, muchas de las decisiones tomadas con relación al diseño del chip tenían como objetivo minimizar los requerimientos de memoria que se hicieran al ordenador. Una forma de reducir la necesidad de memoria era simplificando el software e incrementando la complejidad del procesador, lo cual si bien iba en detrimento del rendimiento global del sistema era una solución mucho mejor que tener que añadir más RAM. Características de CISC. El juego de instrucciones son de longitud variable, logrando reducir la longitud de los programas. Soporta el acceso desalineado a memoria permitiendo utilizar al máximo su espacio. Posee instrucciones muy completas que permiten facilitar la programación en ensamblador. Posee potentes instrucciones que permiten accesos como los indirectos a memoria de una sola vez. Posee instrucciones de tratamiento de palabras( ‘strings’). Ayuda en la ejecución de lenguajes de alto nivel, al mejorar las instrucciones del ensamblador. Ayuda en la gestión de la memoria. Ayuda a la realización de sistemas operativos. Incorpora técnicas para aumentar la velocidad de ejecución. Ayuda a la depuración de programas. Considerando la extraordinaria cantidad de instrucciones que la CPU puede manejar, la construcción de una CPU con arquitectura CISC es realmente compleja. ¿Cómo funciona un procesador de instrucciones complejas? Los chips CISC incorporan un gran conjunto de comandos en su ROM (memoria sólo de lectura) que contienen a su vez varios subcomandos que deben realizarse para completar una operación sencilla (sumar, multiplicar, mover un texto, cambiar un icono de sitio...). Cuando el sistema operativo o una aplicación requiere de una de estas acciones, envía al procesador el nombre del comando para realizarla junto con el resto de información complementaria que se necesite. Pero cada uno de estos comandos de la ROM del CISC varían de tamaño y, por lo tanto, el chip debe en primer lugar verificar cuanto espacio requiere el comando para ejecutarse y poder así reservárselo en la memoria interna. Además, el procesador debe determinar la forma correcta de cargar y almacenar el comando, procesos ambos que ralentizan el rendimiento del sistema. El procesador envía entonces el comando solicitado a una unidad que lo descodifica en instrucciones más pequeñas que podrán ser ejecutadas por un nanoprocesador, una especie de procesador dentro del procesador. Y al no ser las instrucciones independientes, pues son instrucciones menores procedentes de la descodificación de una instrucción mayor, sólo puede realizarse una instrucción cada vez. A través de la compleja circuitería del chip, el nanoprocesador ejecuta cada una de las instrucciones del comando. El desplazamiento por esta circuitería también ralentiza el proceso. Para realizar una sola instrucción un chip CISC requiere de cuatro a diez ciclos de reloj. RISC RISC (del inglés Reduced Instruction Set Computer, en español Computador con Conjunto Reducido de Instrucciones) es un tipo de diseño de CPU generalmente utilizado en microprocesadores o microcontroladores con las siguientes características fundamentales : Instrucciones de tamaño fijo y presentadas en un reducido número de formatos. 2. Sólo las instrucciones de carga y almacenamiento acceden a la memoria de datos. 1. Características de RISC. Las características comunes a todos los procesadores RISC, fuente de sus capacidades de altas prestaciones, son: Modelo de conjunto de instrucciones Load/Store (Cargar/Almacenar). Sólo las instrucciones Load/Store acceden a memoria; las demás operaciones en un RISC, tienen lugar en su gran conjunto de registros. Ello simplifica el direccionamiento y acorta los tiempos de los ciclos de la CPU, y además facilita la gestión de los fallos de paginas (page faults) en entornos de memoria virtual. Además, permite un elevado nivel de concurrencia a consecuencia de la independencia de las operaciones de Load/Store de la ejecución del resto de las instrucciones. 2. Arquitectura no destructiva de tres direcciones. Los procesadores CISC destruyen la información que existe en alguno de los registros, como consecuencia de la ejecución normal de instrucciones; esto es debido a su arquitectura de dos direcciones, por la cual el resultado de una operación sobrescribe uno de los registros que contenía a los operandos. Por contra, las instrucciones RISC, con tres direcciones, contienen los campos de los dos operandos y de su resultado. Por lo tanto, tanto los operandos origen como el destino, son mantenidos en los registros tras haber sido completada la operación. Esta arquitectura "no destructiva" permite a los compiladores organizar las instrucciones de modo que mantengan llenos los conductos (pipelines) del chip, y por tanto reutilizar los operandos optimizando la concurrencia. 1. Instrucciones simples, de formato fijo, con pocos modos de direccionamiento. Las instrucciones simples reducen de manera muy significativa el esfuerzo para su des-codificación, y favorecen su ejecución en pipelines. Las instrucciones de longitud fija, con formatos fijos, implican que los campos de códigos de operación (opcodes) y de los operandos están siempre codificados en las mismas posiciones, permitiendo el acceso a los registros al mismo tiempo que se está descodificando el código de operación. Todas las instrucciones tienen una longitud equivalente a una palabra y están alineadas en la memoria en límites de palabra (word boundaries), ya que no pueden ser repartidas en pedazos que puedan estar en diferentes páginas. 4. Ausencia de micro-código. El micro-código no se presta a la ejecución en ciclos únicos, ya que requiere que el hardware sea dedicado a su interpretación dinámica. La programación en microcódigo no hace que el software sea más rápido que el programado con un conjunto de instrucciones simples. Todas las funciones y el control, en los procesadores RISC, están "cableados" (hardwired), para lograr una máxima velocidad y eficiencia. 5. Ejecución en conductos (pipelined). Las instrucciones simples, de formato fijo y ciclo único permiten que las diferentes etapas de los ciclos de ejecución (búsqueda o fetch, des-codificación, ejecución, y escritura del resultado o result write-back) para instrucciones múltiples, se puedan realizar simultáneamente, de un modo más simple y eficaz. 6. Ejecución en ciclos únicos (single-cycle). El resultado directo de los conjuntos de instrucciones que ofrecen los procesadores RISC, es que cada instrucción puede ser ejecutada en un único ciclo de la CPU. Esto invalida la creencia de que las micro-instrucciones en micro-código, creadas para ser ejecutadas en un solo ciclo de procesador, son más rápidas que las instrucciones del lenguaje ensamblador. Ya que el caché esta construido partiendo de la misma tecnología que el almacenamiento de control del micro-programa, una única instrucción puede ser ejecutada a la misma velocidad que una micro-instrucción. La ejecución en ciclos únicos también simplifica la gestión de las interrupciones y los conductos (pipelines). 3.