Descarga3 - GEOCITIES.ws

Anuncio

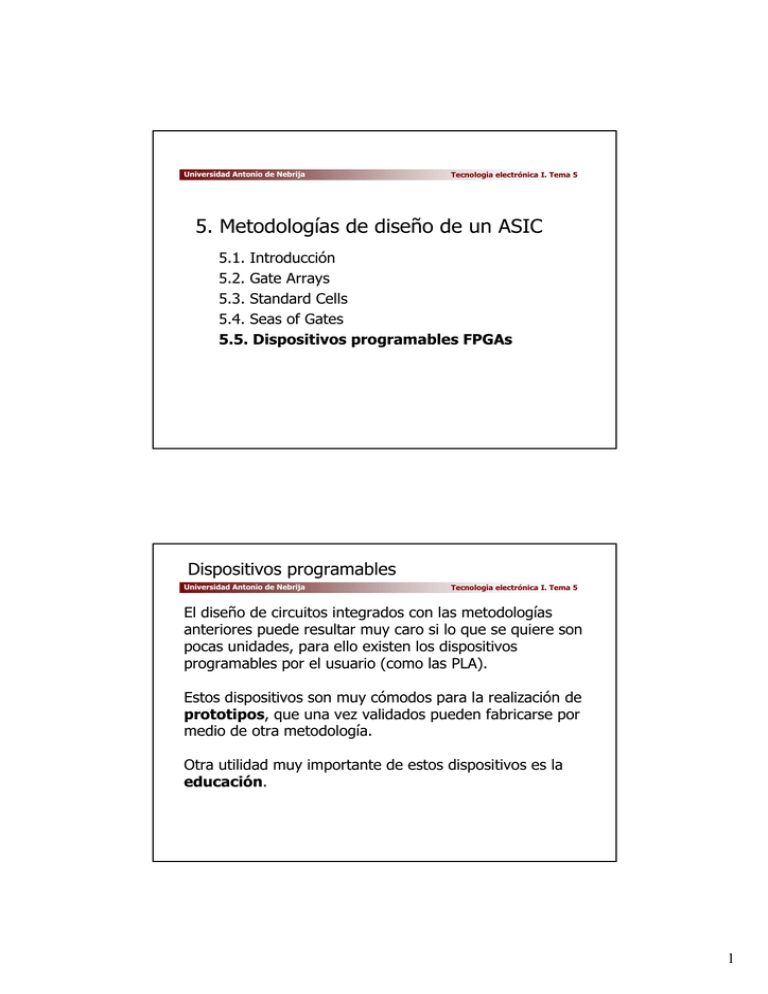

Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 5. Metodologías de diseño de un ASIC 5.1. Introducción 5.2. Gate Arrays 5.3. Standard Cells 5.4. Seas of Gates 5.5. Dispositivos programables FPGAs Dispositivos programables Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 El diseño de circuitos integrados con las metodologías anteriores puede resultar muy caro si lo que se quiere son pocas unidades, para ello existen los dispositivos programables por el usuario (como las PLA). Estos dispositivos son muy cómodos para la realización de prototipos, que una vez validados pueden fabricarse por medio de otra metodología. Otra utilidad muy importante de estos dispositivos es la educación. 1 Dispositivos programables Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Existen muchos dispositivos programables y muchos métodos de programación, pero la arquitectura común de todos ellos es la siguiente: • Módulos programables • Conexiones programables Modulo 1 (programable) Modulo 2 (programable) Modulo n (programable) Conexiones programables Field Programmable Gate Arrays Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Es uno de los dispositivos más utilizados, su estructura es la siguiente: E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S E/S Cada uno de los cruces de líneas es programable 2 Field Programmable Gate Arrays Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Características: • Cada módulo es programable, sea módulo de E/S o módulo interno. • Contiene un número elevado de módulos internos, que son módulos simples, capaces de realizar primitivas lógicas simples o biestables. • Los cruces de líneas son programables: podemos programar su conexión Otros dispositivos programables: PLD Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 PLD: Programmable logic device. Su estructura es la siguiente: Entradas de control (CLK, RESET, ...) E/S E/S E/S FSM FSM FSM FSM Conexiones programables E/S FSM E/S FSM E/S 3 Otros dispositivos programables: PLD Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Características: • Cada módulo es programable, sea módulo de E/S o módulo interno. • Contiene un número pequeño de módulos internos, que son módulos complejos: FSM (Finite State Machine), cada uno de ellos podría ser una máquina de estados. • Existe una zona donde se programan las conexiones. Comparación FPGA vs PLD Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 FPGA PLD Módulos programables Nº elevado de módulos simples Nº reducido de módulos complejos Conexiones programables Distribuidas Centralizadas Aplicación Diseño lógico basado en puertas y biestables Síntesis de máquinas de estados 4 Elección de la metodología Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Nº de puertas 1.000.000 ASIC ASIC 100.000 GA GA SG SG SC SC FPGA FPGA 10.000 1.000 100 10 PAL PAL Comp. discretos 10 100 1.000 10.000 Nº de unidades Programación Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Módulos programables simples: • Número reducido de E/S • Permiten hacer un conjunto de funciones con esas variables, pero no todas las posibles • Pueden incluir biestables • La programación se hace por medio de variables de control X1 X2 f X4 Y1 Y2 Y8 Dependiendo de los valores de las Y el resultado de la función será distinto 5 Programación Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Módulos programables simples, ejemplo X1 X2 X3 CALCULO DE TODAS LAS POSIBLES SALIDAS SELECCIÓN DE LA SALIDA f X4 Y1 Y2 Programación Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Módulos programables simples. Estructura X MODULO f Y MEMORIA (PROGRAMABLE) 6 Programación Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Máquinas de estado programables E CIRCUITO COMBINACIONAL PROGRAMABLE S REGISTRO CLK El circuito combinacional suele ser una red PLA Tecnologías de programación Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Formas de establecer conexiones y puntos de memoria: • Conexiones con fusibles o antifusibles (PLA), no reprogramables (PROM). • Conexiones y puntos de memoria no volátiles. Con transistores MOS de puerta flotante. Reprogramables (FPGA, EPROM, E2PROM) • Conexiones y puntos de memoria volátiles (RAM). El circuito se puede reprogramar en tiempo “de ejecución” 7 Tecnologías de programación Universidad Antonio de Nebrija FUSIBLE Tecnología electrónica I. Tema 5 ANTIFUSIBLE Conexión y punto de memoria con MOS de puerta flotante Transistor nMOS de puerta flotante Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 8 Transistor nMOS de puerta flotante Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Funcionamiento: Si se aplica una tensión alta en la puerta (Vpp) y una tensión un poco menor en el drenador, existirá un flujo de electrones desde la fuente al drenador. Los electrones adquieren una energía cinética y su trayectoria se ve alterada por el campo eléctrico en la zona del canal, por la elevada tensión en la puerta (12-13 V). Los electrones que consiguen una energía superior a 3.2eV son capaces de atravesar el aislante y se quedan atrapados en la puerta flotante. El resultado es un transistor con una elevada tensión umbral. Transistor nMOS de puerta flotante Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 9 Transistor nMOS de puerta flotante Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 El transistor de puerta flotante se utiliza en EPROM y EEPROM. Dentro de estas últimas se encuentra la memoria Flash, ampliamente utilizada en la actualidad (CompactFlash, SmartMedia, Memory Stick, PCMCIA...) Tecnologías de programación Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 Conexión y punto de memoria volátil DATA WRITE CONNECT S D Q EN Q /Q 10 Anexo: tipos de memorias RAM Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 SRAM: Static Random Access memory, utiliza varios transistores (tipicamente seis) apra cada celda de memoria, pero no tiene un condensador en cada celda. Se utiliza para la cache, porque es más rápida. DRAM: Dynamic Random Access Memory, tiene celdas de memoria con un transistor y un condensador acoplados necesitando continuo refresco. FPM DRAM Fast Page Mode DRAM. Espera a finalizar el proceso de localización del dato y lectura para empezar con el siguiente dato. Tasa de transferencia máxima 176 Mbps. EDO DRAM: Extended data-out DRAM. No espera hasta el final, una vez se lacaliza la dirección de un bit, se pasa al siguiente. Tasa de transferencia máxima 264 Mbps. Anexo: tipos de memorias RAM Universidad Antonio de Nebrija Tecnología electrónica I. Tema 5 SDRAM: Syncronous DRAM: Espera en la fila leyendo bits consecutivos, moviendose rápidamente por las columnas. Normalmente cuando se accede a la memoria, los datos que se piden suelen estar en secuencia. Tasa de transferencia máxima 528 Mbps. DDR SDRAM: Double Data Rate SDRAM: Tiene un mayor ancho de banda que la SDRAM, por lo que va al doble de velocidad. Tasa de transferencia máxima 1064 Mbps. CMOS RAM: Es un término que especifica la pequeña cantidad de memoria usada por los dispositivos para recordar ciertas cosas, como los parámetros de configuración de un disco duro. Es necesario que haya una pila para mantener esa memoria. 11