10. Evaluaci´on de las prestaciones del subsistema de memoria. 11

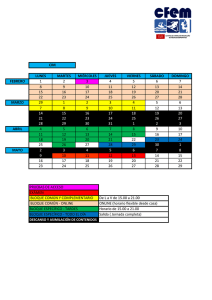

Anuncio

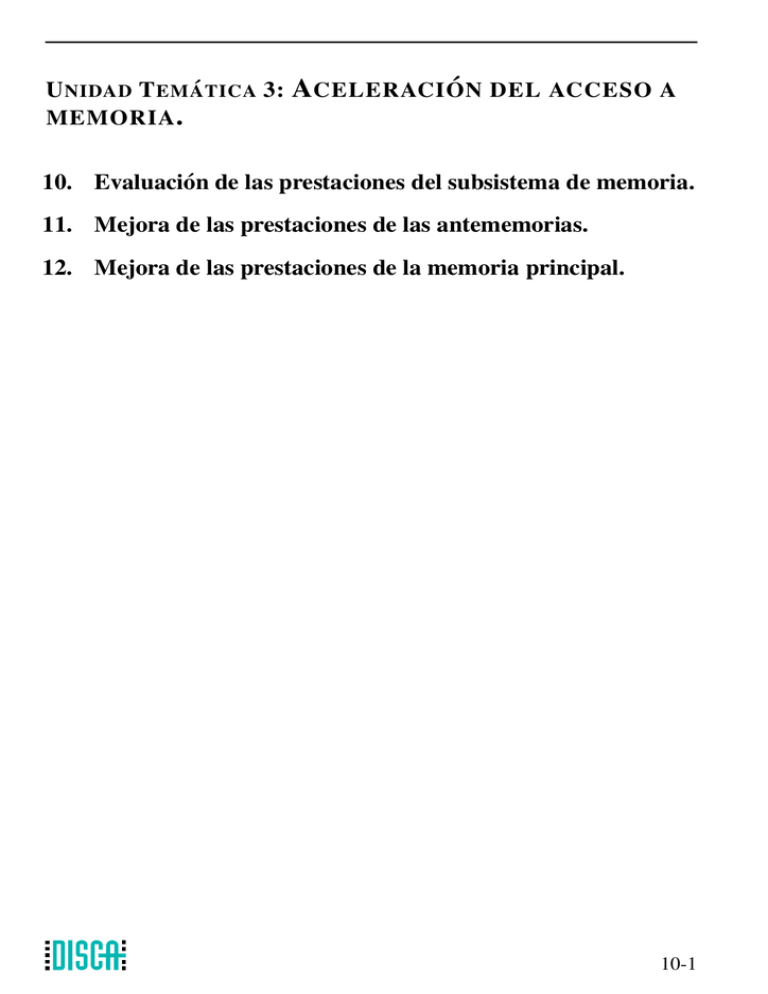

U NIDAD T EM ÁTICA 3: MEMORIA . ACELERACI ÓN DEL ACCESO A 10. Evaluación de las prestaciones del subsistema de memoria. 11. Mejora de las prestaciones de las antememorias. 12. Mejora de las prestaciones de la memoria principal. 10-1 T EMA 10: E VALUACI ÓN DE LAS PRESTACIONES DEL SUBSIS TEMA DE MEMORIA 1. Repaso de la jerarquı́a de memoria. 2. Repaso de la estructura y funcionamiento de las antememorias. 3. Evaluación de las prestaciones del subsistema de memoria. Bibliografı́a: J.L. Hennessy & D. A. Patterson. Computer Architecture: A Quantitative Approach 2a y 3a ed., Morgan Kauffman Publishers, 1996 y 2002. Departamento de Informática de Sistemas y Computadores (DISCA) Facultad de Informática de Valencia 10-2 1 REPASO DE LA JERARQUÍA DE MEMORIA. 1. Repaso de la jerarquı́a de memoria. “...los programadores pretenderán acceder a cantidades ilimitadas de memoria rápida...” → La jerarquı́a de memoria es una solución económica a esta pretensión. Jerarquı́a de memoria Principio de localidad. Los programas tienden a reutilizar el c ódigo y los datos utilizados recientemente. “Un programa gasta el 90 % de su tiempo ejecutando s ólo el 10 % del código” Localidad temporal: los datos accedidos recientemente serán accedidos también en el futuro próximo. Localidad espacial: los ı́tems cuyas direcciones estan cercanas tienden a ser referenciados conjuntamente en un intervalo de tiempo. Coste-prestaciones de las memorias: Cuanto más pequeñas, más rápidas. Cuanto más rápidas, más caras. → Subsistema de memoria organizado en diferentes niveles: 10-3 1 REPASO DE LA JERARQUÍA DE MEMORIA. Jerarquı́a de memoria (cont.) Cada nivel es más pequeño, más rápido y mas caro que el nivel inferior. Objetivo: coste cercano al nivel más barato y velocidad cercana al más rápido. Los datos almacenados en un nivel también están almacenados en el nivel inferior, y ası́ sucesivamente. En cada nivel, hace falta hacer corresponder direcciones del nivel inmediatamente inferior, más grande y más lento, sobre una memoria más pequeña pero más rápida. Tambien se realizan funciones de protecci ón. Importancia de la jerarquı́a de memoria Conforme los procesadores son más rápidos, el diseño de la jerarquı́a de memoria cobra más importancia: Creciente diferencia de velocidad entre procesador y memoria: En 1980, los procesadores no llevaban caches. En 2001, muchos procesadores dos niveles de cache en el propio chip. 10-4 1 REPASO DE LA JERARQUÍA DE MEMORIA. Requisitos diferentes para computadores de sobremesa, servidores, y empotrados Computador de sobremesa. Un usuario, una aplicación. Objetivo: reducir latencia. Servidores. Múltiples usuarios, múltiples aplicaciones Objetivos: ancho de banda, protección. Computadores empotrados. Una aplicacion, a veces sin sistema operativo. Memoria principal pequeña, no hay disco. Objetivos: Tiempo-real (importante conocer las prestaciones del peor-caso). Bajo consumo. Hardware sencillo. Memorias cache o antememorias “Cache: un sitio seguro para esconder o almacenar cosas” Cache: primer nivel de la jerarquı́a de memoria. El principio de localidad se cumple a distintos niveles. El término cache se emplea actualmente cuando se almacena información que se reutilizará: caches de ficheros, cache de disco, cache de nombres, etc. Acierto: cuando el procesador encuentra en la cache el dato solicitado. Fallo: cuando el procesador no encuentra en la cache el dato accedido. Como consecuencia del fallo, un bloque de informaci ón de tamaño fijo que contiene la palabra accedida se copia de la memoria principal a la cache. Tiempo para servir un fallo. Depende de la latencia y ancho de banda de la memoria principal. Latencia. Tiempo necesario para recuperar la primera palabra del bloque. Ancho de banda. Velocidad con que se sirve el resto del bloque. Los fallos de cache se gestionan mediante hardware, y causan que el procesador se detenga hasta que el dato esté disponible. 10-5 1 REPASO DE LA JERARQUÍA DE MEMORIA. Memoria virtual. No todos los objetos referenciados por un programa deben estar en memoria principal. Si soporta memoria virtual, pueden estar en el disco. El espacio de direccionamiento se divide en bloques de igual tama ño (páginas). En un momento dado, una página puede residir en memoria o en disco. Si el procesador referencia un ı́tem dentro de una página que no esté en memoria principal, se produce un fallo de página, y la página entera se transfiere desde el disco hacia la memoria principal. Los fallos de página se gestionan mediante software y no detienen el procesador. El procesador cambia de contexto, ejecutando otra tarea mientras se realiza el acceso al disco. 10-6 2 ABC DE LAS CACHE 2. Repaso de la estructura y funcionamiento de las antememorias. Caracterizando las cache Cualquier nivel de la jerarquı́a de memoria puede caracterizarse respondiendo a las preguntas siguientes: Ubicación de un bloque. ¿Dónde se ubica un bloque en el nivel superior? Identificación de un bloque. ¿Cómo se encuentra un bloque, si está en el nivel superior? Reemplazamiento. ¿Qué bloque se elimina ante un fallo? Polı́tica ante escrituras. ¿Qué se hace ante una escritura? 10-7 2 ABC DE LAS CACHE Ubicación de un bloque. Correspondencia directa. Un bloque sólo puede estar almacenado en un lugar de la cache. La correspondencia es habitualmente: No bloque cache = No de bloque referenciado mod No bloques cache Correspondencia totalmente asociativa. Un bloque puede almacenarse en cualquier lugar de la cache. Correspondencia asociativa por conjuntos. Un bloque puede almacenarse en un conjunto restringido de lugares en la cache. Un conjunto es un grupo de bloques en la cache. Un bloque puede almacenarse en cualquier bloque de uno de los conjuntos, seleccionado habitualmente: No conjunto = No de bloque referenciado mod No conjuntos cache. Si hay n bloques por conjunto, se llama asociativa de n vı́as. Cache de m bloques en total: • Directa es asociativa de 1 vı́a. Hay m conjuntos (de 1 bloque). 10-8 2 ABC DE LAS CACHE • Totalmente asociativa es asociativa de m vı́as. Hay 1 conjunto (de m bloques) Identificación de un bloque Cada bloque almacenado en la cache tiene asociado una etiqueta que indica su dirección. Para saber si un bloque referenciado por el procesador se encuentra en la cache, se compara la dirección del bloque con las almacenadas en todas las etiquetas de la cache. Un bit de válido indica si un bloque de la cache tiene o no informaci ón válida. Partes de una dirección emitida por el procesador: ¿Cómo comparar? En paralelo con todas las etiquetas válidas. Con correspondencia directa, sólo una comparación. No hace falta incluir la palabra dentro del bloque (offset), ya que, el bloque está presente o ausente por completo. El ı́ndice (index) selecciona el conjunto. No hace falta incluir el ı́ndice en la comparación, es redundante. El campo de etiqueta (tag) permite comprobar si el bloque está o no en la cache. Para un mismo tamaño de cache, al aumentar la asociatividad (aumentar el n úmero de bloques por conjunto), se reduce el tamaño del ı́ndice y se aumenta el de la etiqueta. 10-9 2 ABC DE LAS CACHE Reemplazamiento Cuando hay un fallo de bloque, el bloque referenciado debe traerse de la memoria principal y ocupar el espacio ocupado por otro. ¿Cuál de ellos debe eliminarse? Con correspondencia directa, es trivial. Se debe eliminar el que está almacenado en el lugar donde se alojará el nuevo. Con correspondencia asociativa, pueden emplearse varias estrategias: Aleatoria. Se elije un candidato al azar. Fácil de implementar. LRU. Menos recientemente usado. Se pretende reducir el riesgo de eliminar información susceptible de ser utilizada en el futuro. FIFO. Elimina el bloque más antiguo. Más fácil de implementar que LRU. Polı́tica ante escrituras Las operaciones de lectura mucho más frecuentes que las de escritura. ¿Acelerar la lectura de cache? → Leer el bloque al mismo tiempo que se compara la etiqueta. Si es un acierto, la palabra correspondiente se envı́a al procesador. Si es un fallo, se desecha. No hay beneficio, pero tampoco perjuicio (salvo el consumo de energı́a inútil). Escrituras No se puede modificar un bloque hasta que no se confirme que se trata de una acierto. Sólo hay que modificar una palabra (o unas pocas palabras) del bloque. El bloque modificado deberá escribirse también en la memoria principal. 10-10 2 ABC DE LAS CACHE Polı́tica ante escrituras (cont.) Estrategias en caso de acierto: Write-through. La información se almacena tanto en la cache como en la memoria principal. • Más fácil de implementar. • La memoria principal siempre está actualizada. • El procesador debe esperar a que la escritura se complete Solución: write buffer, que permite que el procesador contin úe tan pronto el dato se ha almacenado en el buffer, solapando la ejecuci ón con la actualización de memoria. Write-back. La información únicamente se almacena en la cache. El bloque modificado se escribirá en la memoria principal cuando se reemplace. Un bit dirty indica si un bloque se ha modificado, requiriendo entonces actualizar la memoria principal. • Emplea menos ancho de banda de memoria que Write-through. • Los reemplazamientos requieren escribir en la memoria. Estrategias en caso de fallo de bloque: Write allocate. El bloque se lleva de la memoria principal a la cache. Entonces, se llevan a cabo las acciones de escritura con acierto. Habitual con write-back No-write allocate. El bloque no se lleva a la cache. S ólo se modifica en el nivel inferior. Habitual con write-through 10-11 3 PRESTACIONES DEL SUBSISTEMA DE MEMORIA. 3. Evaluación de las prestaciones del subsistema de memoria. Tiempo de acceso medio Tiempo de acceso med. = Tiempo acierto + Tasa de fallos × Penalizacion por fallo Tacceso = T A + T F × P F . Modificación de la ecuación del tiempo de ejecución para incluir el comportamiento real de la cache: Tej = Tej cpu + Textra memoria , donde Tej cpu incluye el tiempo necesario para gestionar los aciertos de cache y Textra memoria el tiempo necesario para gestionar los fallos1 . Tej cpu = I × CP I × T Textra memoria = Ciclos parada memoria ×T • Ciclos parada memoria = No de fallos × Penalización por fallo = NF × PF • No de fallos = Instrucciones × • Fallos Instruccion = Accesos × Instruccion Fallos Instruccion Tasa de fallos. Sustituyendo: Accesos Ciclos parada memoria = Instrucciones × Instruccion × Tasa de fallos × × Penalización por fallo = I × AP I × T F × P F . Por lo tanto: Textra memoria = I × AP I × T F × P F × T 1 suponiendo que los fallos detienen al procesador 10-12 3 PRESTACIONES DEL SUBSISTEMA DE MEMORIA. Modificación de la ecuación del tiempo de ejecución (cont.) Pueden considerarse por separado las lecturas y escrituras: Accesos Ciclos parada memoria = Instrucciones × Instruccion × Tasa de fallos × × Penalización por fallo = Lecturas × Tasa de fallos lectura × • Instrucciones × Instruccion × Penalización por fallo lectura, más Escrituras • Instrucciones × Instruccion × Tasa de fallos escritura × × Penalización por fallo escritura. Ciclos parada memoria = (I × LP I × T F L × P F L) + +(I × EP I × T F E × P F E) 10-13