Tema 2 - diseño de sistemas electrónicos (1759)

Anuncio

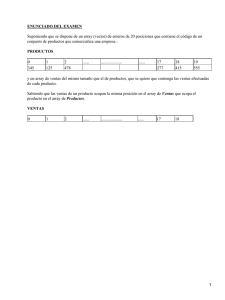

1 Tema II Circuitos Integrados Programables; CPLDs y FPGAs Roberto Gutiérrez Mazón The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www.mentor.com) 2 3.a Full Custom y Semi-Custom. 3.b Mask-Programmable Gate Arrays (MPGA). 3.c PLDs i. SPLDs (PLD simples) ii. CPLDs (PLD complejos) iii. FPGAs 3 Familias Lógicas ASIC PLDs SPLDs (PALs) CPLDs Arrays Puertas FPGAs Lógica Standard Semi Custom Standard Cell Full Custom 4 ¨ Nos surge una pregunta ¿Qué plataforma es la mejor? ¨ Y la respuesta Depende de los requerimientos de la aplicación 5 ¨ Consideraciones a tener en cuenta para la elección de una familia u otra: Ø Retardo Propagación. Ø Cantidad de Lógica empleada. Ø Volatibilidad. Ø Tiempo de Diseño Ø Tiempo empleado en modificaciones. Ø Posibilidades de I/O. Full Custom y Semi-Custom 6 ¨ ¨ ¨ ICs construidos completamente por el diseñador: transistores, conexiones, etc. Emplea máscaras personales para definir cada una de las capas en el proceso de fabricación. El usuario controla la densidad del chip con lo que se puede conseguir una alta utilización del mismo. Ventajas: ¤ ¤ ¨ Inconvenientes: ¤ ¤ ¤ ¨ Máxima flexibilidad en el diseño. Alto rendimiento: Es posible optimizar las partes criticas del diseño consiguiendo un diseño más pequeño y más rápido que el obtenido con herramientas CAD. Diseño complejo y altamente especializado (mucho cuidado con los errores). Tiempo de desarrollo muy alto. Coste de desarrollo alto. Esta alternativa es interesante para producciones de elevado volumen, donde se consiguen amortizar los costes de desarrollo y test. Full Custom y Semi-Custom 7 Materiales de silicato forman el 90% de la corteza terrestre. Sílice (Dióxido de Silicio), se extrae sobre todo para su utilización en el hormigón. Refinado al 95% de pureza es utilizado para la fabricación del aluminio. El silicio para uso electrónico requiere el 99.9999999% de pureza. 8 Full Custom y Semi-Custom 9 Full Custom y Semi-Custom 10 Full Custom y Semi-Custom (MEMS) 11 Caja Cambios Full Custom y Semi-Custom 12 ¨ Cuando se utiliza una metodología de diseño de tipo Semicustom, los diseños se realizan a partir de un conjunto de módulos, Standard Cells, ya diseñados y caracterizados, que se utilizaran como elementos mínimos del diseño. Memoria SRAM 0.25 um Intel Itanium 2 (Montezito) Mask-Programmable Gate Arrays (MPGA): Matrices de puertas y mar de puertas 13 v ¨ ¨ ¨ Matrices de puertas Utiliza patrones predefinidos de transistores y contactos de transistores. La plantilla con los transistores puede fabricarse antes de tener el diseño. El circuito se personaliza con el proceso de metalización. Los transistores y sus contactos se agrupan en células y estas células se ordenan en filas separadas por canales fijos. Características: ¤ ¤ ¤ ¤ Mas fácil que el Full Custom. Tiempos de desarrollo mas cortos. Costes de Desarrollo mas bajos. Solo es necesaria una mascara de rutado. Mask-Programmable Gate Arrays (MPGA): Matrices de puertas y mar de puertas 14 ¨ ¨ ¨ Una clase especial de las matrices de puertas son los Sea-of-Gates. Estos, al contrario que las matrices de puertas no tienen contactos prefabricados, por ello no son necesarios los canales y los transistores pueden llenar todo el chip. El rutado se realiza sobre los transistores no usados. El diseño de Sea-of-Gates solo necesita máscaras para contactos y rutado. Inconvenientes: ¤ Utilizan más silicio y tienen peor velocidad que los diseños Full Custom y Standard Cell. Mask-Programmable Gate Arrays (MPGA): Matrices de puertas y mar de puertas 15 Array de Puertas Array de Puertas (conectado) 2.4 Mask-Programmable Gate Arrays (MPGA): Matrices de puertas y mar de puertas 16 Array de Puertas Rutado Sea of Gate Dispositivos Logicos Programables (PLDs). 17 ¨ ¨ ¨ Son circuitos integrados programables por el usuario y empleados para implementar hardware digital. Igual que los Arrays de Puertas son elementos prefabricados. Las funciones lógicas se implementan programando eléctricamente las interconexiones y personalizando las células básicas. Ventajas: ¤ ¤ ¤ ¤ ¨ Inconvenientes: ¤ ¤ ¤ ¨ Rápida programación y borrado (excepto OTP). Tiempo de desarrollo más corto. Facilidad para realizar cambios. Costes de desarrollo mas bajos. Limita la flexibilidad del diseño. No aprovecha área de silicio. Más lento. El sector de los CPLDs y FPGAs representa uno de los segmentos con crecimiento más rápido en la industria de semiconductores. PLD Simples 18 ¨ Las PLDs sencillas ó SPLDs : ¤ ¤ ¤ ¤ ¨ Tienen una estructuras lógicas de planos AND/OR. Se dispone de un numero de macrocélulas inferior o igual a 16. La mayoría son PAL, también hay PLA y PLE. Son dispositivos de baja densidad. Los diseñadores tienden a dejar los SPLDs que venían usando para trabajar con CPLDs que aportan más velocidad, más densidad, son más fáciles de usar y cuentan con mejores herramientas CAD de diseño electrónico. PLDs SPLDs PROMs PLAs CPLDs PALs GALs etc. PLD Simples 19 Fuses Logic 1 Logic 1 Fat Fat a Pull-up resistors a Pull-up resistors Faf NOT Fbt b & NOT y = 0 (N/A) b AND AND Fbf Fbf NOT Dispositivo sin programar & NOT Dispositivo programado y = a & !b PLD Simples 20 PLA: Programmable Logic Array ¨ ¨ ¨ ¨ ¨ Estos dispositivos fueron los primeros chips desarrollados específicamente para implementar circuitos lógicos (Philips 1975). Su estructura dispone de un plano AND programable seguido de un plano OR también programable. Esta estructura es ideal para implementar funciones lógicas como sumas de productos. El hecho de tener ambas matrices programables hace que el dispositivo tenga mayor tamaño y menos velocidad. Existen variantes de la estructura PLA: ¤ ¤ ¤ ¤ Sólo plano AND u OR Plano AND con realimentación Plano AND+OR con realimentación Con registros o registros programables. PLD Simples 21 c Predefined link Programmable link & & & N/A N/A b c Predefined link Programmable link & & & !b & !c !c Predefined AND array Predefined AND array w x y w = (a & c) | (!b & !c) x = (a & b & c) | (!b & !c) y = (a & b & c) PLA sin programar PLA programada l c a & c l a !a b !b a & b & c l l l l a !a b !b c !c N/A a w x y Programmable OR array b Programmable OR array a PLD Simples 22 PAL: Programmable Array Logic ¨ ¨ a b c Predefined link Programmable link & & & & & & a !a b !b c !c l l l Son los dispositivos SPLDs mas extendidos y variados del mercado. Los primeros dispositivos PAL fueron fabricados por MMI (actual AMD). Solo el plano AND es programable, por lo que son circuitos con mayor velocidad de operación a menor coste. Hay versiones OTP (Programables una vez) y RP (Reprogramables EEPROM). Se dispone de series de 20,24 y 28 pines, con versiones combinacionales y secuénciales. Predefined OR array ¨ Programmable AND array w x y PLD Simples 23 PAL Genericas o universales ¨ Son las PAL con registros mas flexibles que las vistas anteriormente puesto que disponen de una circutería especial conocida con el nombre de Macrocélula. PLD Simples 24 PAL 22VP10 PLD Simples 25 ¨ ¨ ¨ GAL: Generic Array Logic (Lattice, 1984) Son dispositivos borrables eléctricamente diseñados para sustituir a la mayoría de las PALs de la serie general manteniendo la compatibilidad pin a pin. Todos los pines de I/O tienen una macrocélula. Los fusibles de las macrocélulas permiten configurar la GAL en tres modos distintos: ¤ ¤ ¤ ¨ ¨ En modo registro puede emular a la PAL16R8, PAL 16R6, etc. En modo complejo puede sustituir a la PAL16L8, PAL16H8, etc. En modo simple puede funcionar como PAL10L8, PAL16L2, PAL14H4, etc. Reducción del numero de productos del inventario de una empresa. Normalmente es el compilador el que selecciona el modo de funcionamiento elegido en cada diseño. 25 PLD Simples 26 ¨ ¨ ¨ ¨ ¨ ¨ ¨ Todos los pines son bidireccionales. Versiones RP y OTP dependiendo del encapsulado. Flip flops programables como tipo D, T, JK y RS con control individual de reloj y clear Los FF pueden puentearse y se resetean automáticamente cuando se alimenta el circuito. Bit de seguridad programable. El clear de cada FF puede controlarse independientemente y de forma asíncrona con un producto. Como reloj se puede tomar el reloj global del sistema o una señal proveniente de la matriz AND. Familia EPLD de Altera 26 PLD Simples - Programación 27 ¨ Lenguajes Programación ¤ PALASM ¤ ABEL ¤ CUPL Unprogrammed device Programmed device Host computer Device programmer Complex PLDs - CPLDs 28 ¨ ¨ ¨ ¨ Un CPLD extiende el concepto de un PLD a un mayor nivel de integración ya que permite implementar sistemas más eficientes porque utiliza menos espacio, mejoran la confiabilidad en el circuito y reducen costos. Un CPLD se forma de múltiples Bloques lógicos, cada uno similar a un SPLD. Los Bloques lógicos se comunican entre sí utilizando una Matriz Programable de Interconexiones lo cual hace más eficiente el uso del silicio y conduce a un mejor desempeño. En los CPLDs el retardo de propagación es predecible debido a la regularidad de su estructura de interconexiones. Podemos encontrar dispositivos basados en EPROM,E2PROM,SRAM o FLASH. Complex PLDs - CPLDs 29 Matriz de interconexiones Programables (PIM) ¨ Permite unir los pines de I/O a las entradas de los Bloques lógicos, o las salidas del Bloque lógico a las entradas de otro Bloque lógico o inclusive a las entradas del mismo bloque. Bloques Lógicos ¨ ¨ ¨ Un bloque lógico es muy similar a un SPLD, cada uno de ellos poseen generalmente una matriz de puertas AND, una matriz de puertas OR y una configuración para la distribución de los productos en las diferentes macroceldas del bloque. El tamaño del bloque lógico es una medida de la capacidad del CPLD, ya que de esto depende el tamaño de la función booleana que pueda ser implementada dentro del bloque. Los bloques lógicos usualmente tienen de cuatro a veinte macroceldas. Complex PLDs - CPLDs 30 Macroceldas ¨ Las macroceldas son similares a las de un SPLD. Estas también están provistas con registros, control de polaridad y buffers para utilizar salidas Triestado. Celdas I/O ¨ ¨ La función de una celda de entrada/ salida es permitir el paso de la señal hacia dentro o hacia el exterior del dispositivo. Cada celda I/O dispone de un registro con estada de habilitación de reloj. Puede ser empleado como registro de entrada o salida. FPGAs - Field Programmable Gate Array 31 ¨ ¨ ¨ ¨ Combina la Arquitectura de los GateArrays con la programabilidad de los PLDs. Están constituidas por tres elementos configurables: Bloques Lógicos (CLBs) que se comunican mediante Recursos de Interconexión entre si y con el exterior a través de los Bloques de I/O (IOBs) Gran parte del área ocupada en el dado contiene los recursos que permiten el rutado programable. Ventajas: ¤ ¤ ¤ Programmable interconnect Alta densidad de puertas. Ciclo de diseño corto. Bajo coste. Programmable logic blocks 31 FPGAs - Field Programmable Gate Array 32 Bloques lógicos Las FPGAs son dispositivos basados en el concepto de Bloques Lógicos Programables, los cuales están compuestos por una LUT de n-entradas, un F.F. , multiplexores y pequeños elementos adicionales. El diseñador configurara el comportamiento de cada Bloque para realizar diferentes funciones. a b c 3-input LUT y mux flip-flop Bloque Lógico q d clock Required function a b c Truth table & | y = (a & b) | !c y Programmed LUT a b c y SRAM cells 0 0 0 0 1 1 1 1 1 0 1 1 1 0 1 1 1 0 1 1 1 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 000 001 010 011 100 101 110 111 8:1 Multiplexer ¨ abc y FPGAs - Field Programmable Gate Array 33 ¨ Criterios de clasificación: ¤ Técnica de Programación, tenemos, FPGAs configurables por: n n n SRAM, las mas extendidas. Se caracterizan por ser Volátiles y Reconfigurables. Antifusible. Son No-Volátiles y NoReprogramables. Flash o EEPROM, de reciente aparición, las ProASIC de Actel y las ispXPGA de Lattice, emplean estas memorias como fuente única o alternativa de configuración, respectivamente. Son No-Volátiles y Reprogramables. FPGAs - Field Programmable Gate Array 34 Feature SRAM Antifuse E2PROM / FLASH Technology node State-of-the-art One or more generations behind One or more generations behind Reprogrammable Yes (in system) No Yes (in-system or offline) Reprogramming speed (inc. erasing) Fast ---- 3x slower than SRAM Volatile (must be programmed on power-up) Yes No No (but can be if required) Requires external configuration file Yes No No Good for prototyping Yes (very good) No Yes (reasonable) Instant-on No Yes Yes IP Security (especially when using bitstream encryption) Very Good Very Good Size of configuration cell Large (six transistors) Very small Medium-small (two transistors) Power consumption Medium Low Medium Rad Hard No Yes Not really Acceptable The Design Warrior’s Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www.mentor.com) Spartan III 35 Spartan III - Estructura 36 Spartan III – Bloque Lógico 37 Slice 16-bit SRA Bloque Lógico (LC) 16x1 RAM 4-input LUT LUT 16-bit SRA 16x1 RAM MUX REG Bloque Lógico (LC) 4-input LUT LUT MUX REG Spartan III – Bloque Lógico 38 ¨ Bloque Lógico 16-bit SRA 16-bit SRA 16x1 RAM a b c d 16 x 1 RAM 4-input LUT y mux 4-input LUT flip-flop q e clock clock enable set/reset Diagrama Bloque Lógico Simplificado Distintos modos de funcionamiento LUT Spartan III – Bloque Lógico 39 LUT4 configurado para implementar lógica combinacional. LUT4 configurado para implementar un registro de desplazamiento direccionable (SRA). Spartan III - Bloque I/O 40 ¨ Bloque I/O Bloque retardo dinámico Registro DDR Spartan III - Bloque I/O 41 ¨ Standard I/O soportados Spartan III – Bloque DSP48 42 Multiplicador Sumador Acumulador A[n:0] x B[n:0] + Y[(2n - 1):0] MAC Unidad MAC utilizada para DSP Spartan 3A DSP -----------Resto dispositivos únicamente multiplicador Spartan III – Gestión Reloj 43 ¨ Gestión Reloj: ¤ ¤ Se han diseñado arboles de distribución de reloj que nos permiten que el reloj llegue a todos los F.F. de la FPGA en el mismo instante. Se han añadido Bloques de Gestión de Reloj (DCM), el cual nos permite eliminar jitter, síntesis de frecuencias, desplazamientos de fase, correcciones automáticas de skew, etc. Spartan III – Gestión Reloj 44 Clock signal (jitter) Clock Manager etc. clock pad 1.0 x original clk 2.0 x original clk Daughter clock (monitored downstream of the clock manager) fed back to special input .5 x original clk Clock signal from outside world De-skewed daughter clocks used to drive internal clock trees or output pins Special clock pin and pad 1 2 3 90o Phase shifted 4 Main (mother) clock 1 2 3 4 Untreated daughter clock 1 2 0o Phase shifted 3 De-skewed daughter clock 180o Phase shifted 270o Phase shifted Spartan III – Block RAM 45 Modos Configuración BLOCK RAM 45 FPGAs - Programación 46 ¨ ¨ ¨ Proceso por el cual definimos la funcionalidad de la FPGA (SRAM) a partir de un fichero llamado configuration bitstream. Algunos dispositivos permiten la compresión, detección de errores (CRC) y encriptación (AES 256 bits) del archivo de configuración. Además se incluyen numerosas medidas de protección (autentificación, Identificador único (device DNA)). Las FPGAs pueden trabajar en diferentes modos de configuración, dependiendo de las necesidades del diseñador. Además permiten reconfiguraciones parciales, múltiples ficheros de configuración en una única memoria ROM, etc. Configuration data in Configuration data out = I/O pin/pad = SRAM cell Celdas SRAM de configuración. FPGAs - Programación 47 Modos Configuración Spartan 3 Modos Configuración Virtex 5 Secuencias proceso Configuración. FPGAs - Programación 48 ¨ Modo Maestro Serie Modo Serie Daisy-Chain multi-FPGAs. Modo Maestro Serie utilizando Platform FLASH. Modo Ganged Serie multi-FPGAs. FPGAs - Programación 49 ¨ Modo Esclavo Serie FPGAs - Programación 50 ¨ Modo Maestro SPI ¤ ¤ ¤ Modo por el cual podemos utilizar memorias SPI Flash PROM. La FPGA puede tener acceso una vez configurada a la memoria FLASH para leer/ escribir datos. Puede trabajar con distintos fabricantes de memorias FLASH (VS[2:0]). Actualmente solo funciona con memorias de STMicro y Atmel (Impact). Modo Master SPI Acceso Memoria FLASH sistema Embebido FPGA FPGAs - Programación 51 ¨ Modo Maestro SPI interno ¤ Solo únicamente disponible en la familia de dispositivos Spartan 3AN (disponen de hasta 16 Mbits de memoria FLASH interna). FPGAs - Programación 52 ¨ JTAG ¤ ¤ Estándar basado en la especificación IEEE 1149.1 para implementar técnicas de boundary scan para testear IC y PCBs. Dispone de 4 o 5 pines: n n n n n ¤ ¤ TDI: Pin entrada serie para todas las instrucciones y datos. TDO: Pin de salida para todas las instrucciones y datos. TMS: Pin para selección del modo de funcionamiento del controlador JTAG. TCK : Pin entrada de reloj JTAG TRST: Pin Reset (opcional). Podemos encadenar múltiples dispositivos. Nos permite acceder a los nodos internos de la FPGA además de poder testear el dispositivo. Modo JTAG FPGAs - Programación 53 Controlador JTAG Lógica Boundary-Scan incluida en los I/O.