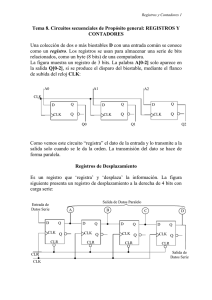

Documento 87407

Anuncio

ELECTRÓNICA DIGITAL. Curso 2003-0 4 1ª autoevaluación PROBLEMA 1.- Dado el circuito de la figura discutir si la puerta 74LS15 tiene un FAN-OUT (cargabilidad) suficiente para actuar sobre el transistor y mantener los niveles de tensión en la puerta 74LS32. En caso afirmativo, calcular la resistencia de base del transistor para que el transistor trabaje en corte -saturación. Datos : Rele: 12V/230 ohm BD135: beta sat=40 74LSXX: VIHmin=2v IIHmax=-0,02mA ICmax =1,5A VCEsat=0,5 VBEsat=1,1 VILmax=0,8v IILmax=-0,4mA VOHmin=2,7v IOHmax=-0,4mA VOLmax=0,4v IOLmax=8mA 12V L1 3 1 S 12V/230 R1 Q1 BD135 A U2A U1A B 1 2 1 2 13 12 74LS04 C U3A 74LS15 1 3 2 C E 74LS32 PROBLEMA 2 .- Se desea diseñar un sistema de iluminación automática para un aula. Se dispone de un elemento fotosensible (LDR) montado hacia el exterior que determina si el nivel de iluminación natural es suficiente. Además, en lugar del interruptor ha bitual de encendido de las luces, se instalan 2 pulsadores A y B con las siguientes funciones: Pulsador A: Cada vez que se pulsa conmuta de modo automático a manual y viceversa. En modo automático el control de las luces se realiza mediante el sensor fotoeléctrico (LDR), de modo que si la LDR detecta oscuridad se encienden las luces y en caso contrario se apagan. Se instalará un LED rojo indicador de este modo. En modo manual el sistema responde únicamente al pulsador B. Pulsador B: Cada vez que se pulsa produce el encendido/apagado de las luces. Solo funciona si se ha seleccionado el modo manual. El sistema posee otro indicador a LED (LED verde) que se ilumina si las luces están encendidas. El diagrama de bloques del sistema es el mostrado en la figura: ELECTRÓNICA DIGITAL. Curso 2003-0 4 1ª autoevaluación CIRCUITO A DISEÑAR Diseñar el circuito digital que implemente el control de iluminación utilizando puertas lógicas y biestables (para la adaptación de los pulsadores) de la familia HCT cuyas hojas características se adjuntan. Calcular los valores de las resistencias necesarias teniendo en cuenta los datos: LDR: Rosc=10K; Rluz=1K Q1 (BD135): HFEmin=40 RELÉ : 12V, 270Ohm. LED : VAK=1.5V, IL=5mA. PROBLEMA 3 .- Diséñese un circuito con el C.I. 555 en modo monoestable para proporcionar un pulso de 10 ms cada vez que se aplica un pulso de disparo en la entrada. PROBLEMA 4.- Una de las funciones de un sistema de alarma para una casa, consiste en que cuando la alarma se conecta, provoca la activación de un led que parpadea una vez por segundo. Si disponemos de alimentación a 5V, realiza las siguientes actividades: a) Diseña un sistema que, al conectar el interruptor para la conexión de la alarma ACT, proporcione alimentación al sistema digital. b) Configura un temporizador 555 como astable para que produzca un pulso cada segundo. c) Diseña la red necesaria a la salida del temporizador, para que con cada pulso que entregue a la salida, se encienda un led.(Iled=20mA., Vled=1.7V). ELECTRÓNICA DIGITAL. Curso 2003-0 4 1ª autoevaluación PROBLEMA 5.- Dado el siguiente montaje, determina cuál es la salida Q3, para la secuencia de entrada que se entrega en la figura que acompaña. (S=Set, R=Reset, activos a nivel H). CLK E S R PROBLEMA 6..- En el siguiente esquema, con un registro de desplazamiento 74194, que utiliza una señal de reloj de periodo 10 ìs generada con un temporizador 555, introducimos un pulso de entrada de 5 ìs de duración. Dibuja la señal en la salida Qc. U1 74194 CA555 CLR QA CLK QB CONT S0 QC THRES S1 QD TRIG SLSER VCC C2 10,0n RESET OUT DISC GND Salida SRSER C1 22,0n R1 560,0 R2 330,0 V1 5,0 A B C D Pulso entrada CLK E E=Pulso de entrada PROBLEMA 7.- Partiendo del CI 74LS194, registro de desplazamiento universal de 4 bits, diseñar un registro de desplazamiento de 8 bits que disponga de: ü ü ü ü Posibilidad de desplazamiento en ambos sentidos. Entrada única de datos serie. Entradas de datos en paralelo. Entrada para el borrado del registro ELECTRÓNICA DIGITAL. Curso 2003-0 4 1ª autoevaluación PROBLEMA 8.- Diseñar un contador asíncrono up/down de 2 bits (no existe ninguno comercial). El contador se basa en dos biestables JK 74LS112 y en un sistema a diseñar tal como se muestra en la figura. Realizar el conexionado adecuado y diseñar el bloque indicado para que se produzca el up/down (up a nivel alto y down a nivel bajo). U U4A U3A CK 1 15 4 J K CLK Q Q 5 6 A C CLR PRE 74LS112 1 15 4 B U/D 3 2 3 2 J K Q Q 5 6 CLK CLR PRE 74LS112 DISEÑAR Q0 Q1 UD PROBLEMA 9.- Conectar adecuadamente el contador 74LS93 para que efectúe una cuenta de 0 a 8. PROBLEMA 10.- Realizar un contador de 3 a 7 con el CI 74LS169. ELECTRÓNICA DIGITAL. 1ª autoevaluación 74HCT00: BD135 Curso 2003-0 4 ELECTRÓNICA DIGITAL. 1ª autoevaluación 555 Curso 2003-0 4 ELECTRÓNICA DIGITAL. 1ª autoevaluación 74LS194 74LS169 Curso 2003-0 4