Buses de expansión. - IES Juan de la Cierva. Vélez

Anuncio

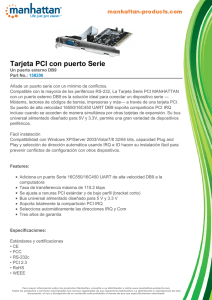

MANTENIMIENTO DE EQUIPOS INFORMÁTICOS Ignacio Moreno Velasco UNIVERSIDAD DE BURGOS Versión 7.0 Abril 2012 4.- LA PLACA BASE DEL PC: BUSES DE EXPANSIÓN. Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Tabla de contenido 4.2.- BUSES DE EXPANSIÓN 4.2.1.- 4 Comunicación con los dispositivos de E/S 4 4.2.1.1.- E/S Programada: 4 4.2.1.2.- Interrupciones hardware 4 4.2.1.3.- DMA (Acceso directo a memoria) 5 Ventajas e inconvenientes ..................................................................................... 5 4.2.2.PCI (Peripheral Component Interconnect) 6 4.2.2.1.- Arquitectura 6 Puentes Host-PCI ................................................................................................ 6 Puente PCI a ISA (PCI to ISA bridge).......................................................................... 6 Puentes PCI-PCI.................................................................................................. 7 4.2.2.2.- Señales del bus 8 4.2.2.3.- Transferencia de datos 9 Fase de direccionamiento...................................................................................... 9 Fase de transferencia de datos ..............................................................................10 Fin de la transferencia ........................................................................................10 Control de errores..............................................................................................10 4.2.2.4.- Control del bus 11 Señal LOCK#.....................................................................................................11 Ranuras master y slave ........................................................................................11 4.2.2.5.- Configuración 12 1º BIOS ...........................................................................................................12 2º Sistema operativo ...........................................................................................12 4.2.2.6.- Interrupciones hardware 14 Reconocimiento de la interrupción..........................................................................14 Compatibilidad .................................................................................................15 4.2.2.7.- Extensiones de la revisión 2.1 16 Extensión a 64 bits .............................................................................................16 Extensión a 66 Mhz.............................................................................................16 Direccionamiento de 64 bits..................................................................................16 4.2.2.8.- PCI-X 17 Revisión 1.0: ....................................................................................................17 Revisión 2.0 .....................................................................................................17 4.2.2.9.- PCI Hot-Plug 18 Elementos implicados .........................................................................................19 Versiones ........................................................................................................19 Ejemplo: sistema con 2 puentes PCI-X y ranuras Hot-plug ..............................................19 4.2.3.PCI Express 20 4.2.3.1.- Características de transmisión 20 Transmisión diferencial .......................................................................................20 Transmisión síncrona ..........................................................................................20 Transmisión bidireccional.....................................................................................20 Enlace múltiple .................................................................................................21 Transmisión isócrona ..........................................................................................22 Distancia .........................................................................................................22 4.2.3.2.- Evolución del PCI Express 23 Características PCI Express® 3.0: ...........................................................................23 4.2.3.3.- Mantenimiento 23 Conector .........................................................................................................23 Tema 4: Placa base versión 7.0 2/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Consumo energético ...........................................................................................23 Ahorro de costes................................................................................................24 Conexión sustitución...........................................................................................24 Integridad de la señal .........................................................................................24 Errores ...........................................................................................................24 Compatibilidad con PCI........................................................................................24 Interrupciones Hardware......................................................................................25 4.2.3.4.- Topología de sistemas PCI-Express 26 Ejemplos de aplicación:.......................................................................................27 Tema 4: Placa base versión 7.0 3/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos 4.2.- BUSES DE EXPANSIÓN Permiten la comunicación de la CPU y de la memoria hacia/desde las distintas controladoras hardware de los periféricos del sistema (Video, puertos, discos duros, etc). Físicamente están implementados mediante pistas de circuito impreso y disponen de ranuras donde conectar tarjetas de expansión: PCI, PCI-Express No contemplan cables como sí hacen los buses periféricos (USB, e-SATA). 4.2.1.- COMUNICACIÓN CON LOS DISPOSITIVOS DE E/S Las tres técnicas básicas de controlar la transferencia de datos hacia/desde un periférico son: 4.2.1.1.- E/S Programada. Interrupciones. DMA (Acceso directo a memoria). E/S Programada: En inglés programmed I/O (PIO) esta técnica se basa en la ejecución de instrucciones E/S como la IN y OUT del repertorio del 8086. Mediante esta técnica la CPU envía una orden al dispositivo (lectura, escritura, configuración, chequeo), y se mantiene ocupada hasta que concluye la operación. El dispositivo no interrumpe a la CPU para comunicar que ya ha terminado la operación, sino que es la CPU quien debe ocuparse de comprobarlo periódicamente, consumiendo así mucho tiempo de CPU. 4.2.1.2.- Interrupciones hardware Cada dispositivo pide servicio a través de una linea de interrupción. Desde el 8086 se dispone de una entrada de petición de interrupción (INTR - INTerrupt Request) y una salida de concesión de interrupción (INTA – INTerrupt Acknowledge). Ante la posibilidad de que varios dispositivos activen su interrupción simultaneamente, las interrupciones no las trata directamente la CPU, sino un controlador. En los primeros PC’s, el circuito integrado 8259 o compatible conocido como PIC que ahora se encuentra integrado en el puente sur. Actualmente se emplean otros mecanismos. 5 Controlador 1 Controlador a de red IRQ 9 Driver RED de Linea IRQ9 E000:01AA interrupcione s 8259 3 2 INTR INTA CPU 4 0000:01C7 0000:01C4 E000:01AA Figura 1: Secuencia de ejecución de una interrupción harware Tema 4: Placa base versión 7.0 4/27 Ignacio Moreno Velasco 1) El dispositivo Apuntes Mantenimiento de Equipos Informáticos pide servicio a través de una de las lineas de interrupción. En la figura la controladora de red usa la interrupción hardware IRQ9 que corresponde a la interrupción nº 71h de la tabla de vectores de interrupción, según la tabla que veremos más adelante. 2) El controlador de interrupciones activa la señal INTR de la CPU. 3) El micro guarda en la pila el estado actual de los registros, deshabilita la posibilidad de atender cualquier otra interrupción (mediante el flag IF) y accede a la petición activando la señal INTA. 4) El controlador de interrupciones 8259 sitúa en el bus de datos el vector de interrupción. Cada IRQ tiene asignada una posición de memoria (vector de interrupción) donde se halla la dirección del controlador (driver) que se ocupará de tratar dicha interrupción. (En el ejemplo el vector nº 21h que ocupa las direcciones 1C4 – 1C7, es decir 4 bytes) 5) Se ejecuta la rutina de atención que puede hallarse en memoria RAM o en el BIOS. 6) Se restaura el estado de los registros desde la pila al estado anterior de atender la interrupción. Esto incluye volver a habilitar las interrupciones (flag IF). 7) Se continúa la ejecución del programa en el punto donde se interrumpió. También existen las llamadas “interrupciones software”. Se “llaman” desde un programa para hacer que se ejecute una función del BIOS o del DOS que accede al hardware. Estas funciones son contempladas por la CPU como subrutinas, que una vez finalizadas, devuelven el control al programa que las llamó. 4.2.1.3.- DMA (Acceso directo a memoria) La técnica DMA (Direct Memory Access) permite transferir datos entre un dispositivo y memoria o de una zona de memoria a otra sin la intervención del micro (excepto para arbitrar la transferencia). Esto es mas rápido que el método tradicional donde cada dato llega a la CPU que lo graba en memoria. Requiere de un dispositivo que controle la operación en sustitución del micro. El bus ISA permite DMA mediante el obsoleto controlador DMA (8237). El bus PCI ya contempla entre sus características la posibilidad de acceder a memoria, por lo que no necesita de hardware adicional. Ventajas e inconvenientes Es útil cuando se deben transferir grandes bloques de datos (P. ej. lectura/escritura en disco). No es tan útil cuando la CPU tiene que procesar uno por uno los datos que se leen/escriben. Tema 4: Placa base versión 7.0 5/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos 4.2.2.- PCI (PERIPHERAL COMPONENT INTERCONNECT) Su arquitectura es independiente del procesador, por lo que es necesario que entre ambos haya un controlador de bus. Esto permite su utilización en otras plataformas (Alpha, Power PC, etc.). Así por ejemplo, una misma tarjeta pueda instalarse en sistemas distintos, cambiando únicamente los controladores de dispositivo (drivers). Bus paralelo, compartido, de 32 bits de datos y direcciones. Bus de direcciones y datos multiplexados en las lineas AD[31-0]. Esto permite al conector mantener unas medidas reducidas a costa de aumentar la latencia. Hasta la llegada de la versión 2.1 sólo funcionaba a 33,3 MHz. Velocidad de transferencia máxima teórica: 33,3 MHz x 32 bits 127 MiB/s. 4.2.2.1.- Arquitectura Los dispositivos de conexión al bus, generalmente circuito integrados son llamados puentes (bridges): Puentes Host-PCI El elemento principal de un sistema basado en PCI es el llamado puente Host-PCI que conecta micro y bus. Figura 2: Sistema basado en un puente Host-PCI Figura 3: Sistema basado en dos puentes Host-PCI Puente PCI a ISA (PCI to ISA bridge) Es un circuito integrado que permite colgar un bus ISA de un bus PCI consiguiendo que convivan ambos buses en una misma placa base. Este elemento se encuentra integrado en el puente sur del chipset, como por ejemplo, en la Figura 4: Figura 4: Puente sur Intel PIIX4E que incluye un puente del bus PCI al bus ISA Tema 4: Placa base versión 7.0 6/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Puentes PCI-PCI Permite incrementar la capacidad del bus a un mayor número de dispositivos. La arquitectura Bridged Bus utiliza un puente de bus PCI a PCI para ampliar la capacidad de dispositivos. Estos puentes suelen ser ASICs (Circuitos integrados de propósito específico) que aislan eléctricamente dos buses PCI, permitiendo que las transferencias pasen de un bus a otro. Figura 5: Arquitectura “bridge bus” para la ampliación del bus de expansión mediante puente PCI-PCI Ejemplo: chipset Intel 440 BX: La Figura 6 constituye un ejemplo típico de la arquitectura “bridge bus”. Podemos observar: Puente Host-PCI entre la CPU-Memoria y el bus PCI #0 del que cuelgan 4 ranuras y el 82371EB. Circuito integrado 82371EB que contiene un puente PCI-PCI del que cuelgan: Controladoras IDE, USB y SMB. Un puente PCI-ISA. Figura 6: Sistema basado en chipset Intel 440 BX Tema 4: Placa base versión 7.0 7/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Figura 7: Arquitectura de un sistema Macintosh basada en PCI. 4.2.2.2.- Señales del bus A continuación se enumeran las señales que componen el bus PCI en sus primeras versiones. AD[0-31]: (AdressData). Estas 32 señales corresponden tanto al bus de direcciones como al bus de datos, ya que se encuentran multiplexados. Esto permite una ahorro de 32 líneas, patillas, contactos o cables, según el caso, a costa de aumentar la latencia. C/BE[0-3]#: En estas 4 señales se encuentran multiplexados en el tiempo las órdenes de bus (Command) y las habilitaciones de byte (Byte Enable). Las órdenes de bus definen el tipo de transferencia que se quiere realizar. Las habilitaciones de byte sirven para determinar la validez de cada uno de los cuatro bytes que se intercambian en cada operación de transferencia. Por ejemplo, cuando estas líneas funcionan como habilitación de byte, un valor 0001 indica que solo el último byte es válido, por lo que deben ingnorarse los tres primeros. Se permiten así transferencias de datos de tamaños distintos a 32 bits. PAR: Esta señal implementa el sistema de paridad empleado para la detección de errores en la transmisión. Se emplea paridad par sobre el conjunto de los 36 bits de las señales anteriores. CLK: Proporciona la señal de reloj que sincroniza todas las operaciones. Como se ha mencionado, se puede tratar de un reloj de 33 o 66 MHz. RST#: Se emplea para inicializar los dispositivos PCI colocando en sus registros de configuración los valores originales. Se trata de una señal activa a nivel bajo. FRAME#: También activa a nivel bajo, indica el inicio de una operación de transferencia. Lógicamente es el maestro quien se encarga de activarla. IRDY#: (Initiator ReaDY). Con ella el maestro indica que está listo para completar una transferencia de datos: Si se trata de una transferencia para escritura, indicará que los datos son válidos. Si la transferenica es de lectura, establece que el maestro está listo para recibirlos. TRDY#: (TaRget ReaDY) Tiene el mismo funcionamiento que la anterior, pero en este caso referida al esclavo. Tema 4: Placa base versión 7.0 8/27 Ignacio Moreno Velasco STOP#: Apuntes Mantenimiento de Equipos Informáticos Es empleada por el esclavo para pedir al maestro que concluya la operación de transferencia en curso. LOCK#: Mediante esta señal un maestro solicita un acceso exclusivo para realizar múltiples operaciones de transferencia sobre un mismo esclavo. IDSEL: (Initialization Device Select). Permite realizar operaciones de lectura o escritura de la configuración de los dispositivos PCI. Existe una de estas señales en cada ranura. DEVSEL#: (Device Select). Es activada por un esclavo cuando reconoce su dirección en el bus. REQ#: (REQuest). Es activada por un maestro para solicitar la utilización del bus. Existe una de estas señales para cada maestro. GNT#: (GraNT). Indica que el maestro que ha solicitado el uso del bus ha sido autorizado a utilizarlo. Obviamente también existe una de estas señales por cada maestro. PERR#: (Parity ERRor). Se emplea para indicar que se ha detectado un error de paridad durante una transferencia. SERR#: (System ERRor). Se emplea para señalar un error grave de sistema. INTA #: Señal de petición de interrupción empleada por un dispositivo PCI para reclamar la atención de su correspondiente controlador software (driver). INTB#, INTC#, INTD#: Señales de interrupción empleadas por los dispositivos PCI multifunción. Por ejemplo una tarjeta de modem que incluya un chip de sonido utilizaría INTA# y INTB#. 4.2.2.3.- Transferencia de datos En terminología PCI las transferencias de datos se realizan entre un iniciador (initiator) que asume el control del bus (bus master) y un destinatario (target) que funcionará como esclavo (bus slave). Una transferencia de datos está compuesta por una primera fase de direccionamiento y por una o varias fases posteriores de lectura/escritura de datos. Estas fases se explican a continuación: Fase de direccionamiento Las 4 líneas denominadas C/BE[3:0]# (Command/Byte Enable) se encuentran multiplexadas, de manera que durante esta fase se utilizan para codificar órdenes. La fase de direccionamiento comienza con la activación de la señal FRAME#. Durante esta fase El iniciador activa las señales C/BE[3:0]# que codifican el tipo de transferencia que va a tener lugar (Lectura de memoria, escritura en memoria, lectura de dispositivo E/S, escritura en dispositivo E/S, etc...). Las direcciones aparecen en el bus multiplexado, lineas AD[31-0]. El sufijo # ante el nombre de una señal indica que es activa a nivel bajo. Tema 4: Placa base versión 7.0 9/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Tabla 1: Señales de control del bus PCI. C/BE[3:0]# Orden 0000 0001 0010 0011 0100 Interrupt Acknowledge Special Cycle I/O Read I/O Write Reserved 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 Reserved Memory Read Memory Write Reserved Reserved Configuration Read Configuration Write Memory Read Multiple Dual Address Cycle Memory Read Line Memory Write and Invalidate Fase de transferencia de datos Durante esta fase las señales multiplexadas C/BE[3:0]# se utilizan como Byte Enable, es decir, indican cual de los 4 bytes de datos es válido y cual no. Esto permite transferencias de datos de longitud variable: Los datos aparecen en el bus multiplexado, lineas AD[31-0]. Tanto el iniciador como el destinatario pueden insertar estados de espera durante la transferencia desactivando las señales IRDY# (Initiator ReaDY) y TRDY# (Target ReaDY). Fin de la transferencia El iniciador puede terminar la transferencia desactivando la señal FRAME# durante la última fase de datos. El destinatario puede finalizar la transferencia activando la señal STOP#. La multiplexación de direcciones y datos hace que la se necesiten al menos 2 ciclos de reloj para una transferencia simple de datos. De esta forma la velocidad de transferencia se reduciría a la mitad. Para paliar esto el bus PCI contempla la transferencia de ráfagas de datos (burst mode) como veremos a continuación. Control de errores El bus dispone de la señal PAR que compone la paridad par sobre las señales AD[31:0] y BE[3:0]#. Esta señal tiene la misma temporización que AD[31:0] pero retrasada un ciclo de reloj para permitir el cálculo de paridad. Tema 4: Placa base versión 7.0 10/27 Ignacio Moreno Velasco 4.2.2.4.- Apuntes Mantenimiento de Equipos Informáticos Control del bus A diferencia del bus ISA que proporciona un controlador específico para el acceso directo a memoria de los periféricos (Controlador DMA 8237), PCI no proporciona un circuito especial para ese propósito. En cambio contempla un mecanismo de transferencia llamado Bus mastering. El iniciador activa la señal REQ# (REQuest=petición) para indicar al controlador PCI que desea tomar el control del bus. El controlador PCI confirma la propiedad del bus activando la señal GNT# (GraNT=cesión) convirtiendo al iniciador en lo que se conoce como Bus master. Señal LOCK# El iniciador puede activar la señal LOCK# pidiendo acceso exclusivo al bus para realizar múltiples transacciones con el destinatario. Impide que otros iniciadores modifiquen las direcciones bloqueadas (mínimo de 16 bytes Figura 8: Transferencia a memoria de una tarjeta de adquisición de datos siBus mastering (arriba) y conus mtering (abajo). National Instruments. bloqueables). Durante el bloqueo pueden realizarse otras transacciones no exclusivas a direcciones no bloqueadas. Figura 9: Configuración del tiempo que puede bloquearse el bus en el BIOS Setup de una placa base En este modo ráfaga, con un solo ciclo de direccionamiento pueden realizarse varios ciclos de transferencia de datos a direcciones consecutivas, disminuyendo drásticamente la latencia y rozando los teóricos 127 MiB/s (133MB/s). Ranuras master y slave Cada slot PCI tiene sus propias lineas REQ# y GNT# que van unidas al controlador PCI. Por ejemplo el Host Bridge incluido en el puente norte de los chipsets de Intel dispone de 4 patillas para REQ# y otras 4 Tema 4: Placa base versión 7.0 11/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos para GNT#. Es por esto que, en principio, sólo puede haber 4 ranuras PCI con capacidad Bus master en las placas madre basadas en esos chipsets. Figura 10: Algunas placas base con las primeras versiones del estándar PCI añaden un quinto slot llamado "Slave" . Éste no puede alojar tarjetas bus master, al no disponer de las señales REQ# y GNT# y debe realizar las tareas de transferencia mediante interrupciones (modo PIO), lo que involucra al procesador. Sin embargo el puente sur Intel® ICH7, más moderno, especifica sobre la interfaz PCI que incluye: - Supports PCI Rev 2.3 Specification at 33 MHz - New: Six available PCI REQ/GNT pairs 4.2.2.5.- Configuración Cada dispositivo PCI incluye un conjunto de registros de configuración que permiten identificar su tipo (RAID, vídeo, Ethernet, etc...), y fabricante. Además, otros registros de configuración permiten la asignación de recursos: direcciones E/S, direcciones de memoria e interrupciones que se necesitan para la comunicación con el sistema. 1º BIOS Durante el arranque, las rutinas PCI/PnP del BIOS asignan los recursos a los dispositivos y guardan esta información dentro de la CMOS-RAM (ocupando memoria superior: E000EDFF) en una parte que se denomina ESCD (Extended System Configuration Data). Esto permite que la información permanezca hasta el próximo arranque. (Salvo que se active la opción “Clear ESCD” desde el BIOS-Setup). Figura 11: Recursos del sistema usados por una tarjeta de red Para acceder a las rutinas PCI del BIOS se utiliza la interrupción software INT 1AH. Antes debe escribirse el valor 1BH en la parte alta del acumulador, y el número de función en la parte baja del acumulador. 2º Sistema operativo Después de que las rutinas PCI del BIOS han inicializado los dispositivos, el control pasa al sistema operativo. Aquí es donde el sistema operativo comienza a cargar los drivers. El driver llama a las rutinas Tema 4: Placa base versión 7.0 12/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos BIOS PCI para obtener información sobre los recursos que "su" hardware utiliza. Para ello usa la identificación del dispositivo (ID) y el nº de fabricante (p. ej. 8086 = Intel). Durante la carga de drivers, el bus PCI permanece bajo el control del sistema operativo, pero una vez finalizada el control vuelve al BIOS. Figura 12: Asignación de dispositivos PCI incluidos en el puente sur de Intel 82801 ICH3. Windows 9x puede acceder directamente a los registros de configuración de los dispositivos y además puede acceder al ESCD. Esto le permite modificar las asignaciones de recursos de cada dispositivo. Sin embargo desde Windows NT nunca se usa el ESCD. El sistema operativo utiliza llamadas directas a los registros de configuración de los dispositivos. Figura 13: Observar como puede elegirse si el proceso será automático o manual y además puede borrarse el ESCD desde el BIOS Setup ante un eventual conflicto surgido por la instalación de una nueva tarjeta. Figura 14: Ejemplo de configuración desde el BIOS setup. Tema 4: Placa base versión 7.0 13/27 Ignacio Moreno Velasco 4.2.2.6.- Apuntes Mantenimiento de Equipos Informáticos Interrupciones hardware Cada ranura PCI cuenta con 4 lineas ( INTA#, INTB#, INTC#, INTD#) para solicitar interrupción al controlador PCI. Las tarjetas insertadas pueden utilizar una linea para cada función que implementen. Una tarjeta que únicamente implementa una función (P. Ej. tarjeta de red) utilizará solamente la linea INTA#. Sin embargo, una tarjeta PCI que incorpore interfaz de red y modem utilizaría INTA#, INTB#. Figura 15: Pines de petición de interrupción de un dispositivo PCI P. ej. La tarjeta de red Kingston KNE30BT especifica: I/O Base Address: 0000h-FFFFh (set by BIOS PCI). Interrupt (IRQ) Levels: INTA (set by BIOS PCI). El controlador PCI cuenta con varias líneas (PIRQA#, PIRQB#, PIRQC#, PIRQD#, etc.) que se conectan a las de las ranuras y dispositivos PCI integrados: INTA#, INTB#, INTC#, INTD#. Reconocimiento de la interrupción El reconocimiento de interrupción es una orden de lectura proporcionada por el dispositivo que actúa como controlador de interrupciones en el bus PCI. Las líneas de direcciones no se utilizan en la fase de direccionamiento, y las líneas BE# indican el tamaño del indentificador de interrupción a devolver. Fase de direccionamiento: Las líneas C/BE# contienen 0000 Interrupt Acknowledge. (véase Tabla 1) Las líneas de direcciones no se usan en esta fase Fase de datos: Se transfiere el vector de interrupción a la CPU. Este vector apuntará al código encargado de gestionar las necesidades del dispositivo que ha solicitado la interrupción, es decir, el llamado driver del dispositivo. Tema 4: Placa base versión 7.0 14/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Compatibilidad De la compatibilidad con las interrupciones estándar (IRQs) se encarga el enrutador de interrupciones que forma parte del controlador PCI que enruta las INTn# hacia las IRQs: Figura 16: PCI Interrupt Table. Placas base Asrock de la serie K7S8X con 6 ranuras PCI. Los dispositivos pueden utilizar las lineas INTx# de las ranuras PCI que son redirigidas a las IRQs por el enrutador según una tabla que reside en la BIOS PCI. Los dispositivos PCI pueden entonces usar su linea INTx# para generar la IRQ y mantener así la compatibilidad con el software antiguo. Hasta hace poco era muy común el llamado puente PCI-ISA (PCI to ISA bridge) que formaba parte del puente sur desde la aparición del bus PCI (P. Ej. Incorporado en el PIIX4 de los chipsets 430TX, 440LX y 440BX). Como su nombre indica tiene como propósito mapear los viejos dispositivos ISA en el bus PCI, permitiendo su coexistencia. Supongamos que tenemos una aplicación MS-DOS diseñada para una tarjeta de sonido ISA antigua. Deseamos que dicha aplicación funcione sobre una tarjeta PCI. Ese viejo software usará un driver MS-DOS que accede al hardware mediante una IRQ y puertos E/S. Cuando la tarjeta PCI requiera servicio activará su linea INTx#. Mediante la tabla de la BIOS PCI se enrutará dicha petición generando la IRQ que el driver espera. Esto hará que la CPU busque el vector de interrupción correspondiente a esa IRQ y se ejecute el driver MS-DOS. La BIOS puede asignar más de una IRQ al mismo dispositivo. Además dos dispositivos pueden compartir la misma IRQ. Este aparente conflicto lo resuelve el sistema operativo, que cuando activa una interrupción, llama de forma encadenada a cada gestor de interrupción hasta que uno de ellos reclama dicha interrupción. Tema 4: Placa base versión 7.0 15/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Figura 17: En la imagen podemos observar como en un sistema la interrupción 9 es compartida por todos los dispositivos PCI además de un dispositivo ISA. 4.2.2.7.- Extensiones de la revisión 2.1 Extensión a 64 bits Utiliza un conector extendido compatible con tarjetas de 32 bits. Dobla el ancho de banda teórico, lo que permite soportar mejor tecnologías como Gigabit Ethernet y Fibre Channel. Extensión a 66 Mhz Motivos de carga eléctrica y restricciones en la temporización impiden soportar más de dos dispositivos. Para solucionar este problema se suele utilizar la arquitectura peer bus vista Figura 18: Tarjetas y ranuras PCI de 32 bits y 64 bits anteriormente. Pueden conectarse dispositivos de 33 MHz en un bus de 66 MHz. Hay que tener en cuenta que el bus trabajará tan rápido como el más lento de los dispositivos conectados. Este bus resulta ideal para interconexiones de sistemas que formen un cluster donde es crítica la baja latencia de las señales de control y datos entre los servidores del cluster. Velocidad transferencia Frequencia Bus 32-Bit 64-Bit 33 MHz 127 MiB/seg 254 MiB/seg 66 MHz 254 MiB/seg 508 MiB/seg Direccionamiento de 64 bits. La especificación 2.1 de PCI define la capacidad de direccionar mas de 4 GB (32 bits 232 = 4 GB) de memoria del sistema mediante el uso de 64 bits de direcciones. Este direccionamiento es posible en Tema 4: Placa base versión 7.0 16/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos dispositivos de 32 bits, pero necesitan que la fase de direccionamiento dure dos ciclos de bus, mientras que los dispositivos de 64 bits lo hacen en uno. 4.2.2.8.- PCI-X Ante la creciente demanda de ancho de banda de servidores y estaciones de trabajo, se desarrolló esta mejora del bus PCI. Se destacan a continuación algunas características: Mejoras en el protocolo que permiten un uso más eficiente del bus. Compatibilidad con PCI convencional a nivel de sistema, controlador de dispositivo y ranuras. Si insertamos una tarjeta PCI-X en una ranura PCI, el dispositivo queda limitado a las velocidades de PCI. Capacidad de inserción/sustitución en caliente: Hot-plug Revisión 1.0: PCI-X 66: 64 Bits @ 66 MHz, PCI-X 133: 64 Bits @ 133 MHz, Revisión 2.0 PCI-X 266: Utiliza doble transferencia de datos (Double Data Rate), por lo que la frecuencia efectiva es de 266 MT/s PCI-X 533: Cuádruple transferencia de datos (Quad Data Rate), por lo que la frecuencia efectiva es de 533 MT/s. Figura 19: Ejemplo de arquitectura basada en PCI-X. Tema 4: Placa base versión 7.0 17/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Figura 20: Ejemplo de arquitectura basada en PCI-X. Todas estas mejoras tienen un coste, pues al aumentar el número de patillas-pistas y la frecuencia se elevan las exigencias de diseño PCB. 4.2.2.9.- PCI Hot-Plug Figura 21: Obsérvese en la figura la arquitectura hardware y software de un sistema PCI Hot Plug Permite la inserción/sustitución en caliente de tarjetas en el bus PCI, eliminando los tiempos muertos tan importantes en servidores (i.e. disponibilidad). La especificación PCI hot-plug en su revisión 1.0, define interfaces software y hardware para tarjetas PCI, pero no define como deben ser implementados por los fabricantes. Permite la coexistencia con tarjetas PCI que no soporten Hot-Plug. Cuando falle una tarjeta, se desactiva su ranura PCI, se sustituiye dicha tarjeta y se vuelve a activar. Tema 4: Placa base versión 7.0 18/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Elementos implicados Placa base: El controlador PCI debe soportar Hot-plug para controlar individualmente las señales de cada ranura PCI. Modificaciones para evitar riesgos eléctricos en las ranuras PCI activas. Facilidad para el acceso a las ranuras. Tarjetas y driver del dispositivo: Lógicamente las tarjetas y sus drivers deben estar diseñados para soportar esta tecnología. Sistema operativo: Cada sist. op. debe definir capas de interfaz entre el hardware y el núcleo del sistema operativo. Por ejemplo, un servidor PC con tecnología PCI hot-plug puede utilizar dos tarjetas de red, una de ellas redundante. Al fallar la tarjeta principal, la de reserva se activará automáticamente. Puede reemplazarse la tarjeta averiada sin necesidad de apagar el sistema, eliminándose los tiempos muertos. Versiones La especificación, según las características que se implementen, contempla varios tipos de hot-plug: Hot plug PCI replacement: Sustituir un dispositivo que falla por otro idéntico. Hot plug PCI upgrade: Sustituir dispositivos y controladores por nuevas versiones. Hot plug PCI Expansion: Instalar tarjetas adicionales y drivers. Ejemplo: El servidor Intel® Server Platform SR4850HW4 describe entre sus características 7 ranuras PCI: • 1 PCI Express* x8 (hot-plug) • 3 PCI Express x4 (hot-plug) • 1 PCI-X 133MHz (hot-plug) • 2 PCI-X 100MHz (non-hot-plug) Ejemplo: sistema con 2 puentes PCI-X y ranuras Hot-plug Figura 22: Ejemplo de sistema PCI-X Hot-plug Fuente: Preliminary AMD-8131TM HyperTransportTM PCI-X Tunnel Data Sheet Tema 4: Placa base versión 7.0 19/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos 4.2.3.- PCI EXPRESS Las revisiones del bus PCI (PCI 2.3, PCI-X) aumentan el rendimiento a costa de elevar el número de señales y las restricciones en cuanto a la integridad de señal lo que eleva los costes (patillas, pistas, zócalos). Por todo ello se ha ido fraguando una tecnología sustitutiva basada en la transmisión diferencial en serie: PCI Express. 4.2.3.1.- Características de transmisión Transmisión diferencial Al igual que otros buses del ordenador que han evolucionado a la transmisión serie (USB, Serial ATA) utiliza la técnica LVDS (Low Voltage Differential Signaling). Transmisión síncrona La señal de reloj está mezclada con la propia información. Para ello, usa una codificación 8b/10b que transmiste 10 bits por cada 8 de información, por lo que genera una sobrecarga del 20 %. Figura 23: Codificación 8b/10b usada en las versions 1.0 y 2.0 de PCI Express Transmisión bidireccional Un enlace (link) elemental está compuesta de 1 vía (lane), dos hilos de ida y dos de vuelta que transmiten simultáneamente (conexión full-duplex). Figura 24: Enlace simple (x1) de PCI Express Tema 4: Placa base versión 7.0 20/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Enlace múltiple PCI Express puede utilizar varias vías (lanes) para el mismo enlace (link) dando lugar a configuraciones llamadas x1, x2, x4, x8, x12, x16, x32. Las conexiones x16 y x32 permiten conectar dispositivos que requieren grandes velocidades de transmisión como tarjetas gráficas. Figura 25: Codificación 8b/10b usada en las versions 1.0 y 2.0 de PCI Express Se pueden establecer múltiples canales virtuales en un enlace múltiple. Cada vía puede transmitir hasta 2’5 Gbit/s (5 Gbits/s en la versión 2.0 y 8 Gbits/s en la 3.0). Figura 26: Ranuras de conexión para los distintos tipos de conexiones PCIExpress Ejemplo: Velocidad de transferencia de una conexión PCI Express 2.0 x32 En una dirección se puede tranmistir: 5 Gbit/s x 32 vías x 2 sentidos = 320 Gbit/s = 40 GByte/s Si contamos la transferencia en un único sentido: 160 Gbit/s = 20 GByte/s Propuesto 4.8: ¿Cuál será la velocidad de transferencia de datos teniendo en cuenta la sobrecarga que se produce al añadir la señal de reloj? Ejemplo: ATI Radeon Xpress 200P North Bridge features 22 PCI Express lanes. Two of them are assigned for the connection with the South Bridge, four of them are responsible for PCI Express x1 slots. As a result there are 16 lanes left for the graphics interface, which can be used either by a single PCI Express x16 graphics bus or by two PCI Express x8 graphics buses simultaneously. www.xbitlabs.com Tema 4: Placa base versión 7.0 21/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Para la transmisión, la información se divide en bytes que se reparten por las vías disponibles: Figura 27: Un enlace (link) está compuesto de varias vías (lane). Los bytes se reparten entre las vías disponibles PROPUESTO 4.9: ¿Cuánto se tardará en transmitir esos 8 bytes? Transmisión isócrona Es posible reservar y garantizar un ancho de banda bajo demanda consiguiendo una transmisión en tiempo real. A esto se le conoce como transferencia isócrona, pues se puede garantizar el tiempo que durará una transmisión de datos (i.e. tiempo real). Esto es útil, por ejemplo, en la transmisión de vídeo en tiempo real (sin cortes). Figura 28: La edición de vídeo, por sus altos requerimientos de ancho de banda, es una tarea que se ve favorecida por las características del bus PCI Express. Distancia La inclusión de la señal de reloj permite mayores distancias respecto a los buses paralelo cuya señal discurre por una línea separada. En el diseño de este bus se ha marcado como objetivo permitir hasta 50 cm de distancia entre dispositivos con tecnología de placa de circuito impreso de 4 capas y conectores estándard. Se podría aumentar la distancia usando componentes de mayor calidad. Tema 4: Placa base versión 7.0 22/27 Ignacio Moreno Velasco 4.2.3.2.- Apuntes Mantenimiento de Equipos Informáticos Evolución del PCI Express Mientras versión 3.0 dobla la tasa de transferencia teórica respecto a la 2.0, la próxima versión 4.0 hace lo propio con la versión 3.0 alcanzando las 16 GT/s. Características PCI Express® 3.0: Dobla el tasa de transmisión respecto a PCIe 2.0 Data rate: 8 GT/s Optimiza consumo respecto a PCIe 2.0 Codificación 128b/130b Esta codificación permite que 8 GT/s ≈ 8 Gb/s Compatible con PCIe 1.x y 2.x 4.2.3.3.- Mantenimiento Conector Figura 29: Descripción de los contactos del conector PCI-Expres x1 www.overclockers.com.au Observar la presencia del SMBus, y de los contactos para Hotplug Consumo energético Bajo consumo debido a las bajas tensiones de funcionamiento. (recordar que utiliza LVDS) Implementa funciones de ahorro de energía, incluyendo una línea WAKE#. Tema 4: Placa base versión 7.0 23/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Ahorro de costes La transmisión serie ahorra muchas líneas y por tanto ahorra también: Patillas en los circuitos integrados Pistas en las placas de circuito impreso, Hilos en los cables permitiendo conectores más pequeños. Conexión sustitución Conexión en caliente (hot-plug) Cambio en caliente (hot-swap) Integridad de la señal Al disminuir el nº de pistas, facilita tomar medidas contra las interferencias electromagnéticas (EMI): La conexión serie tiene menos problemas con la propagación por la diferencia de longitud de las pistas. La señal diferencial disminuye los problemas con el ruido eléctrico. Figura 30: Como puede observarse en la imagen, las pistas que discurren en paralelo tienen distinta longitud en cuanto cambian de dirección. Errores Figura 31: El nivel de enlace añade la información CRC para asegurar la integridad de los datos. Intel. Toda esa información que se añade a los datos supone una sobrecarga, que añadida a la codificación 8b/10b o 128b/130b, reduce aún más la velocidad de transferencia de datos. Compatibilidad con PCI Aunque la incompatibilidad hardware es evidente, se mantiene una compatibilidad con PCI en las capas software: Compatibilidad con el mecanismo de configuración del bus (bus enumeration) y los dispositivos: Evita problemas con las rutinas de configuración PCI/PnP del BIOS y su espacio de configuración ESCD. Permite abaratar los costes en la implementación de los controladores de dispositivo (drivers) Tema 4: Placa base versión 7.0 24/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Figura 32: Capas definidas en la arquitectura PCI Express. Intel. Interrupciones Hardware El método nativo para las interrupciones hardware es mediante Mensajes (MSI = Message Signaled Interrupt). Ya no se trata de activar una patilla o señal del bus, sino de realizar una escritura en una zona reservada al efecto en la RAM. Por compatibilidad con el modelo PCI, se emula el método tradicional de PCI las INTA# …INTD# permitiendo que lo usen los drivers PCI (i.e. Sist. Op.). Para ello se encapsula la información de las interrupciones INTx dentro de una transacción de mensajes de PCI-Express Figura 33: Coexistencia de los métodos de solicitud de interrupción. www.oohoo.org Tema 4: Placa base versión 7.0 25/27 Ignacio Moreno Velasco 4.2.3.4.- Apuntes Mantenimiento de Equipos Informáticos Topología de sistemas PCI-Express Basada en conmutación (switching) que permite establecer canales virtuales de comunicación. Figura 34: Ejemplo de topología de placa base con PCI Express. Observar que en el sitio ocupado anteriormente por el puente sur se halla ahora un switch. Actualmente, este switch está integrado en el puente sur. Intel. En la Figura 35, podemos observar en detalle el switch de la Figura 34. Se observa como la compatibilidad con PCI se consigue gracias a que el sistema “ve” puentes PCI-PCI, de ahí que se les adjetive como virtuales: Figura 35: Diagrama de bloques de un switch PCI Express. Intel. Tema 4: Placa base versión 7.0 26/27 Ignacio Moreno Velasco Apuntes Mantenimiento de Equipos Informáticos Ejemplos de aplicación: Figura 36: Imagen de placa base donde puede observarse en primer término dos ranuras PCI. Tras ellas dos PCI-Express x1 y una PCI-Express x16 Figura 37: Chipset con la estructura habitual de puente norte (MCH) y puente sur (ICH) basado en arquitectura PCI Express. Intel Figura 38: Chipset de un solo circuito integrado. El Root coomplex se encuentra en el propio micro. Intel. Tema 4: Placa base versión 7.0 27/27

![Descargar - [ [ [ ANSEL ] ] ]](http://s2.studylib.es/store/data/005807843_1-39498269826d9ab30dac33202061ffe6-300x300.png)