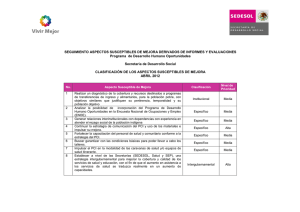

doc general

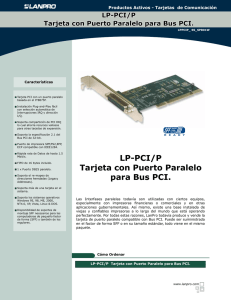

Anuncio