Control 1 - U

Anuncio

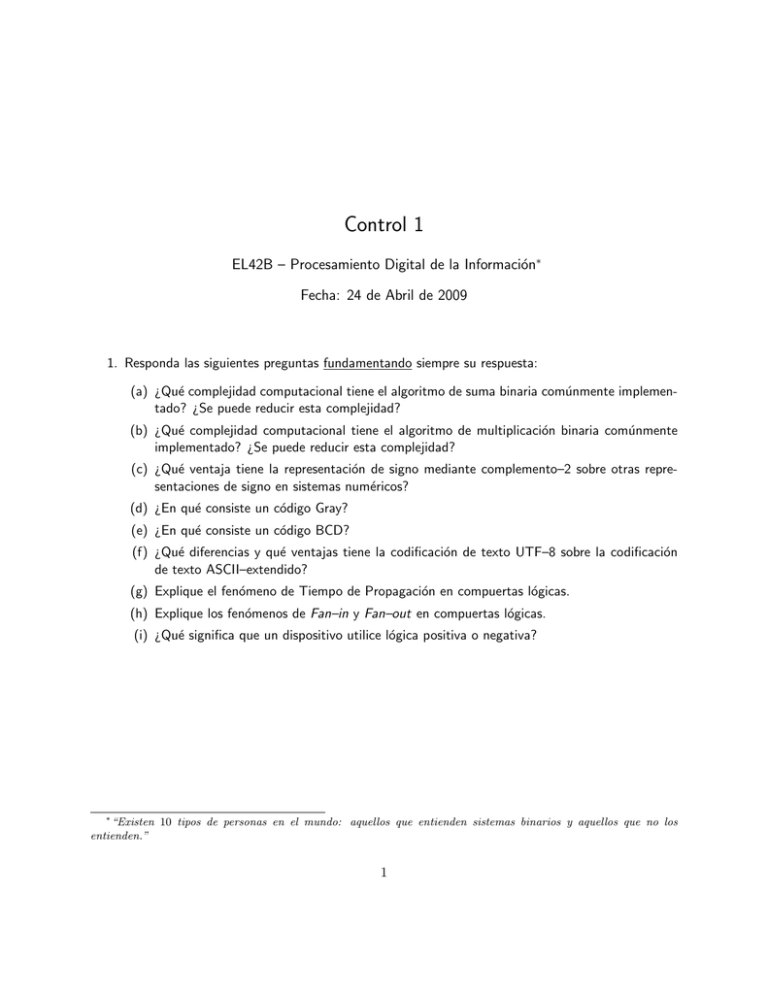

Control 1 EL42B – Procesamiento Digital de la Información∗ Fecha: 24 de Abril de 2009 1. Responda las siguientes preguntas fundamentando siempre su respuesta: (a) ¿Qué complejidad computacional tiene el algoritmo de suma binaria comúnmente implementado? ¿Se puede reducir esta complejidad? (b) ¿Qué complejidad computacional tiene el algoritmo de multiplicación binaria comúnmente implementado? ¿Se puede reducir esta complejidad? (c) ¿Qué ventaja tiene la representación de signo mediante complemento–2 sobre otras representaciones de signo en sistemas numéricos? (d) ¿En qué consiste un código Gray? (e) ¿En qué consiste un código BCD? (f) ¿Qué diferencias y qué ventajas tiene la codificación de texto UTF–8 sobre la codificación de texto ASCII–extendido? (g) Explique el fenómeno de Tiempo de Propagación en compuertas lógicas. (h) Explique los fenómenos de Fan–in y Fan–out en compuertas lógicas. (i) ¿Qué significa que un dispositivo utilice lógica positiva o negativa? ∗ “Existen 10 tipos de personas en el mundo: aquellos que entienden sistemas binarios y aquellos que no los entienden.” 1 2. Simplifique todo lo que sea posible la función f (a, b, c) representada en la figura y dibuje el circuito lógico simplificado utilizando el mı́nimo de compuertas lógicas. Haga referencia a los postulados y/o teoremas de la tabla adjunta. Recuerde que x ⊕ y = xȳ + x̄y. a b b c f ā b̄ a c 2 3. Se quiere diseñar un circuito lógico con tres bits de entrada: A2 , A1 y A0 . La entrada representa un número entero con signo en representación complemento–2: A = (A2 A1 A0 )2c . El circuito debe tener cuatro bits de salida: B2 , B1 , B0 y E. Las tres primeras salidas representan un número entero con signo en representación complemento–2, B = (B2 B1 B0 )2c , que es el resultado de restar (2)10 a la entrada, es decir, B = A − (2)10 . El bit de salida E indica si existe un overflow en esta operación. Es decir, E es es igual a 1 si existe un overflow y 0 si no existe. Para el diseño del circuito considere que si E = 1 el usuario descartará completamente el resultado en B. (a) Escriba la tabla de verdad con todas las posibles entradas y salidas del circuito lógico. (b) Escriba cada una de las funciones de salida en forma canónica SOP. Utilice notación compacta haciendo referencia al número de los minitérminos. (c) Simplifique todo lo que sea posible cada una de las funciones de salida haciendo referencia a los postulados y/o teoremas de la tabla adjunta. 3 Postulados y Teoremas de Álgebra Booleana: Expresión Dual P2: a+0=a P2(D): a·1=a P3: a+b=b+a P3(D): ab = ba P4: a + (b + c) = (a + b) + c P4(D): a(bc) = (ab)c P5: a + bc = (a + b)(a + c) P5(D): a(b + c) = ab + ac P6: a + ā = 1 P6(D): a · ā = 0 T1: a+a=a T1(D): a·a=a T2: a+1=1 T2(D): a·0=0 T3: ¯=a ā T4: a + ab = a T4(D): a(a + b) = a T5: a + āb = a + b T5(D): a(ā + b) = ab T6: ab + ab̄ = a T6(D): (a + b)(a + b̄) = a T7: ab + ab̄c = ab + ac T7(D): (a + b)(a + b̄ + c) = (a + b)(a + c) T8: a + b = ā · b̄ T8(D): a · b = ā + b̄ T9: ab + āc + bc = ab + āc T9(D): (a + b)(ā + c)(b + c) = (a + b)(ā + c) f (x1 , x2 , . . . , xn ) = x1 · f (1, x2 , . . . , xn ) + x̄1 · f (0, x2 , . . . , xn ) T10(D): f (x1 , x2 , . . . , xn ) = x1 + f (0, x2 , . . . , xn ) · x̄1 + f (1, x2 , . . . , xn ) T10: 4