- Ninguna Categoria

Universal Serial Bus:

Anuncio

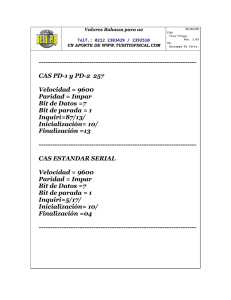

Universal Serial Bus: Elementos de un Controlador USB La complejidad del protocolo USB implica que un periférico USB debe tener inteligencia. Todos los dispositivos USB tienen un controlador que se encarga de atender los eventos que se producen en el port USB, y mantenga en áreas de memoria los datos correspondientes a las transacciones en curso. Una importante decisión al diseñar un dispositivo USB es la selección del controlador apropiado. Universal Serial Bus: Criterios de Diseño de Dispositivos La variedad de chips existentes en el mercado permiten plantear tres alternativas para la resolución de un proyecto: Tipo de µControlador Control del USB Eléctrica firmware cualquiera Diseñada de acuerdo a la especificación eléctrica del USB manejar todo el control del Bus cualquiera Controlador USB conectado como un periférico con Controlador USB embebido Controlador USB embebido como un periférico Diseño Global Flexibilidad al cambiar de proyecto Altísima complejidad Máxima en la libre elección de CPU Mínima complejidad Máxima en la libre elección de CPU Se mantiene know how sobre el Controlador USB Mínima complejidad Se cambia de CPU y de Controlador USB Universal Serial Bus: Casos Prácticos Intel: Fue el primero. Presentó un microcontrolador de la familia MCS 51 con un controlador USB embebido: el 80251. Posteriormente junto con Cypress desarrolló el 8x930 (basado en el 8051 básico) y el 8x931 como evolución del 80251. Cypress: Hasta su sociedad con Intel desarrolló la línea de microcontroladores con USB embebido CY7C63xxx. En algunos puntos mas fuertes que los de Intel. Pero el valor de la compatibilidad con la conocida MCS51 los hizo migrar a la línea 8x93x. Finalmente desarrollaron el EZ-USB que une lo mejor de los dos mundos. La potencia de los CY7C63xxx y la compatibilidad con el 8051 básico. Universal Serial Bus: Casos Prácticos Controladores Genéricos: Se trata de Transceivers genéricos que interfacean con cualquier microprocesador. Ofrecen mas flexibilidad en el diseño de diferentes soluciones. Opciones: National USBN9603 Lucent USS820/825 NetChip Net2888 Philips PDIUSBD11 PDIUSBD12 Fairchild USB1T11A Universal Serial Bus: USBN9603 Diagrama en Bloques •Formateo de paquetes •Generación y Chequeo de CRC •Detección de Direccionamiento de Endpoints •Controla la devolución de NACK, ACK o Stall •Circuito de clock Recovery •Detector de glitch •Circuitería de detección de EOP •Lógica de Bit Stuffing •Utiliza el código NRZI entrante para extraer el clock de 12 MHz del frame entrante. Trabaja con un clock de 48 Mhz. derivado de un cristal de 24 Mhz que alimenta al chip, y un PLL doblador •Cumple con el capítulo 7 de la especificación USB 1.1. •Contiene un Receptor con entrada diferencial, un receptor con terminación simple y regulador interno, y u transmisor con fuente de corriente propia •Le provee 3.3 V al Transceptor. •Se puede utilizar para suministrar alimentación al resistor de pull up de 1,5 KΩ Universal Serial Bus: USBN9603 Endpoint Pipe Controller Universal Serial Bus: USBN9603 Interfaz con el Microprocesador Modo No Multiplexado Universal Serial Bus: USBN9603 Interfaz con el Microprocesador Modo Multiplexado Universal Serial Bus: USBN9603 Interfaz con el Microprocesador Modo Microwire/PLUS Universal Serial Bus: USBN9603 Operación de los Endpoints I Cada Endpoint tiene asociada una memoria RAM FIFO. La memoria RAM FIFO asociada al Endpoint 0 bidireccional es de 8 bytes. Luego cada uno de los seis Endpoints unidireccionales restantes tiene una memoria de 64 bytes. Universal Serial Bus: USBN9603 Operación de los Endpoints II Operación de RAM FIFO de Transmisión TFxS: Tamaño total en bytes de la memoria FIFO. TXRP: Puntero de Lectura para Transmisión. Se incrementa cada vez que el Endpoint Controller lee la memoria FIFO durante la transmisión al BUS. TXWP: Puntero de Escritura para Transmisión. Se incrementa cada vez que el Firmware escribe en la memoria FIFO un dato para ser transmitido. TXFL: Indica cuantos bytes tiene actualmente almacenados la memoria FIFO TCOUNT: Accesible por el Firmware en el registro TxSx, este valor indica cuantos bytes serán escritos en la memoria FIFO de Transmisión. Universal Serial Bus: USBN9603 Operación de los Endpoints III Operación de RAM FIFO de Recepción RFxS: Tamaño total en bytes de la memoria FIFO. RXWP: Puntero de Escritura por Recepción. Se incrementa cada vez que el Endpoint Controller escribe la memoria FIFO por recepción de un dato desde el BUS. RXRP: Puntero de Lectura para Recepción. Se incrementa cada vez que el Firmware lee desde la memoria FIFO un dato. RXFL: Indica cuantos bytes pueden ser recibidos y almacenados la memoria FIFO antes de tener Overrun RCOUNT: Accesible por el Firmware en el registro RXSx, este valor indica cuantos bytes serán leídos desde la memoria FIFO de Recepción. Universal Serial Bus: USBN9603 Modelo de Programación I Jerarquía de Registros para reporte de Eventos Universal Serial Bus: USBN9603 Modelo de Programación II Consideraciones Generales en la descripción de los registros. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control I Main Control Register (MCNTRL): SRST: Software Reset. Si es ‘1’ se resetea el controlador. Es idéntico al Reset por Hardware excepto que no se altera el registro CCONF. VGE: Voltage Generator Enable: Si es ‘1’ se habilita el generador interno de 3,3 V. NAT: Node Attached: Si es ‘1’ indica que el nodo está listo para ser detectado como attachado al USB. INTOC: Interrupt Output Control: Controla la salida de Interrupción a un procesador 00: Deshabilitado. 01 Activa baja open drain. 10:Activa alta push pull. 11 Activa baja push pull. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control II Clock Configuration Register (CCONF): CLKDIV: Divisor del Clock Externo. Luego de un reset divide por 11 lo que significa que emite una señal de 4 MHz. por el pin CLKOUT. CODIS: Clock Output Disable. Si vale ‘1’ se deshabilita la salida de clock mencionada en el punto anterior. CLKOUT permanecerá inactivo hasta que se limpie este bit. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control III Revision Identifier (RID): REVID: Indicador de revisión. Para esta revisión el 9603 contiene en este campo 0010b. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control IV Node Functional State Register (NFSR): NFS: El firmware irá efectuando transiciones de estado según los valores de los bits de Estados del Alternate Event Register (ALTEV). De acuerdo a eso escribirá en estos bits el estado en que se encuentra el nodo funcional. NFS 1 0 Estado del Nodo Descripción 0 0 NodeReset Se recibió un Reset por HW, Sw, o por el BUS. Todos los Endpoints deshabilitados. 0 1 NodeResume 1 0 Se generó señalización “K”. El Firmware setea este modo para efectuar un Wake Up remoto.Dura de 1 a 15 mseg. NodeOperational Este es el estado Normal de operación. 1 1 NodeSuspend Si el Firmware detecta un evento de Suspensión, setea este estado. Los transceivers operan en modo de bajo consumo. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control V Main Event Register (MAEV): WARN: Se ha seteado uno de los bits en el registro FWEV (FIFO Warning Event). Volverá a ’0’ cuando se lee FWEV. ALT: Se ha seteado uno de los bites del registro ALTEV. Se limpiará cuando se lea ALTEV. TX_EV: Se ha seteado alguno de los bits del Registro TXEV (TXFIFOx o TXUNDERNx). Indica que se ha completado una transacción IN. FRAME: Se setea cada vez que el Frame Counter se actualiza con un nuevo valor. Puede indicar la recepción de un paquete SOF en el USB. NAK: Negative Acknowledge se ha producido y uno de los bits del registro NAKEV indica en que Endpoint. Se limpia cuando se lee NAKEV. ULD: El timer de frames pasó de una condición Locked a una condición Unlocked. Esta situación se indica con el bit UL seteado en el Fram Numbre Register. Se limpia al leer dicho registro. RX_EV: Se ha seteado algúno de los bits del Registro RXEV. Esto indica que se ha completado una transacción OUT o SETUP. Se limpia cuando se limpian los bits RX_LAST en el registro RXSx y los bits RXOVRRN en el registro RXEV. INTR: Master Interrupt Enable.Este bit se cablea a 0 en este registro. El correspondiente bit en el Main Mask Register (MAMSK) es el Master Interrupt Enable. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control VI Main Mask Register (MAMSK): Con un 1se habilita la generación de interrupción al microprocesador cuando el bit correspondiente del registro MAEV se activa. De lo contrario la generación de interrupción de esa fuente permanece deshabilitada. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control VII Alternate Event Register (ALTEV): WKUP: Este bit se pone en ‘1’ cuando se envía una interrupción por el pin INTR. Este bit es Read Only y se limpia cuando se pone a cero el bit correspondiente (PNDUC o PNDUSB en el Wake Up Register. DMA: DEMA Event. Indica que alguno de los bits del DMA Event Register (DAMEV) se ha seteado. Se limpia cuando se resetea el bit del DMAEV. EOP: Indica la detección de una secuencia EOP en el USB. Se limpia con la operación de lectura SD3 y SD5: Se setean cuando se detectan que un port Upstream lleva 3 y 5 mseg. respectivamente en estado Idle. SD3 indica que el dispositivo debe ser suspendido. SD5 indica que el dispositivo puede comenzar una operación de Wake Up remota si se le solicita. Se limpia con la lectura. RESET: Se setea cuando se detecta una condición de reset. Se limpia con la lectura RESUME: Se enciende si el dispositivo está en estado Idle y recibe señalización en el USB. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control IX Transmit Event Register (TXEV): TXFIFO Transmit FIFO. Son copia de los bits TX_DONE de los Transmit Status Register (TXSx) correspondientes. Se setean cuando se completa una transacción IN en el correspondiente Endpoint de transmisión. Se limpian cuando se lee el correspondiente TXSx Register. TXUDRRN Transmit Underrun. Son copia de los respectivos bits TX_URUN de los correspondientes TXSx registers. Cada vez que cualquiera de los Transmit FIFOs se vacía, se setea el respectivo bit TXUDRRN. Estos bits se limpian en el momento en que se lee el Transmit Status Register. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control X Transmit Mask Register (TXMSK): Cada bit trabaja como máscara del correspondiente bit TXEV del Transmition Event Register. Si la máscara está en 1, cada vez que se active un bit en el registro TXEV, dicha activación se translada al bit TX_EV en el registro MAEV. Cuando la máscara esté inactiva (bit en cero) el bit TX_EV del Registro MAEV no sigue las variaciones de los bits del registro TXEV. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control XI Receive Event Register (RXEV): RXFIFO. Receive FIFO. Se setean en respuesta a un set en los bits RX_ERR o RX_LAST del respectivo Receive Status (RXSx) Register. AL leerse el correspondiente RXSx Register estos bits se limpian automáticamente. El USBN9603 descarta todos los packets para su Endpoint 0 que reciba con errores, a fin de asegurar que se ha capturado una copia válida del paquete SETUP, en el caso de retransmisiones por errores en el medio de transmisión. De otro modo la FIFO puede quedar enganchada manteniendo datos corruptos, y quedar inhibida para retransmitir el mismo paquete (El bit RXFIFO0 no solo refleja el valor del RX_LAST para el Endpoint 0). Si se usa data streaming para los endpoints de recepción (EP2, EP4 y EP6) el firmware debe chequear el bit RX_ERR respectivo para asegurar que los paquetes recibidos no están corruptos por errores. RXOVRRN Receive Overrun. Se setean con el evento de un FIFO overrun. Se limpian cuando se limpia el registro. El firmware debe chequear el bit RX_ERR respectivo al recibir paquetes en los otros Endpoints de Recepción(EP2, EP4 y EP6) que no estén corruptos por errores, mas cuando esos endpoints soportan data streaming (paquetes que son mayores que el tamaño de la FIFO). Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control XII Receive Mask Register (RXMSK): Cada bit trabaja como máscara del correspondiente bit RXEV del Transmition Event Register. Si la máscara está en 1, cada vez que se active un bit en el registro RXEV, dicha activación se translada al bit RX_EV en el registro MAEV. Cuando la máscara esté inactiva (bit en cero) el bit RX_EV del Registro MAEV no sigue las variaciones de los bits del registro RXEV. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control XIII Nack Event Register (NAKEV): IN Vale 1 cuando se genera un handshake NAK para una combinación address/endpoint habilitada (se pone en uno el bit AD_EN en el Function Address Register (FAR) y el EP_EN en el Endpoint Control Register (EPCx ) en respuesta a un token IN. Se limpia cuando el registro es leído. OUT Vale 1 cuando se genera un handshake NAK para una combinación address/endpoint habilitada (se pone en uno el bit AD_EN en el Function Address Register (FAR) y el EP_EN en el Endpoint Control Register (EPCx ) en respuesta a un token OUT. Este bit no se setea si NACK se genera a causa de una condición de overrun. Se limpia cuando el registro es leído. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Control XIV Nack Mask Register (NAKMSK): Cada bit trabaja como máscara del correspondiente bit del NAKEV Register. Si la máscara está en 1, cada vez que se active un bit en el registro NAKEV, dicha activación se translada al bit NAK en el registro MAEV. Cuando la máscara esté inactiva (bit en cero) el bit NAK del Registro MAEV no sigue las variaciones de los bits del registro NAKEV. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia I FIFO Warning Event Register (FWEV): TXWARN Transmit Warning. Vale 1 cuando la respectiva FIFO del Endpoint de transmisión alcanza su límite de warning, según se especifica en los bits TFWL del Registro TXCx respectivo, y está habilitada la transmisión desde el Endpoint respectivo . Se limpia junto con la condición de warning al escribir datos en la FIFO cuando esta está flusheada, o cuando la transmisión está finalizada, como se refleja en el bit TX_DONE bit en el TXSx Register. RXWARN Receive Warning. Vale 1 cuando la respectiva FIFO del Endpoint de transmisión alcanza su límite de warning, según se especifica en los bits RFWL del Registro EPCx respectivo. Se limpia junto con la condición de warning al leer datos en la FIFO o cuando ésta está flusheada. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia II FIFO Warning Mask Register (FWMSK): Cada bit trabaja como máscara del correspondiente bit del FWEV Register. Si la máscara está en 1, cada vez que se active un bit en el registro FWEV, dicha activación se traslada al bit WARN en el registro MAEV. Cuando la máscara esté inactiva (bit en cero) el bit WARN del Registro MAEV no sigue las variaciones de los bits del registro NAKEV. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia III Frame Number High Byte Register (FNH): Parte I FN Frame Number. Es el número de frame recibido en el último paquete SOF. Si no se recibe un número de frame válido dentro de un tiempo de 12060 bits del cambio previo(denominado Frame Length Maximum, FLMAX, con tolerancia), el número de frame se incrementa artificialmente. Si dos frames sucesivos se pierden o resultan incorrectos, el FN actual se congela y se carga el siguiente número de frame desde un paquete SOF válido. Si el byte bajo del número de frame es leído por el firmware antes de leer el registro FNH, el valor leído corresponde a un buffer del registro que mantiene el valor de los tres bits mas significativos del número de frame válidos al momento de la lectura del registro. Por lo tanto la secuencia correcta para leer el número de frame es FNL, FNH. Las lecturas de FNH que no hayan sido precedidas por lecturas del registro FNL leen el valor actual de los tres bits mas significativos del número de frame. Luego de un reset, FN vale 0. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia III Frame Number High Byte Register (FNH): Parte II RFC Reset Frame Count. AL setear este bit se resetea el número de frame (=x000), y a continuación este bit se resetea por si mismo. Si lo leemos el resultado siempre es 0. UL Unlock Flag. Este bit indica que se han recibido al menos dos frames sin el número de frame esperado, o que no se ha recibido un SOF válido dentro de 12060 tiempos de bit. Si este bit está seteado, se carga en FN el número de frame del próximo paquete SOF válido. Luego de un reset este bit vale 1. MF Missed SOF Flag. Este flag se setea cuando el número de frame en un SOF válido recibido, no coincide con el valor esperado, o cuando no se ha recibido un SOF dentro de los 12060 tiempos de bit. Luego de un reset, este flag vale 1. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia IV Frame Number Low Byte Register (FNL): Mantiene el byte bajo del Número de Frame. Para asegurar consistencia, al leer este registro el controlador lockea los tres bits mas significativos del Número de Frame en el Registro FNH hasta que éste sea leído. La secuencia correcta para leer el número de Frame es: FNL, FNH. Luego de un reset, FN vale 0. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia V Function Address Register (FAR): Este registro establece la dirección de función del dispositivo. Los diferentes números de Endpoint se establecen para cada Endpoint individual en su Endpoint Control Register. AD Address. Contiene la dirección de 7 bits de la función utilizada para transmitir y recibir los tokens direccionados al dispositivo. AD_EN Address Enable. Cuando vale 1, los bits AD6-0 se utilizan para la comparación de direcciones. Cusndo está en 0, el dispositivo no responde a ningún token sobre el USB. Nota: Si el bit DEF en el registro Endpoint Control 0 está seteado, el Endpoint 0 responde a la dirección default (Address 0). Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia VI DMA Control Register (DMACNTRL): Parte I DSRC DMA Source. El campo de bits DMA source contiene el valor codificado en binario que especifica cuales de los Endpoints 1 a 6 tienen habilitado soporte DMA. Estos bits valen 0 luego de un reset. La Tabla que tenemos a la derecha presenta los valores posibles del campo de bits DSRC. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia VI DMA Control Register (DMACNTRL): Parte II DMOD DMA Mode. Este bit especifica cuando se ha enviado un requerimiento DMA. Si está en ‘0’, se envía un requerimiento DMA al completarse una transferencia. Para los Endpoints de transmisión EP1, EP3 y EP5, el dato se transfiere completamente y se setea el bit TX_DONE (para llenar la FIFO con nuevos datos a transmitir). Para los Endpoints de recepción EP2, EP4 y EP6, se indica mediante el bit RX_LAST. Cuando el bit DMOD está en ‘1’, se envía un requerimiento DMA para advertir que el respectivo bit está seteado. El bit DMOD está en ‘0’ luego de un reset Un requerimiento DMA desde un Endpoint de transmisión se activa cuando se limpia la condición del requerimiento. Si DMOD está a 0, se envían los requerimientos DMA una vez que le firmware lee el registro Transmit Status (TXSx) respectivo, reseteando de este modo el bit TX_DONE, o si el bit TX_LAST del registro Transmit Command (TXCx) se setea por firmware. Si DMOD está a ‘1’, se envía un requerimiento de DMA cuando se limpia la condición de la FIFO, debido a que ya se han transferido la cantidad suficiente de bytes al Endpoint, o si el bit TX_DONE está seteado debido a una transmisión. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia VI DMA Control Register (DMACNTRL): Parte III DMOD (continuación) Los requerimientos de DMA desde un Endpoint de recepción se activan cuando la condición del requerimiento se limpia. Si DMOD está a ‘0’, se envían requerimientos de DMA una vez que el firmware lea el registro Receive Status (RXSx) respectivo, reseteando de este modo el bit RX_LAST, o si la FIFO del Endpoint se vacía lo suficiente debido a las lecturas sucesivas. Si DMOD vale ‘1’, Los requerimientos de DMA se envían una vez que la condición de warning de la FIFO se limpie, o si la FIFO del Endpoint se vacía lo suficiente debido a las lecturas sucesivas. Si DMOD vale ‘0’ y el Endpoint y el DMA están habilitados, se envían requerimientos de DMA una vez que el firmware lee los registros TXSx or RXSx respectivos, reseteando de este modo el bit TX_DONE/RX_LAST. Si DMOD vale ‘1’ y el Endpoint y el DMA están habilitados, se enviarán requerimientos de DMA cada vez que se limpie la condición de la FIFO. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia VI DMA Control Register (DMACNTRL): Parte IV ADMA Automatic DMA. Al setear este bit se habilita el Endpoint seleccionado para recibir o transmitir. Antes que se haya habilitado el modo ADMA, debe estar en ‘0’ el bit DEN en el registro DMA Control (DMACNTRL). El Modo ADMA funciona hasta que se setee cualquier bit en el registro DMA Event (DMAEV), excepto para NTGL. Para iniciar el modo ADMA, deben estar en ‘0’ todos los bits del registro DMAEV, excepto NTGL. Para operaciones de recepción, se habilita automáticamente el receptor; y cuando se recibe el paquete se lo transfiere vía DMA a la memoria. Para operaciones de transmisión, el paquete de datos se transfiere desde memoria vía DMA; luego el transmisor se habilita automáticamente. Para operaciones ADMA, se ignora el bit DMOD. Todas las operaciones tienen lugar como si el bit DMOD estuviese en ‘0’. Cuando un dispositivo entra al modo ADMA, puede perderse el estado existente en cualquiera de los endpoints. Si aún hay datos en la FIFO, se flushean. También puede cambiar el estado existente de RX_EN o TX_EN. Limpiando ADMA se sale del modo ADMA. Puede limpiarse DEN en ese momento o a posteriori. Si se lo hace al mismo tiempo, todas las operaciones de DMA se cancelarán de inmediato y el firmware deberá transferir cualquier dato remanente. Si se lo hace a posteriori, el USBN9603 completará cualquier transferencia DMA antes de abandonar el modo ADMA (ver la descripción del bit DSHLT en el registro DMAEV). Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia VI DMA Control Register (DMACNTRL): Parte IV DTGL DMA Toggle. Este bit se usa para determinar el estado inicial de las operaciones ADMA. El Firmware setea inicialmente este bit a 1 si comenzará con una operación DATA1, y a 0 si comenzará con una operación DATA0. Las escritura en este bits también actualizan el bit NTGL en el registro DMAEV. IGNRXTGL Ignore RX Toggle. Si se setea este bit, no se efectúa la comparación entre los bits NTGL del registro DMAEV y TOGGLE de los respectivos registros RXSx durante las operaciones de recepción. En este caso, no se detendrá la operación de ADMA aunque no se correspondan los estados de estos bits durante una recepción. Si este bit vale ‘0’, se detendrá el ADMA cuando no se correspondan los estados de estos bits. Luego de un reset este bit vale ‘0’. DEN DMA Enable. Este bit habilita el modo DMA cuando se lo pone en ‘1’. If se resetea este bit y el ciclo de DMA actual se ha completado (o no fue aún enviado) se finaliza la transferencia de DMA. Cuando el USBN9603 opera en el modo de interfaz serie (el pin MODE1 está conectado a Vcc) el modo DMA no puede habilitarse, y setear este bit no tiene efecto. Este bit se limpia luego del reset. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia VII DMA Event Register (DMAEV): Parte I Todos los bits de este registro se usan con el modo ADMA. Los bits 0 a 3 pueden ocasionar una interrupción si no se los limpia, aún si el dispositivo no está configurado en el modo ADMA. Hasta que no estén limpios todos estos bits no puede iniciarse el modo ADM. Inversamente, el modo ADMA finaliza automáticamente cuando se setean todos estos bits. DSHLT DMA Software Halt. Este bit se setea cuando las operaciones de ADMA se haltean por firmware. Este bit se setea solo luego que el motor de DMA completó cualquier operación de limpieza y retornó al estado idle. Las siguientes condiciones aplican en esta condición: • Si el bit ADMA vale ‘0’ (pero DEN permanece seteado), se completa la operación en curso(si la hubiere). Esto significa que cualquier dato presente en la FIFO se transferirá a memoria por DMA (si se estaba recibiendo). El bit DSHLT bit está seteado solo si esto ha ocurrido. Al quedar seteado DEN es necesario limpiarlo mas adelante. Normalmente esto se hace dentro del handler de interrupción de DSHLT. • Si el bit DEN está a ‘0’ (ADMA puede permanecer seteado, o puede ponerse a ‘0’0 al mismo tiempo), finalizan todas las operaciones de DMA y se setea de inmediato el bit DSHLT. Si hay datos en la FIFOs, éstos se retienen, no se transmiten. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia VII DMA Event Register (DMAEV): Parte II DSHLT (Continuación) • Si el firmware intenta leer la FIFO (si se está recibiendo) o escribir en la FIFO (si se está transmitiendo), se cancelan todas las operaciones de DMA y se seta de inmediato el bit DSHLT. La lectura o escritura no puede considerarse exitosa ya que esta operación equivale a corromper la FIFO pudiendose perder algunos datos.. • Si el firmware leer o escribir desdehacia loe registros EPCx, TXCx, RXCx, TXSx, or RXSx correspondientes (cuando DEN y ADMA están seteados en el registro DMACNTRL), se haltean todas las operaciones de DMA e inmediatamente se setea el bit DSHLT. La operación de lectura o escritura no es afectada. DERR DMA Error. Este bit se setea para indicar que un paquete no ha sido recibido o transmitido correctamente. También se setea si el bit TOGGLE del registro RXSx/TXSx no es igual al bit NTGLen el registro DMAEV luego de la recepción/transmisión de un paquete. (Note que esta comparación se efectúa antes de que el bit NTGL cambien de estado debido a una transferencia de paquete). En recepción, DERR es equivalente a RX_ERR. En transmisión, es equivalente a TX_DONE (seteado) y a ACK_STAT (limpio). Si está seteado el bit AEH en el registro DMA Error Count (DMAERR), DERR no se setea hasta que MAERRCNT en el registro DMAERR esté limpio, y se detecte otro error. Los errores se manejan de acuerdo a lo especificado en el registro DMAERR. DCNT Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia VII DMA Event Register (DMAEV): Parte III DCNT DMA Count. Este bit se setea cuando el registro DMA Count (DMACNT) register está a ‘0’ (ver registro DMACNT). DSIZ DMA Size. Este bit es significativo solo para operaciones de DMA de recepción. Indica la recepción de un paquete cuya longitud es menor que la longitud completa de la FIFO. Esto normalmente indica el final de una transferencia multipaquete. NTGL Next Toggle. Este bit determina el estado de toggle state del próximo paquete de datos a enviar (si se está transmitiendo), o el estado de toggle experado del próximo paquete de datos (si se está recibiendo). Este bit se inicializa escribiendo en el bit DTGL del registro DMACNTRL. Luego cambia de estado con cada paquete enviado o recibido sobre el Endpoint actualmente seleccionado por DSRC2-0. Si se escribe DTGL al mismo tiempo en que se está actualizando, la precedencia corresponde a la escritura. Si se está transmitiendo, mientras hay operaciones ADMA en curso, el bit DTGL sobreescribe el correspondiente bit TOGGLE en el registro TXCx. De esta forma el toggle alternativo de datos se produce correctamente sobre el USB. Note que no hay un bit de máscara correspondiente a este evento ya que no se utiliza para generar interrupciones. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia VIII DMA Mask Register (DMAMSK) Cualquier bit de este registro que se setea habilita el seteo automático del bit de DMA en el registro ALTEV cuando ocurre un evento respectivo en el registro DMAEV. De otro modo, está deshabilitado el seteo del bit DMA. Los bits 0 a 3, se describen en el registro DMAEV. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XI Mirror Register (MIR): Es un registro de solo lectura. Ya que su lectura no altera el estado de los registros TXSx or RXSx al que apunta, el firmware puede chequear libremente el estado del canal. STAT Status. Este campo es una réplica de los bits de estado del transmisor o receptor seleccionado por el campo DSRC2-0 del registro DMACNTRL (no se requiere tener el DMA activo o habilitado). Corresponde a TXSx o RXSx, respectivamente. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia X DMA Count Register (DMACNT): Este registro permite especificar la cuenta máxima de operaciones ADMA. DCOUNT DMA Count. Este campo se decrementa al completarse una operación de DMA hasta llegara 0. Entonces se setea el bit DCNT del registro DMA Event, solo cuando se completa con éxito la siguiente operación DMA. Este registro se detiene en cero (no hace underflow). Para operaciones de recepción, esta cuenta se decrementa cuando el paquete se recibe correctamente, y luego se transfiere a memoria vía DMA. Para operaciones de transmisión, esta cuenta se decrementa se transfiere un paquete desde memoria vía DMA, y luego de transmitido con éxito. DCOUNT debe setearse del siguiente modo: DCOUNT = (Nº de paquetes a transferir) – 1. Si una operación de escritura de DMACNT se superpone con un decremento automático por parte de la lógica descripta, la escritura tiene mas precedencia. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XI DMA Error Register (DMAERR): Parte I DMAERRCNT DMA Error Counter. Junto con la función de manejo automático de errores, este contador define el número máximo de errores de bus consecutivos luego de los cuales se detiene el modo ADMA. El Firmware puede asignar al bit 7 del contador un valor preestablecido. Una vez que arranque ADMA, el contador se decrementa a partir de este valor preestablecido cada vez que se detecta un error en el bus. Cada transacción correcta restablece el contador a su valor preestablecido. Cuando el modo ADMA se detiene, también se restablece el contador a su valor preestablecido. Si el contador llega a 0 y se detecta error en otro paquete, se setea el bit DERR del registro DMA Event. Este registro no realiza underrun, es decir una vez que llega a cero, simplemente se detiene. DMAERRCNT se setea del siguiente modo: DMAERRCNT = 3D (Máximo . Nº de intentos de transferencia permitidos) – 1. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XI DMA Error Register (DMAERR): Parte II AEH Automatic Error Handling. Dependiendo del modo de transferencia actual este bit tiene dos osignificados diferentes: * Modo no Isocrono. Se utiliza para transferencias bulk, interrupción y control. Poner AEH en ‘1’ en este modo habilita el manejo automático de paquetes con error de CRC o bit-stuffing. Si este bit es ‘1’ durante operaciones de transmisión, el USBN9603 recarga automáticamente la FIFO y reprograma el paquete del cual el host no retornó ACK. Si este bit es ‘0’ se detiene el manejo de errores. Si este bit es ‘1’ durante operaciones de recepción, se flushea todo paquete recibido con error, directamente de la FIFO en uso (de acuerdo a lo especificado en la descripción del bit DERR en el registro DMAEV) de modo de recibirlo nuevamente. Si este bit es ‘0’ se detiene el manejo automático de errores. * Isochronous mode Cuando este bit está en ‘1’ el USBN9603 ignorará paquetes recibidos con errores (tal como se especifica en la descripción del bit DERR del registro DMAMSK). Si AEH es ‘1’ durante una operación de recepción, el USBN9603 flushea y limpia la FIFO de recepción para recibir el siguiente paquete. Los paquetes erróneos se ignoran y no son transferidos vía DMA. Si se limpia AEHse detiene el manejo automático de errores. Solo se puede escribir este registro cuando el DMA está inactivo. De otro modo se ignora la escritura. Una lectura a este registro mientras ADMA está activo retorna el valor actual del contador, y con ADMA inactivo retorna el valor preestablecido. El contador solo se decrementa si AEH es ‘1’ (Detección de errores automática activada). Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XII Wake-Up Register (WKUP): Parte I PNDUSB Pending USB Wake-Up. Este bit indica que el dispositivo ha sido despertado por actividad en el USB. También señala un requerimiento de interrupción de wake-up pendiente. El host debe limpiar el bit PNDUSB escribiendo ‘0’ en esta dirección. Un reset de hardware pone este bit a ‘1’. PNDUC Pending Microcontroller Wake-Up. Indica que el dispositivo ha sido despertado por un acceso desde el microcontrolador. También indica un requerimiento de interrupción wake-up pendiente. El host limpia el bit PNDUC escribiendo ‘0’ en esta dirección. Un hardware reset pone a ‘1’ este bit. ENUSB Enable USB. Cuando está a ‘1’, este bit habilita el wake-up del dispositivo por actividad en el USB. ENUC Enable Microcontroller. Cuando está a ‘1’, este bit habilita el wake-up del dispositivo por acceso desde el microcontrolador. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XII Wake-Up Register (WKUP): Parte II WKMODE Wake-Up Mode. Este bit selecciona el intervalo luego del cual el dispositivo generará una interrupción wake-up (si está habilitada) cuando ocurra un evento wake-up válido, ya sea: 1 Immediately 2 Luego de un wake-up delay. HOS Halt On Suspend. Cuando este bit está seteado, el dispositivo entra en el modo Halt ni bien se lo setea en estado Suspendido. Una vez que el nodo entra en este estado las escrituras en este bit se ignoran. FHT Force Halt. Cuando el nodo no está attachado (NAT en ‘0’ en el registro MCNTRL), un ‘1’ en este bit fuerza al nodo en el modo Halt. Cuando el nodo se attacha al USB (NAT se pone en ‘1’), se ignora cualquier escritura a ‘1’ de este bit. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XIII Endpoint Control 0 Register (EPC0): Parte I EP Endpoint. Este campo mantiene los 4 bits del número de Endpoint. Para el Endpoint 0, estos bits están cableados a 0000b. DEF Default Address. Cuando está en ‘1’, el dispositivo responde a los requerimientos que se hagan por la Dirección de port 0, independientemente del valor que contengan los campos FAR6-0/EP03-0. Cuando se transmite un paquete IN para el Endpoint, el bit DEF se limpia automáticamente. Este bit aporta en la transición de la dirección default (00000000000b) a la dirección asignada durante la secuencia de enumeración del dispositivo por parte del Host. Esta transición no puede ocurrir en medio de una secuencia de control SET_ADDRESS. Es necesario completar la secuencia de control. Sin embargo, la dirección debe cambiar inmediatamente finalizada dicha secuencia a fin de evitar errores cuando otra secuencia de control siga inmediatamente al comando SET_ADDRESS. Luego de un reset del USB, el firmware tiene 10 mseg. para el set-up, y debe escribir 80h al registro FAR y 00h al registro EPC0. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XIII Endpoint Control 0 Register (EPC0): Parte II DEF (Continuación) Al recibir un comando SET_ADDRESS, el firmware debe escribir 40h al registro EPC0 y 80h <assigned_function_address> al registro FAR. Luego debe encolar un paquete IN de longitud cero para completar la fase de estadosde la secuencia de control SET_ADDRESS. STALL AL setear este bit el chip genera un handshake STALL bajo las siguientes condiciones: 1. Se habilita la FIFO de transmisión y se recibe un token IN. 2. Está habilitada la FIFO de recepción y se recibe un token OUT. Note: Un token SETUP no causa la generación de un handshake STALL cuando este bit es ‘1’. Al transmitir el handshake STALL, los bits RX_LAST y TX_DONE de los registros Receive/Transmit Status respectivamente están seteados. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XIV Transmit Status 0 Register (TXS0): TCOUNT Transmission Count. Indica la cuenta de bytes vacíos disponibles en la FIFO. Este campo nunca es mayor que 8 en el Endpoint 0. TX_DONE Transmission Done. Cuando está seteado, este bit indica que un paquete completó su transmisión. Se limpia con la lectura del dispositivo. ACK_STAT Acknowledge Status. Indica el estado, del paquete ACK previamente enviado. Este bit será interpretado cuando TX_DONE está seteado a 1. Está seteado cuando se recibe ACK; de otro modo permanece en ‘0’. Este bit también se limpia cuando se lee el registro. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XV Transmit Command 0 Register (TXC0): TX_EN Transmission Enable. Habilita la transmisión de datos desde la FIFO. El chip lo limpia cada vez que termina de transmitir un paquete simple, o un handshake STALL, en respuesta a un token IN. Para arrancar la transmisión de un paquete, el firmware necesita setear este bit. El bit RX_EN del registro Receive Command 0 (RXC0) tiene precedencia sobre este bit, es decir, si RX_EN está seteado, se ignora el bit TX_EN hasta que se resetee RX_EN. Los paquetes de longitud cero se indican seteando este bit sin escribir nada en la FIFO. TOGGLE Especifica el PID utilizado para transmitir el paquete. Un valor 0 ocasiona que se genere un DATA0 PID, mientras que un valor ‘1’ origina la generación de un DATA1 PID. Este bit no es alterado por el hardware. FLUSH Un ‘1’ en este bit flushea todos los datos de las FIFO de los Endpoint de control, resetea los Endpoints al estado Idle, limpia los punteros de lectura y escritura de las FIFO, y finalmente se limpia a sí mismo. Si el Endpoint está usando corrientemente la FIFO0 para transferir datos sobre el USB, la operación de flushing se demora hasta que la transferencia se complete. Este bit se limpia en el reset. Es equivalente al bit FLUSH del registro RXC0. IGN_IN Ignore IN tokens. Sieste bit es ‘1’, el Endpoint ignorará cualquier token IN dirigido a su dirección configurada. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XVI Transmit Data 0 Register (TXD0): TXFD Transmit FIFO Data Byte. El firmware escribe aquí solamente el payload de datos del paquete. El PID y CRC16 se crean automáticamente. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XVII Receive Status 0 Register (RXS0): Registro de Estado de Recepción para el Endpoint de Control 0. Para recibir un paquete SETUP luego de recibir un paquete OUT/SETUP de longitud cero, hay dos copias de este registro en el hardware. Una mantiene el estado de recepción de un paquete de longitud cero, y la otra el estado del siguiente paquete SETUP con datos. Si un paquete de longitud cero es seguido por un paquete SETUP, la primer lectura de este registro indica el estado del paquete de longitud cero (con RX_LAST en ‘1’ y RCOUNT en ‘0’), y la segunda el del paquete SETUP. RCOUNT Receive Count. Indica la cuenta de bytes presentes en la RX FIFO. Nunca es superior a 8 para el Endpoint 0. RX_LAST Receive Last Bytes. Indica que se envió un ACK al completarse una operación de recepción exitosa. Este bit no cambia para paquetes de longitud cero. Se limpia cada vez que se lee este registro. TOGGLE Un ‘0’ indica que el PID del último paquete de datos recibido exitosamente fue DATA0. Un ‘1’ indica que fue DATA1. Los paquetes de longitud cero no lo modifican y se limpia cuando se lee este registro. SETUP Indica la recepción de un paquete SETUP. Los paquetes de longitud cero no lo modifican y se limpia cuando se lee este registro. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XVIII Receive Command 0 Register (RXC0): Parte I RX_EN Receive Enable. La recepción de paquetes OUT se deshabilita después de que se recibe cada paquete, o cuando se retorna un handshake STALL en respuesta a un token OUT. Se debe escribir un “1” en este bit para rehabilitar la recepción de datos. La recepción de paquetes SETUP siempre está habilitada. En el caso de paquetes SETUP back-to-back (para un Endpoint dado) donde se recibe un paquete SETUP válido sin intervenir otro token no SETUP, el Endpoint Controller descarta el nuevo paquete SETUP y retorna un handshake ACK. Por cualquier razón que impida al Endpoint Controller aceptar un paquete SETUP, no se generará handshake. Esto permite recuperarse de la situación de haber perdido por el host el ACK del primer token SETUP. IGN_OUT Ignore OUT tokens. Si es ‘1’ el Endpoint ignorará cualquier token OUT dirigido a su dirección configurada. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XVIII Receive Command 0 Register (RXC0): Parte II IGN_SETUP Ignore SETUP tokens. Si es ‘1’, el Endpoint ignora cualquier token SETUP dirigido a su dirección configurada. FLUSH Si es ‘1’ flushea todos los datos de los Endpoint de control de las FIFOs, resetea el Endpoint al estado Idle, limpia los punteros de lectura y escritura de la FIFO, y luego se limpia a sí mismo. Si el Endpoint es utilizado actualmente por la FIFO0 para transferir datos sobre el USB, la operación de flushing se pospone hasta completar la transferencia. Luego de un reset este bit está limpio. Es equivalente a FLUSH del registro TXC0. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XIX Receive Data 0 Register (RXD0): RXFD Receive FIFO Data Byte. El firmware esperará leer solo el payload de datos del paquete. El PID y el CRC16 se remueven del stream de datos de entrada automáticamente. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XX Endpoint Control X Register (EPC1 a EPC6): Parte I Cada Endpoint unidireccional tiene un registro EPCx con los bits siguientes. EP Endpoint. Este campo mantiene el número de Endpoint de 4 bits. EP_EN Endpoint Enable. Si es ‘1’, se usa en la comparación el campo EP3-0, junto con el campo AD6-0 del registro FAR. Si es ‘0’, el Endpoint no responde a ningún token sobre el USB. Note: AD_EN en el registro FAR es la dirección global de comparación habilitada para el USBN9603. Si es ‘0’, el dispositivo no responde en ninguna dirección, a pesar del estado de EP_EN. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XX Endpoint Control X Register (EPC1 a EPC6): Parte II ISO Isochronous. Si es ‘1’, el endpoint es isócrono. Esto significa que no se están enviando NAK si el endpoint no está ready sino habilitado;es decir, si se recibe un token IN y no hay datos disponibles para transmitir en la FIFO, o si un token OUT y la FIFO es full ya que no disponemos de handshake de USB para máquinas sincrónicas. STALL Si es ‘1’ el chip generará handshakes STALL bajo las siguientes condiciones: 1. La FIFO se habilita y se recibe algún token de recepción. 2. La FIFO de recepción está habilitada y se recibe OUT token. Setear este bit no genera un handshake STALL en respuesta al SETUP token. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXI Transmit Status X Register (TXS1, TXS2, TXS3): Parte I Cada una de las tres FIFOs de Endpoints de transmisión tiene un registro de Estados de Transmisióncon los bits que se detallan a continuación. TCOUNT Transmission Count. Indica la cuenta de bytes vacíos disponible en la FIFO. Si esta cuenta es mayor de 31, este campo indicará 31. TX_DONE Transmission Done. Si es ‘1’ indica que el Endpoint respondió a un paquete USB. Un ‘1’ en este bit responde a alguna de las siguientes tres condiciones: 1. Se completó la transmisión de un paquete de datos que responde a un token IN con operación no-ISO. 2. El endpoint envió un handshake STALL en respuesta a un token IN. 3. Se descartó o se transmitió un frame ISO schedulada. Este bit se limpia cada vez que se lee este registro. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXI Transmit Status X Register (TXS1, TXS2, TXS3): Parte II ACK_STAT Acknowledge Status. Vale cuando TX_DONE es ‘1’. Su función difiere de acuerdo a si la operación es ISO (bit ISO en ‘1’ en el registro EPCx) o no-ISO (bit ISO en ‘0’). Para operación no-ISO, este bit indica el estado de ACK del host para el paquete enviado previamente. Vale ‘1’ cuando se ha recibido un ACK; de otro modo, está en ‘0’. Para operación ISO, este bit vale ‘1’ si coincide el LSB de un número de frame (ver bit IGN_ISOMSK), y se han enviado datos en respuesta a un token IN De otro modo está en ‘0’, la FIFO se flushea y TX_DONE es ‘1’. Este bit se limpia cada vez que se lee este registro. TX_URUN Transmit FIFO Underrun. Vale ‘1’ si la FIFO de transmisión se vacía durante una transmisión, y no se escriben datos nuevos en la FIFO. Si es así, el Media Access Controller (MAC) fuerza un error de bit stuff seguido de un EOP. Este bit se limpia cada vez que se lee este registro. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXII Transmit Command X Register (TXC1, TXC2, TXC3): Parte I TX_EN Transmission Enable. Habilita la transmisión de datos desde la FIFO. Cada vez que transmite un paquete o luego de un handshake STALL en respuesta a un token IN, el USBN9603 lo limpia en forma automática. Para comenzar la transmisión de un paquete, el firmware lo debe poner en ‘1’. LAST Si vale ‘1’ indica que se ha escrito en la FIFO el paquete entero. Esto se utiliza en streaming de datos a la FIFO mientras tiene lugar la transmisión del paquete previo. Si durante una transmisión el bit LAST no está seteado y se vacía la FIFO de transmisión, se fuerza en el bus un error de stuff seguido de un EOP. Los paquetes de longitud cero se indican seteando este bit pero sin escribir ningún dato en la FIFO. La máquina de estados de transmisión, transmite el payload de datos, el CRC16 y la señal EOP antes de limpiar este bit. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXII Transmit Command X Register (TXC1, TXC2, TXC3): Parte II TOGGLE Su función difiere si se usa operación en modo ISO (bit ISO en ‘1’ en el registro EPCx) o noISO (bit ISO en ‘0’). Para operación non-ISO, especifica el PID utilizado cuando se transmite el paquete. Un ‘0’ genera un PID DATA0. Un ‘1’ genera un PID DATA1. Para operación ISO, este bit junto con el LSB del frame counter (FNL0) trabajan como máscara para el bit TX_EN bit para permitir el pre encolado de paquetes en números de trama específicos.Se habilita la transmisión solo si el bit 0 del registro FNL está en igual estado que TOGGLE. Si no se ha recibido un token IN durante la validez de esta condición, se flushea el contenido de la FIFO con el siguiente SOF. Si el Endpoint se configuró en modo ISO, el dato siempre se transfiere con un PID DATA0. Este bit no es alterado por el hardware. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXII Transmit Command X Register (TXC1, TXC2, TXC3): Parte III FLUSH Un ‘1’ en este bit flushea todos los datos de la correspondiente FIFO de transmisión, resetea el Endpoint al estado Idle,y limpia los punteros de lectura y escritura de la FIFO. Si el MAC está utilizando en ese momento la FIFO para transmitir datos, se flushea luego de completar la transmisión. Luego de flushear los datos este bit es reseteado por hardware. RFF Refill FIFO. Al setearse el bit LAST automáticamente se salva a un buffer al Transmit Read Pointer (TXRP). Cuando el bit RFF es ‘1’, el TXRP buffereado se recarga en el TXRP. Esto permite repetir la última transacción en caso de no haberse recibido ACK desde el host. Si en ese momento el MAC está utilizando la FIFO para transmitir, TXRP se recargará una vez que la transmisión se complete. Luego de la recarga este bit es reseteado por hardware. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXII Transmit Command X Register (TXC1, TXC2, TXC3): Parte IV TFWL Transmit FIFO Warning Limit. Estos bits especifican cuantos bytes pueden transmitirse desde la FIFO respectiva antes de que ocurra una condición de underrun. Si el número de bytes remanentes en la FIFO es igual o menor que el límite de warning seleccionado, el bit TXWARN del registro FWEV se pone en ‘1’. Para evitar interrupciones por setear este bit mientras la FIFO se está llenando antes de comenzar una transmisión, TXWARN se pone en ‘1’ cuando está habilitada la transmisión desde ese Endpoint (TX_ENx en ‘1’ en el registro TXCx). Ver tabla adjunta. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXII Transmit Command X Register (TXC1, TXC2, TXC3): Parte V IGN_ISOMSK Ignore ISO Mask. Este bit tiene efecto solo si el Endpoint está configurado como isócrono. Si es ‘1’,se deshabilita el lock de números de frame específicos con la función del bit TOGGLE. De este modo los datos se transmiten una vez recibido el siguiente token IN. Si es ‘0’, los datos se transmiten solo si FNL0 coincide con TOGGLE. Este bit se limpia en el Reset. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXIII Transmit Data X Register (TXD1, TXD2, TXD3): Cada FIFO de transmisión tiene un registro Transmit Data cuyos bits se definen a continuación. TXFD Transmit FIFO Data Byte. El firmware solo debe escribir el payload de datos del paquete. El PID y el CRC16 se insertan automáticamente en el stream de datos a transmitir. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXIV Receive Status X Register (RXS1, RXS2, RXS3): Parte I Cada pipe de un Endpoint de recepción (2, 4 y 6) tiene un registro Receive Status con los bits que se definan a continuación. Para permitir la recepción de un paquete SETUP luego de recibirse un paquete OUT de longitud cero, el hardware contiene dos copias de este registro. Una mantiene el estado de un paquete de longitud cero, y la otra el estado del siguiente paquete SETUP con datos. Si un paquete nulo es seguido por un paquete SETUP, la primer lectura de este registro entrega el estado del paqute nulo, mientras que la segunda lectura entrega el estado del paquete SETUP. RCOUNT Receive Count. Indica la cuenta de bytes presengtes en la FIFO del Endpoint de recepción. Si esta cuenta es mayor que 15, se entrega 15. RX_LAST Receive Last. Indica que se envió un ACK luego de una operación exitosa de recepción. Este bit se limpia con la lectura de este registro. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXIV Receive Status X Register (RXS1, RXS2, RXS3): Parte II TOGGLE La función de este bit difiere de acuerdo con el uso de operación ISO (bit ISO del registro EPCx en ‘1’) o no-ISO (bit ISO en ‘0’). Para operación no-ISO, un ‘0’ indica que el último paquete recibido correctamente tenía PID DATA0. Un ‘1’ indica que ese paquete tenía PID DATA1. Para operación ISO, este bit refleja el LSB del número de frame (FNL0) luego de recibirse un paquete con éxito por este Endpoint. Este bit se limpia leyendo el registro RXSx. SETUP Indica la recepción de un paquete SETUP. Se limpia cada vez que se lee este registro. RX_ERR Receive Error. Si es ‘1’, indica un error de medio, tal como bit-stuffing o CRC. Si es ‘1’, el firmware deberá flushear la FIFO correspondiente. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXV Receive Command X Register (RXC1, RXC2, RXC3): Parte I Cada Endpoint de recepción (2, 4 y 6) tiene un registro Receive Command cuyos bits se definen a continuación. RX_EN Receive Enable. No puede recibirse un paquete OUT luego de cada paquete de datos, o cuando se retorna un handshake STALL en respuesta a un token OUT. Este bit debe ser ‘1’ para rehabilitar la recepción de datos. Los paquetes SETUP se pueden recibir siempre. En el caso de paquetes SETUP back-to-back (para un Endpoint dado) en donde un paquete SETUP válido se ha recibido sin otra intervención de tokens no-SETUP, la máquina de estados de recepción descarta el nuevo paquete SETUP y retorna un handshake ACK. Si por alguna otra razón, la máquina de estados de recepción no puede aceptar el paquete SETUP, no se generará HANDSHAKE. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXV Receive Command X Register (RXC1, RXC2, RXC3): Parte II IGN_SETUP Ignore SETUP Tokens. Si es ‘1’, el Endpoint ignora cualquier token SETUP dirigido a su dirección configurada. FLUSH Si se lo pone a ‘1’ flusheas todos los datos de la FIFO de recepción correspondiente, resetea el Endpoint al estado Idle, y resetea los punteros de lectura y escritura de la FIFO. SI el MAC está usando en ese momento la FIFO para recibir datos, el flush se pospone hasta completar la recepción. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXV Receive Command X Register (RXC1, RXC2, RXC3): Parte III RFWL1-0 Receive FIFO Warning Limit. Especifican cuantos bytes mas se pueden recibir en la FIFO respectiva antes de que ocurra una condición de overrun. Si el número de bytes vacíos remanentes en la FIFO es igual o menor que el límite de warning seleccionado, el bit RXWARN del registro FWEV se setea a fín de indicar esta condición. Universal Serial Bus: USBN9603 Modelo de Programación Registros de Transferencia XXVI Receive Data X Register (RXD1, RXD2, RXD3): Cada una de las tres FIFOs de los Endpoint de Recepción tiene asociado un registro Receive Data cuyos bits se definen a continuación. RXFD Receive FIFO Data Byte. El firmware lee solamente el payload de datos del paquete . EL PID y el CRC16 son terminados opor la máquina de estados de recepción. Universal Serial Bus: USBN9603 Modelo de Programación Mapa de Registros I Universal Serial Bus: USBN9603 Modelo de Programación Mapa de Registros II Universal Serial Bus: USBN9603 Modelo de Programación Mapa de Registros III Universal Serial Bus: USBN9603 Modelo de Programación Mapa de Registros IV Universal Serial Bus: USBN9603 Modelo de Programación Mapa de Registros V Universal Serial Bus: USBN9603 Modelo de Programación Mapa de Registros VI

Anuncio

Documentos relacionados

Descargar

Anuncio

Añadir este documento a la recogida (s)

Puede agregar este documento a su colección de estudio (s)

Iniciar sesión Disponible sólo para usuarios autorizadosAñadir a este documento guardado

Puede agregar este documento a su lista guardada

Iniciar sesión Disponible sólo para usuarios autorizados