Document

Anuncio

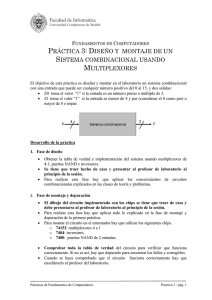

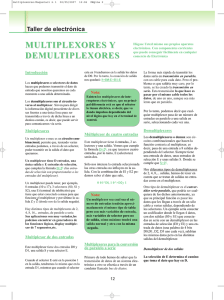

MULTIPLEXORES EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 1 ARQUITECTURAS ESPECIALES MULTIPLEXORES ¿Qué es un Multiplexor? EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 2 • Un multiplexor o MUX es un switch digital (interruptor digital) que conecta una de las entradas con su única salida. • Desde el punto de vista de los sistemas digitales es un circuito combinacional con varios canales de entrada, una única salida y una lógica de control que selecciona el canal que se debe presentar a la salida del circuito. • Las señales de entrada pueden ser más de una. • Por lo general también cuenta con una señal de habilitación que permite que el circuito responda una vez que se selecciona como activo. MULTIPLEXORES Multiplexor EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 3 • También se le conoce como circuito Selector. • Para un multiplexor de 2n - a -1, hay 2n líneas para la entrada de datos, donde “n” corresponde a las líneas de selección donde la combinación de bits determinan la entrada a seleccionar. MULTIPLEXORES MULTIPLEXOR EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 4 • Es un circuito usado para el control de un flujo de información que equivale a un conmutador. • En su forma más básica se compone de dos entradas de datos (A y B), una salida de datos y una entrada de control. Cuando la entrada de control se pone a 0 lógico, la señal de datos A es conectada a la salida; cuando la entrada de habilitación se pone a 1 lógico, la señal de datos B es la que se conecta a la salida... • El multiplexor es una aplicación particular de los decodificadores, tal que existe una entrada de habilitación (EN) por cada puerta AND y al final se hace un OR entre todas las salidas de las puertas AND. http://es.wikipedia.org/wiki/Multiplexor Concepto de multiplexor • MULTIPLEXORES • EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 5 • • • • • La figura que se muestra representa “n” multiplexores. Las entradas se denotan como XD# donde: X representa el multiplexor, D a que la entrada corresponde a una señal de datos y # al número de la entrada que se discute. Las salidas se denotan con una Y y el número que la antecede al multiplexor al que pertenece. Entre las señales de control se encuentran SEL y EN. Como se indica SEL selecciona el canal de entrada que se transfiere a la salida. EN es una señal de control que permite seleccionar el dispositivo y que las salidas se transfieran al pin de salida. La selección del canal de entrada se puede simular como un interruptor que posiciona la entrada que se transfiere a la salida. MULTIPLEXORES Diagrama lógico de un multiplexor EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 6 MULTIPLEXORES Multiplexores EL - 3307 Diseño Lógico Ing. José Alberto Díaz García • Dependiendo de la cantidad de canales de entrada así será la cantidad de líneas de selección. • La cantidad de líneas de selección serán las necesarias para contar en binario la cantidad de entradas que tenga el sistema. • Así en los ejemplos que se muestran para: – Dos entradas, una línea de selección. – Para cuatro entradas, dos líneas de selección – Para ocho entradas, tres líneas de selección. I0 I1 2:1 MUX Z A I0 I1 I2 I3 4:1 MUX Z A B I0 I1 I2 I3 I4 I5 I6 I7 8:1 MUX Z Página 7 A B C MULTIPLEXORES Conexión en cascada EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 8 • Para hacer un multiplexor de 8 entras a una, se podrían utilizar dos multiplexores de 4 a 1 y uno de 2 a 1, tal como se muestra en la figura I0 I1 I2 I3 0 4:1 1 MUX 2 3 S1 S0 I4 I5 I6 I7 0 4:1 1 MUX 2 3 S1 S0 B C 8:1 MUX 0 2:1 Z MUX 1S A MULTIPLEXORES Multiplexor 75LS151 EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 9 • Este es un multiplexor de 8 a 1. • Es muy utilizado en la selección de datos de entrada en los circuitos aritméticos. • Consta de ocho entradas (I0, I1, I2, I3, I4, I5, I6, I7). • La cantidad de líneas de selección son 3 (S0, S1, S2), ya que 2n debe corresponder a la cantidad de entradas. • Y una línea (E) para seleccionar el dispositivo. • Con respecto a las salidas es solamente una (Z), sin embargo también se encuentra disponible su complemento. MULTIPLEXORES Tabla de verdad del Multiplexor 74LS151 EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 10 Diagrama lógico del 74LS151 MULTIPLEXORES Selector de canal EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 11 Entradas Selección de Dispositivo (chip select) Salidas MULTIPLEXORES Conclusión EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 12 • Como se observa del diagrama anterior un multiplexor se puede confeccionar a partir de un decodificador y agregarle una compuerta OR a la salida MULTIPLEXORES Ejemplo EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 13 • Implementación de un multiplexor de 16 entradas utilizando dos multiplexores 75LS151 Ampliación de los canales de entrada • MULTIPLEXORES • EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 14 • • • Si se requiere de un multiplexor con muchos canales de entrada. Este se puede configurar utilizando varios multiplexores, uniendo las salidas por medio de una función de unión (OR) Y un decodificador que seleccione los diferentes selectores de dispositivos dependiendo del canal que se quiere seleccionar. En la figura se muestran 4 multiplexores del tipo 74LS151, para manejar 40 canales de entrada y cinco señales para seleccionar los canales. La selección de los canales se hace de la siguiente forma: – – Los tres bits menos significativos de la dirección del canal se conectan directamente a cada uno de los multiplexores. Los dos bits más significativos se conectan al decodificador de seleccionador de dispositivo que en este caso es un 74LS138, las salidas Y0, Y1, Y2 y Y3 se convierten en las señales que selección los diferentes multiplexores MULTIPLEXORES Método eficiente para implementar funciones booleanas EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 15 • Para un función con “n” variables de entrada (por ejemplo., f(A,B,C,D)): – Necesita un multiplexor con 2n-1 señales de entrada y con n-1 señales de selección. – Enumere la función como en la tabla de verdad con el orden consiste de las variables (por ejemplo, A,B,C,D) – Conecte las variables más significativas, a las señales de selección de canal (por ejemplo, A,B,C) – Examine las parejas de las filas adyacentes (solo las variables menos significativas difieren, por ejemplo, D=0 y D=1). – Determine cuando la salida de la función para combinación de (A,B,C,0) y (A,B,C,1) es (0,0), (0,1), (1,0), o (1,1). – Conecte 0, D, D’, o 1 a la entrada correspondiente de (A,B,C). MULTIPLEXORES EJEMPLO EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 16 • Un sistema binario con cuatro variables de entradas debe generar la función lógica que se muestra en la siguiente tabla de verdad. • En la solución de este ejercicio debe emplearse la metodología anteriormente propuesta. MULTIPLEXORES Tabla de verdad EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 17 • Según la metodología: • El número de variables es 4, entonces necesitamos un multiplexor de 8 entradas, un 74LS151, con tres entradas para seleccionar los canales de entrada. • Las variables más significativas se conectan a las señales de selección del 74LS151. • Como se muestra en la siguiente figura. ENTRADAS SALIDA DECIMAL A B C D F 0 0 0 0 0 1 1 0 0 0 1 1 2 0 0 1 0 0 3 0 0 1 1 1 4 0 1 0 0 0 5 0 1 0 1 1 6 0 1 1 0 0 7 0 1 1 1 0 8 1 0 0 0 1 9 1 0 0 1 0 10 1 0 1 0 0 11 1 0 1 1 0 12 1 1 0 0 0 13 1 1 0 1 1 14 1 1 1 0 1 15 1 1 1 1 0 MULTIPLEXORES Conexión de las variables más significativas EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 18 • La salida se toma de Y. • El dispositivo se selecciona por la señal G´, si la colocamos a tierra siempre el dispositivo estará seleccionado. • Ahora la variable menos significativa se coloca en las entradas según la siguiente metodología. U1 4 3 2 1 15 14 13 12 A B C 11 10 9 7 D0 D1 D2 D3 D4 D5 D6 D7 A B C G 74LS151 Y Y 5 6 F Variable menos significativa MULTIPLEXORES • EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 19 • • • • Si observamos las tres variables más significativas. Cuando se presenta el estado cero por ejemplo, la salida “F” es uno independientemente del valor de la variable “D”, por lo que para este estado la salida siempre es “1”. Cuando el estado es uno a la salida “F” corresponde al valor que tenga la entrada “D”. Cuando el estado es dos a la salida “F” le corresponde el valor que tenga la entrada “D”. Cuando el estado es tres a la salida le corresponde el valor de cero independientemente del valor de la entrada “D”. ENTRADAS SALIDA DECIMAL A B C D F 0 0 0 0 0 1 1 0 0 0 1 1 2 0 0 1 0 0 3 0 0 1 1 1 4 0 1 0 0 0 5 0 1 0 1 1 6 0 1 1 0 0 7 0 1 1 1 0 8 1 0 0 0 1 9 1 0 0 1 0 10 1 0 1 0 0 11 1 0 1 1 0 12 1 1 0 0 0 13 1 1 0 1 1 14 1 1 1 0 1 15 1 1 1 1 0 MULTIPLEXORES Tratamiento para la variable menos significativa EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 20 • O sea podemos introducir en un mapa las diferentes condiciones que toman los estados. • Estas condiciones se llevan a las entradas del multiplexor y nos resulta el siguiente circuito. 1 D D D D 0 D 0 MULTIPLEXORES Circuito resultante EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 21 • La variable menos significativa “D” entra a formar parte de un lógica que se conectará a los pines de entrada. VCC U1 D 1 2 A B C 4 3 2 1 15 14 13 12 11 10 9 7 D0 D1 D2 D3 D4 D5 D6 D7 A B C G 74LS151 Y Y 5 6 F MULTIPLEXORES APLICACIONES EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 22 • La función de un multiplexor da lugar a diversas aplicaciones: – Selector de entradas. – Serializador: Convierte datos desde el formato paralelo al formato serie. – Transmisión multiplexada: Utilizando las mismas líneas de conexión, se transmiten diferentes datos de distinta procedencia. – Realización de funciones lógicas: Utilizando inversores y conectando a 0 ó 1 las entradas según interese, se consigue diseñar funciones complejas, de un modo más compacto que con las tradicionales compuertas lógicas. MULTIPLEXORES BIBLIOGRAFIA EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 23 • http://es.wikipedia.org/wiki/Codificad or, consultado el 16 de julio del 2007 • http://www.ti.com/, consultado el 2 de setiembre del 2007 • Fletcher, William I. An Engineering approach to digital design, Prentince Hall, Inc. Primera edición, USA, 1980