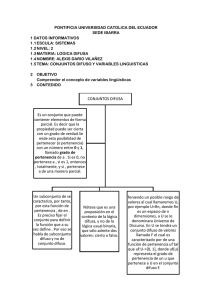

Arquitectura de un Controlador Lógico Difusousando Lógica

Anuncio