COMPUTADORES SIMD 1. Organizaciones b´asicas. 2. Estructura

Anuncio

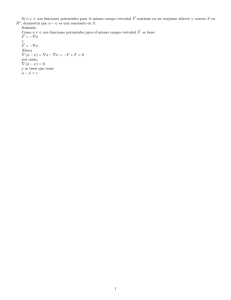

T EMA 14: C OMPUTADORES SIMD 1. Organizaciones básicas. 2. Estructura interna de cada elemento de proceso. 3. Programación de los computadores SIMD. Bibliografı́a: K. Hwang, F.A. Briggs, Computer Architecture and Parallel Procesing, McGrawHill, 1984. Versión en castellano (1987): Arquitectura de Computadoras y Procesamiento Paralelo, McGraw-Hill, 1987. K. Hwang, Advanced Computer Architecture: Parallelism, Scalability, Programmability, McGraw-Hill, 1993. Departamento de Informática de Sistemas y Computadores (DISCA) Facultad de Informática de Valencia 14-1 1 ORGANIZACIONES BÁSICAS. 1. Organizaciones básicas. Concepto de computador SIMD Arquitectura del juego de instrucciones vectorial. Ejecución rápida de las instrucciones vectoriales: Múltiples UAL’s bajo el dominio de una sola unidad de control → Single Instruction Multiple Data. Todas las UAL ejecutan la misma instrucción sobre distintos datos. Diagrama de bloques Memoria de programa UC EP0 EP1 EPn-1 M0 M1 Mn-1 Red de interconexion La memoria de programa es única y accesible sólo por la unidad de control. La unidad de control decodifica las instrucciones, ejecutando directamente las escalares. Cuando decodifica una instrucción vectorial, difunde la misma operación a todas las UAL, que la ejecutan simultáneamente. Ese funcionamiento sı́ncrono limita la frecuencia de funcionamiento. Los módulos de memoria almacenan los datos vectoriales. Pueden estar asignados estática o dinámicamente a las UAL. Una red de interconexión permite que las UAL se comuniquen entre sı́ o establece la correspondencia entre las UAL y los módulos de memoria. El sistema completo se gobierna desde un computador externo “convencional” que da acceso a los periféricos y realiza la administración del sistema. 14-2 1 ORGANIZACIONES BÁSICAS. Organizaciones básicas En función de la interconexión entre las UAL y los módulos de memoria. 1. Computadores SIMD de memoria distribuida. Host Bus de datos Memoria de programa Unidad de Control Bus de control EP0 EP1 EPn-1 M0 M1 Mn-1 Red de interconexion Cada UAL tiene su propio módulo de memoria local, accesible sin conflicto. Las UAL pueden intercambiar datos entre sı́ a través de la red de interconexión, gobernada por la unidad de control → no hay conflictos de acceso a la red de interconexión. Las transferencias, como una instrucción mas, se realizan por parte de todas las UAL. El contenido de los módulos de memoria de datos se prepara/recupera antes/después del procesamiento por parte del host → los módulos de memoria de datos suelen formar parte del espacio de direccionamiento del host. 14-3 1 ORGANIZACIONES BÁSICAS. 2. Computadores SIMD de memoria compartida. Host Bus de datos Memoria de programa Unidad de Control Bus de control EP0 EP1 EPn-1 Red de interconexion M0 M1 Mm-1 Los módulos de memoria son globales. Cualquier UAL puede acceder a cualquier módulo. ⇒ Más flexible. La red de interconexión establece la correspondencia entre las UAL y los módulos de memoria. Está gobernada por la unidad de control → no hay conflictos de acceso a la red de interconexi ón, ni a los módulos de memoria. La red de interconexión debe permitir tanto que una UAL pueda conectarse con cualquier módulo de memoria, como que todas las UAL puedan estar conectadas simultáneamente con un módulo de memoria distinto. ⇒ Red de interconexión cara. El tiempo de acceso a memoria aumenta, disminuyendo el ancho de banda de la memoria. 14-4 1 ORGANIZACIONES BÁSICAS. El número de módulos de memoria (M ) se elije de manera que sea un número primo, para facilitar el acceso simultáneo a cualquier estructuras matricial definida por una dirección inicial D y una distancia de salto d, siempre que d no sea múltiplo de M (estrategias de almacenamiento “oblicuo”). Ejemplo: P = 4 y M = 5. La matriz 4×4: a00 a10 a20 a30 a01 a11 a21 a31 a02 a12 a22 a32 a03 a13 a23 a33 se puede almacenar: M0 M1 a00 a01 a11 a12 a22 a23 a33 M2 M3 M4 a02 a03 a13 a10 a20 a21 a30 a31 a32 Fila, d = 1 Columna, d = 4 El contenido de los módulos de memoria de datos se prepara/recupera antes/después del procesamiento por parte del host → los módulos de memoria de datos suelen formar parte del espacio de direccionamiento del host. ⇒ Solamente una máquina, el Burroughs Scientific Processor ha empleado esta configuración. 14-5 2 ESTRUCTURA INTERNA DE CADA ELEMENTO DE PROCESO. 2. Estructura interna de cada elemento de proceso. (Illiac IV) D I R S UAL Registros de uso general: A, B, C . . . La unión de todos los registros del mismo nombre (A, B, C,. . . ) constituye algo equivalente a un registro vectorial. Registro de dirección propia D. Registro que contiene el identificador del elemento de proceso. Es de solo lectura. Registro de ı́ndice local I. Cuando la instrucción vectorial a ejecutar requiere operar con vectores en memoria, la unidad de control difunde la misma dirección a todos los elementos de proceso. El registro I permite modificar esta dirección: Dir. efectiva en la memoria local = Dir. base (unidad de control) + I Registro de interconexión R. Constituye el puerto de entrada/salida a la red de interconexión. Registro de máscara S. Si está a “0”, enmascara la operación difundida por la unidad de control. La unión de todos los registros de máscara forma algo equivalente al registro de máscara vectorial (VM) de los computadores vectoriales segmentados. Módulo de memoria local asociado a cada elemento de proceso. 14-6 2 ESTRUCTURA INTERNA DE CADA ELEMENTO DE PROCESO. Ejemplos de instrucciones: 1. Carga vectorial (≈LV Va,Ra): Cada elemento de proceso carga en el registro de uso general A el dato presente en su posición de memoria local Ra . 2. Suma vectorial (≈ADDV Va,Vb,Vc): Cada elemento de proceso suma los registros B y C, depositando el resultado en A. 3. Creación de vector de ı́ndices (≈CVI): Cada elemento de proceso calcula un ı́ndice, en función de su registro de dirección propia D, y lo almacena en el registro de ı́ndice I. 4. Carga vectorial indexada (≈LVI Va,(Ra+Vi)): Cada elemento de proceso carga en el registro de uso general A el dato presente en su posici ón de memoria local (Ra + I). 5. Comparación vectorial (≈SxxV Va,Vb): Cada elemento de proceso eval úa la condición xx, depositando el resultado sobre el registro S. 6. Puesta a “1” del vector de mascara vectorial (≈ CVM): Cada elemento de proceso escribe un “1” en el registro S. 7. Preparación de operación de salida: Cada elemento de proceso copia un registro de uso general sobre el registro R. 8. Operación de salida por el enlace x: Cada elemento de proceso transmite el contenido del registro R a través del enlace x, copiándose sobre el registro R del elemento de proceso vecino. 9. Obtención del resultado de una operación de entrada: Cada elemento de proceso copia el contenido del registro R en un registro de uso general. 14-7 3 PROGRAMACIÓN DE LOS COMPUTADORES SIMD. 3. Programación de los computadores SIMD. Ejemplo Computador SIMD, con n elementos de proceso conectados seg ún una red de interconexión “hipercubo”. Matriz A, de tamaño n × n. Cada módulo de memoria tiene una columna de la matriz. ⇒ Escribir un algoritmo para sumar la diagonal principal, depositando el resultado en la memoria del elemento de proceso 0. Hipercubo de 8 nodos: P6 P4 P7 c2 P5 c1 c0 P2 P0 P1 EP0 A: a00 a10 .. a,n-10 M0 P3 EP1 A: a01 a11 ... an-11 M1 EPn-1 A: a’n-1 a1n-1 ... an-1n-1 Mn-1 14-8 3 PROGRAMACIÓN DE LOS COMPUTADORES SIMD. P0 P1 P2 P3 P4 P5 P6 P7 a00 a11 a22 a33 a44 a55 a66 a77 Algoritmo: S[i] := 1, i = 0..7 I[i] := D[i] RegA[i] := M[A+I[i]] S[i] := 1, i = 1,3,5,7 S[i] := 0, i = 0,2,4,6 R[i] := RegA[i] Transferir segun c0 S[i] := 1, i = 0,2,4,6 S[i] := 0, i = 1,3,5,7 RegA[i] := RegA[i] + R[i] S[i] := 1, i = 2,6 S[i] := 0, i = 0,1,3,4,5,7 R[i] := RegA[i] Transferir segun c1 S[i] := 1, i = 0,4 S[i] := 0, i = 0,1,2,3,5,6,7 RegA[i] := RegA[i] + R[i] S[i] := 1, i = 4 S[i] := 0, i = 0,1,2,3,5,6,7 R[i] := RegA[i] Transferir segun c2 S[i] := 1, i = 0 S[i] := 0, i = 1,2,3,4,5,6,7 RegA[i] := RegA[i] + R[i] 14-9 3 PROGRAMACIÓN DE LOS COMPUTADORES SIMD. Algoritmo para n procesadores: ParFor i := 0 to n-1 do S[i] := 1; ParFor i := 0 to n-1 do I[i] := D[i]; ParFor i := 0 to n-1 do RegA[i] := M[A+I[i]] etapas := log2(n); for j := 0 to etapas-1 do begin ParFor i := 0 to n-1 do If ((D[i] MOD 2ˆ(j+1))=2ˆj) then S[i] := 1 else S[i] := 0; ParFor i := 0 to n-1 do R[i] := RegA[i]; ParFor i := 0 to n-1 do Transferir(enlace_j); ParFor i := 0 to n-1 do If ((D[i] MOD 2ˆ(j+1))=0) then S[i] := 1 else S[i] := 0; ParFor i := 0 to n-1 do RegA[i] := RegA[i]+R[i]; end; 14-10