PROTOCOLO BUS I C

Anuncio

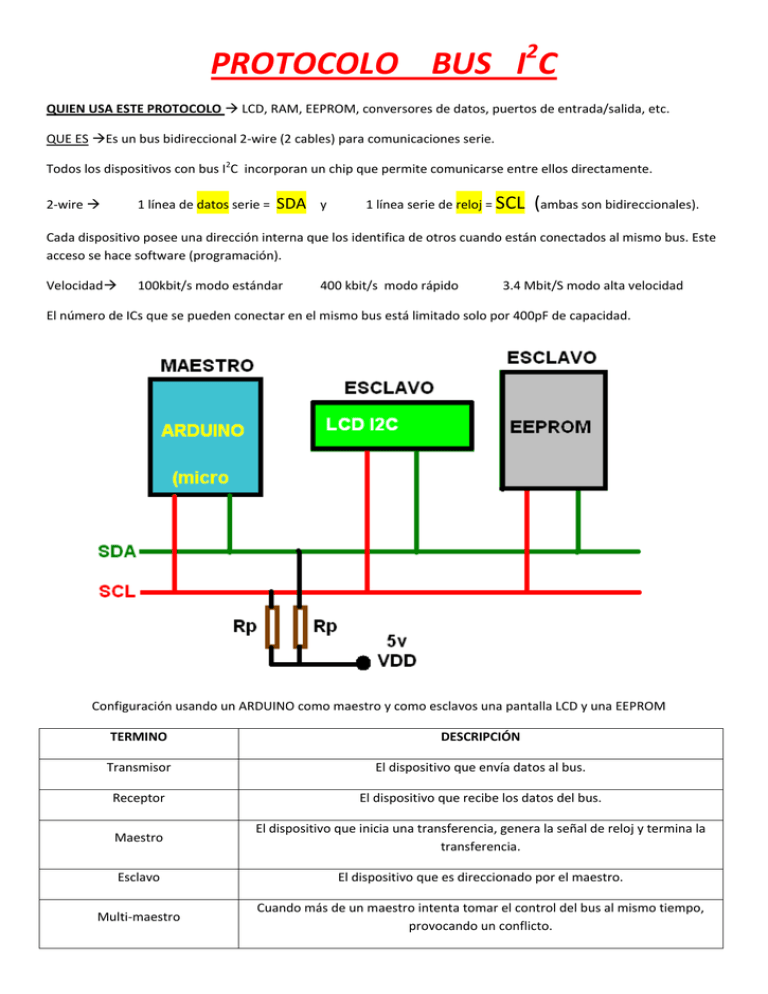

PROTOCOLO BUS I2C QUIEN USA ESTE PROTOCOLO LCD, RAM, EEPROM, conversores de datos, puertos de entrada/salida, etc. QUE ES Es un bus bidireccional 2-wire (2 cables) para comunicaciones serie. Todos los dispositivos con bus I2C incorporan un chip que permite comunicarse entre ellos directamente. 2-wire 1 línea de datos serie = SDA y 1 línea serie de reloj = SCL (ambas son bidireccionales). Cada dispositivo posee una dirección interna que los identifica de otros cuando están conectados al mismo bus. Este acceso se hace software (programación). Velocidad 100kbit/s modo estándar 400 kbit/s modo rápido 3.4 Mbit/S modo alta velocidad El número de ICs que se pueden conectar en el mismo bus está limitado solo por 400pF de capacidad. Configuración usando un ARDUINO como maestro y como esclavos una pantalla LCD y una EEPROM TERMINO DESCRIPCIÓN Transmisor El dispositivo que envía datos al bus. Receptor El dispositivo que recibe los datos del bus. Maestro El dispositivo que inicia una transferencia, genera la señal de reloj y termina la transferencia. Esclavo El dispositivo que es direccionado por el maestro. Multi-maestro Cuando más de un maestro intenta tomar el control del bus al mismo tiempo, provocando un conflicto. FUNCIONAMIENTO SDA y SCL son líneas bidireccionales, conectadas a la alimentación (5v para Arduino) a través de resistencia (pull-up). Cuando el bus está libre SDA = HIGH y SDL = HIGH. Ambas están a nivel alto. Las etapas de salida de los dispositivos conectados en el bus deben ser de drenador abierto o colector abierto para realizar la función AND de todas ellas. Validación de datos Los datos en SDA deben ser estables durante el nivel alto del reloj (SCL = HIGH). El cambio de estado de la línea (HIGH o LOW) se debe producir cuando SCL = LOW. Bit de inicio (start) Cuando pasa SDA de nivel ALTO a BAJO mientras SCL permanece ALTO. Bit de parada (stop) Cuando pasa SDA de nivel BAJO a ALTO mientras SCL permanece ALTO. Inicio y Parada son generados por el maestro. El bus se considera ocupado después de la condición de inicio. El bus se considera libre después de la condición de parada. El bus está ocupado si se repite la condición de inicio en lugar de la condición de parada. Formato del byte (8 bits) Cada byte pone en la línea SDA debe tener 8 bits. Debe ser seguido por un bit de reconocimiento (ACK). El MSB (bit más significativo) se transmite en primer lugar. El bit ACK es obligatorio. El maestro genera un pulso de reloj durante el que el cuando esta a nivel alto, el receptor debe poner la línea SDA a nivel bajo. SINCRONIZACIÓN Generación del reloj Todos los maestros generan su reloj en la línea SCL para transferir los mensajes al bus. Los datos son válidos solo durante el periodo ALTO del reloj. La sincronización del reloj es realizada usando la conexión AND de todos los esclavos en la línea SCL. Esto significa que un paso de nivel ALTO a BAJO en la línea SCL causarán que los dispositivos dispuestos a empezar reinicien sus contadores a nivel BAJO. Esto mantendrá la línea SCL a nivel BAJO hasta que le reloj alcance un nivel ALTO. El paso de BAJO a ALTO de este reloj puede no cambiar el estado de la línea SCL si otro reloj está aún en su periodo BAJO. La línea SCL se mantendrá a nivel BAJO por el dispositivo que tenga mayor periodo BAJO. Los dispositivos con cortos periodos BAJOS pasan a ALTO durante este tiempo. En caso de varios dispositivos mirar el documento oficial de Philips I2C especificaciones. FORMATO DE LA DIRECCIÓN (7 bits) 1) Bit de INICIO. 2) 7 bits de dirección (Determina el esclavo seleccionado por el maestro) 3) 1 bit (8º) R/W 0 = WRITE (escribir) y 1 = READ (leer) 4) Bit de PARADA (Si quiere enviar más datos sería un repetir INICIO) TRANSMISIÓN DESDE EL MAESTRO AL ESCLAVO TRANSMISIÓN MAESTRO LEE DATOS DE UN ESCLAVO FORMATO COMBINADO PRIMER BYTE DESPUES DEL PROCEDIMIENTO DE INICIO