3.- Placa base

Anuncio

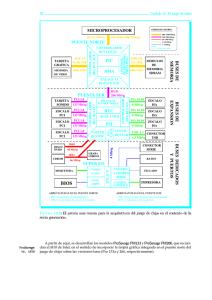

Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.- Placa base Tabla de contenido 3.1.- INTRODUCCIÓN 4 Buses: ............................................................................................................................................................................................ 5 Chipset.......................................................................................................................................................................................... 5 3.2.- BUSES DEL SISTEMA 6 3.3.- BUS DE GESTIÓN DEL SISTEMA 7 System Management Bus (SMBus) 7 Funcionamiento......................................................................................................................................... 7 Señales .................................................................................................................................................... 7 Aplicaciones .............................................................................................................................................. 8 Detección de presencia de módulos de memoria DIMM (SPD: Serial Presence Detect)............................................. 8 Gestión de otros dispositivos del sistema .............................................................................................................................. 8 3.4.- BUSES DE EXPANSIÓN Introducción 9 9 Ancho de banda ........................................................................................................................................ 9 Interfaz de bus.......................................................................................................................................... 9 Comunicación con los dispositivos de E/S 10 E/S Programada: ......................................................................................................................................10 Escritura en un puerto:............................................................................................................................................................10 Lectura de un puerto:...............................................................................................................................................................10 Interrupciones..........................................................................................................................................13 Interrupciones Hardware ........................................................................................................................................................13 El controlador de interrupciones (8259) ..............................................................................................................................14 Interrupciones Software ..........................................................................................................................................................15 Tabla de vectores de interrupción .........................................................................................................................................16 Configuración de los vectores de interrupción ...................................................................................................................17 Ventajas e inconvenientes .......................................................................................................................................................17 DMA (Acceso directo a memoria) ...............................................................................................................18 Ventajas e inconvenientes .......................................................................................................................................................18 El controlador DMA (8237)...................................................................................................................................................18 Obsoletos 18 XT...........................................................................................................................................................18 ISA. ........................................................................................................................................................19 MCA (Micro Channel Architecture)..............................................................................................................19 EISA (Enhanced ISA) ................................................................................................................................19 Bus local VESA .........................................................................................................................................19 PCI (Peripheral Component Interconnect) 20 Transferencia de datos..............................................................................................................................20 Placa base 1/1 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Fase de direccionamiento........................................................................................................................................................20 Fase de transferencia de datos................................................................................................................................................21 Fin de la transferencia..............................................................................................................................................................21 Control de errores ....................................................................................................................................................................21 Control del bus.........................................................................................................................................21 Señal LOCK# ...........................................................................................................................................................................22 Slots master y slave...................................................................................................................................................................22 Configuración...........................................................................................................................................23 Interrupciones ...........................................................................................................................................................................25 Puente PCI a ISA (PCI to ISA bridge) .........................................................................................................26 Puente PCI (PCI Bridge)............................................................................................................................26 Extensiones de la revisión 2.1....................................................................................................................27 Extensión a 64 bits ...................................................................................................................................................................27 Extensión a 66 Mhz .................................................................................................................................................................27 Direccionamiento de 64 bits...................................................................................................................................................27 PCI Hot-Plug ............................................................................................................................................28 Elementos implicados..............................................................................................................................................................28 Versiones....................................................................................................................................................................................29 3.5.- CIRCUITOS INTEGRADOS DE LA PLACA BASE Chipset 30 30 Fabricantes de chipsets .............................................................................................................................31 Ejemplos .................................................................................................................................................31 SIS 5598......................................................................................................................................................................................31 AMD 760 ...................................................................................................................................................................................32 Intel 850 .....................................................................................................................................................................................32 VIA Apollo P4X333 ................................................................................................................................................................33 Otros circuitos integrados 33 Generador de frecuencias..........................................................................................................................33 Temporizadores-contadores ......................................................................................................................34 Controlador de teclado..............................................................................................................................35 Entradas/salidas .......................................................................................................................................35 Monitorización del hardware 36 Winbond W83781D...................................................................................................................................36 Descripción................................................................................................................................................................................37 Interfaces....................................................................................................................................................................................37 National Semiconductor LM79....................................................................................................................37 3.6.- ALIMENTACIÓN DE LA PLACA BASE 39 Conector AT 39 Conector ATX 39 3.7.- DISEÑO 40 Distribución de los componentes 40 Disipación térmica 40 Placa base 2/2 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Segundo ventilador...................................................................................................................................42 Capas 42 interferencias Electromagnéticas (EMI) 43 3.8.- CONFIGURACIÓN 44 3.9.- EJEMPLOS 45 Placa base AMI Fortress 3000 (Chipset intel 440gx) 45 Placa base Intel D850GB 46 3.10.- ATX (REVISIÓN 2.01) 47 Procesador 47 Zócalos de memoria 47 Conectores I/O 48 Fuente de alimentación 48 Unidades de almacenamiento 48 Chasis 48 Placa base 3/3 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.1.- INTRODUCCIÓN Es una placa de circuito impreso (PCB: Printed Circuit Board) que soporta y conecta físicamente los elementos fundamentales de un ordenador: Microprocesador, memoria, chipset, tarjetas de periféricos, conectores, condensadores, etc. Placa base 4/4 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 En la siguiente imagen podemos observar el diagrama de bloques de una placa base genérica basada en el mismo chipset Intel 440BX: Buses: Bus del externo del micro. También llamado Host Bus, Bus frontal del sistema (FSB: Frontal Side Bus). Bus de memoria (72 bits = 64 bits de datos + 8 bits de paridad opcional). Bus del sistema gráfico (2X AGP Bus). Buses de expansión: (PCI, ISA, USB). Bus de gestión del sistema (System Management Bus). Chipset Intel 440 BX, compuesto de dos circuitos integrados: 82433BX y 82371EB Puente norte: 82433BX contiene: Interfaz con el bus externo del micro, controlador de memoria, interfaz con sistema gráfico, interfaz PCI. Puente sur: 82371EB (conocido como PIIX4E) contiene: puente PCI a ISA, controladora Bus Serie Universal (USB), dispositivos estándar (controlador DMA, controladores de interrupción 82C59, RTC y memoria CMOS, ...), controladora EIDE. Placa base 5/5 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.2.- BUSES DEL SISTEMA En principio consideraremos buses del sistema como aquellas lineas de comunicación que conectan directamente la CPU con los dispositivos básicos del sistema: • Host Bus: Controlador de memoria ⇔ CPU. También se conoce este bus como Bus frontal del sistema (FSB: Front Side Bus). • Bus de memoria: Controlador de memoria ⇔ Memoria. lineas de datos, direcciones y control. Dual Indepent Bus Architecture Tecnología Intel usada en Pentium PRO y posteriores. Arquitectura de bus dual independiente (CPU ⇔ Caché, CPU ⇔ Memoria). Esta separación del bus de la memoria principal libera ancho de banda del sistema de memoria y permite a la caché nivel 2 funcionar a una velocidad muy superior. Bus GTL+: Conecta el procesador al Host Bridge (controlador de memoria principal, bus PCI...). Esta diseñado para SMP (Multiproceso Simétrico) y múltiples buses PCI. Bus caché: Conecta el nucleo del procesador a la caché nivel 2. Placa base 6/6 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.3.- BUS DE GESTIÓN DEL SISTEMA Llamaremos así a cualquier bus cuya principal función sea conectar dispositivos de gestión con el sistema. Se usa para controlar y obtener información de dispositivos de la placa base. De momento el único bus de estas características implementado en sistemas PC es el llamado System Mangement Bus. SYSTEM MANAGEMENT BUS (SMBUS) • Es una implementación específica realizada por Intel basada en el bus I2C desarrollado por Philips. • Es un bus serie donde datos y direcciones comparten las misma linea por la que los dispositivos se intercambian comandos sincronizados por la señal de reloj. Funcionamiento • La especificación se refiere a tres tipos de dispositivos. - Slave: es un dispositivo que está recibiendo datos o respondiendo a un comando. - Master: es un dispositivo que envía comandos, genera la señal de reloj y finaliza la transferencia. - Host: es un dispositivo master especializado que proporciona la interfaz principal con la CPU del sistema. En los varios de los chipsets de Intel la interfaz con el SMBus se encuentra en el PIIX4. Este circuito integrado puede actuar como host lo que permite a la CPU comunicarse con dispositivos slave. También puede funcionar como slave para que dispositivos master externos puedan activar eventos relacionados con la gestíon de energía. Para ello incorpora tres patillas: SMBALERT#, SMBCLK, SMBDATA. • Es un bus multimaster, o sea, que se pueden conectar varios dispositivos al bus y cada uno de ellos puede actuar como master iniciando una transferencia con dispositivos slave. En la imagen, el conector SMBus de la placa base Asus P2B permite la conexión a este bus de dispositivos externos a la placa. Señales - SMBDATA: linea única (i.e. bus serie) de datos y direcciones (i.e. bus multiplexado). - SMBCLK: Placa base Señal de reloj proporcionada por el master (i.e. bus síncrono). 7/7 Mantenimiento de Equipos Informáticos - Apuntes 01/02 ver. 5.2 SMBALERT#: Linea por la que un dispositivo Slave puede pedir atención al host ante una situación de alerta (P.ej. una temperatura excesiva del micro detectada por su dispositivo sensor). Esta linea es opcional, por lo que no todos los dispositivos la poseen. - Vcc_SMB: Alimentación del bus. Aplicaciones Detección de presencia de módulos de memoria DIMM (SPD: Serial Presence Detect) • Los módulos DIMM pueden incorporar de serie un circuito integrado EEPROM que almacena un conjunto de parámetros de temporización críticos, así como información sobre el fabricante del módulo y del circuito integrado. • Esta detección de presencia incluida en las rutinas del POST, la lleva a cabo el PIIX4E a través el SMBus. Los datos obtenidos se graban en la CMOS RAM (También incluida en el PIIX4E). • Utiliza las señales SMB_CLK, SMB_DATA conectadas a cada DIMM. Gestión de otros dispositivos del sistema • Utilizan este bus circuitos integrados para monitorización del hardware (temperatura, tensiones de alimentación, velocidad de rotación de ventiladores, etc..) que se encuentran en las placas base actuales y que veremos posteriormente. • Gestión de parametros del micro: Como se vió en el capítulo de micros, Intel comenzó a incorporar este bus de gestión en el Pentium III Xeon para la gestión de temperatura, nº de serie y otros datos incluidos en el micro. • También utilizan este bus las baterías inteligentes para ordenadores portátiles. Esto permite avisar al sistema conocer el estado de carga de la batería. Placa base 8/8 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.4.- BUSES DE EXPANSIÓN • Permiten la comunicación de la CPU y de la memoria con los distintos periféricos del sistema: Video, impresoras, modems, discos duros, etc.. INTRODUCCIÓN Ancho de banda • Cuando se habla de buses, se define el ancho de banda (BW = BandWidth) como la cantidad teórica de datos que puede transportar el bus por unidad de tiempo. • Se calcula como: Anchura de bus x Frecuencia x Nº de datos por ciclo Bus Anchur a (bits) Velocida d (MHz) 8-bit ISA 8 8.3 Datos por ciclo 1 16-bit ISA 16 8.3 1 15,9 EISA 32 8.3 1 31,8 VLB 32 33 1 127,2 PCI 32 33 1 127,2 64-bit PCI 2.1 64 66 1 508,6 254,3 Ancho de banda (MBytes/sec) 7,9 AGP 32 66 1 AGP (x2 mode) 32 66 2 508,6 AGP (x4 mode) 32 66 4 1.017,3 Nota: 1 MByte/seg = 1.024 Kbytes/seg = 1.048.576 bits/seg. ≠ 1.000.000 bits/seg Interfaz de bus Cuando en un sistema conviven varios buses, se necesitan circuitos integrados que permitan la comunicación entre ellos. El propio bus PCI necesita una interfaz (controlador PCI del chipset) para poder conectarse al micro a través del Bus del sistema. Actualmente es muy común el llamado puente PCI-ISA (PCI to ISA bridge) que forma parte de los chipsets desde la aparición del bus PCI (P. Ej. Incorporado en el PIIX4 del chipset 430TX, 440LX y 440BX). Como su nombre indica tiene como propósito mapear los viejos dispositivos ISA en el bus PCI, permitiendo su coexistencia. Placa base 9/9 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 COMUNICACIÓN CON LOS DISPOSITIVOS DE E/S Las tres técnicas básicas de controlar la transferencia de datos hacia/desde un periférico son: • E/S Programada. • Interrupciones. • DMA (Acceso directo a memoria). E/S Programada: En inglés programmed I/O (PIO) esta técnica se basa en la ejecución de instrucciones E/S como la IN y OUT del repertorio del 8086. Mediante esta técnica la CPU envía una orden al dispositivo (lectura, escritura, configuración, test), y se mantiene ocupada hasta que concluye la operación. El dispositivo no interrumpe a la CPU para comunicar que ya ha terminado la operación, si no que es la CPU quien debe ocuparse de comprobarlo periódicamente. Como puede deducirse por lo expuesto, esta técnica consume mucho tiempo de CPU Desde el 8086, la comunicación de la CPU con los periféricos NO se realiza con el mismo mapa de direcciones que la memoria. • Se realiza mediante los llamados puertos, que son direcciones de 16 bits (entre 0 y 65535) y que forman el llamado espacio de direcciones I/O. • Estas direcciones no se refieren a circuitos integrados de la memoria RAM, sino a registros que se encuentran físicamente en los propios dispositivos donde se puede leer y/o escribir. Escritura en un puerto: • Se activa una señal de control que identifica que la próxima dirección del bus de direcciones, no se refiere a una dirección de memoria si no a un puerto. 1. Se coloca la dirección del puerto en los 16 bits inferiores del bus de direcciones. 2. La CPU espera a que el dispositivo permita la escritura. (Activando la señal de strobe). 3. La CPU escribe en el puerto mediante el bus de datos. Lectura de un puerto: 1. Se activa una señal de control que identifica que la próxima dirección del bus de direcciones, no se refiere a una dirección de memoria si no a un puerto. Placa base 10/10 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 2. Se coloca la dirección del puerto en los 16 bits inferiores del bus de direcciones. 3. El dispositivo espera a que la CPU pueda atenderle. (Señal de strobe). 4. La CPU lee en el bus de datos la información puesta por el dispositivo. • Para estos procedimientos, el repertorio de instrucciones del 80x86 contiene las instrucciones ensamblador IN y OUT. • Las direcciones de los puertos para los dispositivos estándar se encuentran asignadas. Véase tabla adjunta. Placa base 11/11 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Distribución estándar de los puertos de Entrada/Salida Dispositivo XT AT • Cada dispositivo añadido por el usuario debe configurarse (mediante jumpers o programa de configuración propio) para ocupar un rango de direcciones libre para evitar conflictos. El controlador de teclado del AT (8042) utiliza de forma estándar el rango de direcciones 0060h a 006Fh, es decir 16 registros para la transferencia de datos y configuración de su funcionamiento. En el siguiente trozo de código vemos como se accede al puerto del controlador del teclado en ensamblador: in al, 60h; Leer del puerto 60h, correspondiente al controlador de teclado cmp al, 128; ¿Se ha soltado la tecla? jae mirutina; en caso afirmativo saltar a la rutina etiquetada como “mirutina” Placa base 12/12 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Interrupciones Interrupciones Hardware Cada dispositivo pide servicio a través de una linea de interrupción. El 8086 sólo dispone de una entrada de petición de interrupción (INTR - INTerrupt Request) y una salida de concesión de interrupción (INTA – INTerrupt Acknowledge). Ante la posibilidad de que varios dispositivos activen su interrupción simultaneamente, las interrupciones no las trata directamente la CPU, sino un controlador (Desde los primeros PC’s, el circuito integrado 8259 o compatible). 5 1 Tarjeta red IRQ 9 Linea IRQ9 E000:01AA Controlador interrupciones (8259) driver tarjeta red 3 2 INTR INTA CPU 4 0000:01C7 E000:01AA 0000:01C4 1. El dispositivo pide servicio a través una de las lineas de interrupción presentes en el bus. En la figura una tarjeta de red que usa la interrupción hardware IRQ9 que corresponde a la interrupción nº 71h de la tabla de vectores de interrupción, según la tabla que veremos más adelante. 2. El controlador de interrupciones activa la señal INTR de la CPU. 3. El micro guarda en la pila el estado actual de los registros, deshabilita la posibilidad de atender cualquier otra interrupción (mediante el flag IF) y accede a la petición activando la señal INTA. 4. El controlador de interrupciones 8259 sitúa en el bus de datos el vector de interrupción. Cada IRQ tiene asignada una posición de memoria (vector de interrupción) donde se halla la dirección del controlador (driver) que se ocupará de tratar dicha interrupción. (En el ejemplo el vector nº 21h que ocupa las direcciones 1C4 – 1C7, es decir 4 bytes) 5. Se ejecuta la rutina de atención que puede hallarse en memoria RAM o en el BIOS. 6. Se restaura el estado de los registros desde la pila al estado anterior de atender la interrupción. Esto incluye volver a habilitar las interrupciones (flag IF). 7. Se continúa la ejecución del programa en el punto donde se interrumpió. Placa base 13/13 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 El controlador de interrupciones (8259) • Controla las IRQs de forma que se ejecuten según el orden de prioridad predefinido por el 8086: IRQ 0 mayor prioridad que IRQ 1, IRQ 1 mayor prioridad que IRQ 2, etc.. • En el XT sólo hay un controlador 8259 capaz de gestionar 8 IRQs hardware. • En el AT se utilizan dos controladores para llegar hasta las 16 IRQs hardware: 1. Cuando se activa una IRQ hardware entre la 8 y la 15 (en la figura la IRQ 9). 2. El segundo controlador activa la IRQ 2 del primer INT 71h IRQ0 IRQ1 IRQ2 CPU 8259 2 controlador, quien averigua cual de las IRQ se ha activado. 3 IRQ7 3. El controlador primario pasa a la CPU la interrupción 71h que se corresponde con la IRQ9. • De lo anterior se desprende que las interrupciones hardware IRQ8 a IRQ15 tienen mayor prioridad que la IRQ3 a IRQ7. Además, el número total de IRQ8 IRQ9 IRQ10 1 8259 IRQ9 interrupciones hardware utilizables, se reduce a 15. IRQ15 Placa base 14/14 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Interrupciones Software Aunque no sirven para la comunicación directa dispositivo-CPU, se explican aquí las interrupciones software por su analogía de funcionamiento. Se llaman desde un programa para hacer que se ejecute una función del BIOS o del DOS. Estas funciones son contempladas por la CPU como subrutinas, que una vez finalizadas, devuelven el control al programa que las llamó. P. ej. para llamar a cualquier servicio (rutina) del DOS se utiliza la interrupción 21h. Como el vector de interrupción ocupa 4 bytes (21h x 4 bytes = 84h) las posiciones que ocupa son 84h-87h. Para especificar cual de los servicios disponibles se requiere, se carga el número de servicio en el acumulador (registro AX del microprocesador, concretamente en su parte alta, es decir AH). El siguiente trozo de código ensamblador muestra el carácter “A” en la posición actual del cursor. MOV AH, 06H ;función 06h del DOS, muestra carácter en pantalla MOV DL, ‘A’ ;seleccionar el carácter ASCII “A” INT 21H ;llamada a los servicios del DOS Placa base 15/15 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Tabla de vectores de interrupción N º Direcc ión Descripción N º Direcció n Descripción • Este método permite la compatibilidad, pues cada fabricante puede utilizar sus propias rutinas, mientras coloque su dirección de comienzo en la posición correcta de la tabla de vectores. • El 8088 y posteriores soportan 256 interrupciones (entre software y hardware). Placa base 16/16 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 • Cada vector está formado por 2 palabras (base y desplazamiento) de 16 bits = 4 bytes. P. ej. A000:1D01. • 256 interrupciones x 4 bytes = 1024 bytes. Ocupa el primer KB de memoria. 0000:0000 – 0000:03FF. Configuración de los vectores de interrupción • Los programas residentes (TSR) y los controladores de dispositivo (drivers) son los que más apuntados por los verctores de interrupción, para trabajar con el sistema. • El proceso de carga de un controlador de dispositivo (driver) incluye además de la copia en memoria del código que lo forma, la escritura del vector de interrupción para que apunte a la dirección de comienzo de dicho código. P. ej. podemos ver los vectores de interrupción mediante el comando debug de MS-DOS. C:\>debug -d 0000:0000 0000:0000 68 10 A7 00 8B 01 70 00-16 00 98 03 8B 01 70 00 h.....p.......p. 0000:0010 8B 01 70 00 B9 06 0C 02-40 07 0C 02 FF 03 0C 02 ..p.....@....... 0000:0020 46 07 0C 02 EC 06 29 05-3A 00 98 03 54 00 98 03 F.....).:...T... 0000:0030 6E 00 98 03 88 00 98 03-A2 00 98 03 FF 03 0C 02 n............... 0000:0040 9D 08 0C 02 8D 09 0C 02-93 09 0C 02 5D 04 0C 02 ............]... 0000:0050 99 09 0C 02 0D 02 DA 02-AC 09 0C 02 8B 05 0C 02 ................ 0000:0060 F6 0B 0C 02 FC 0B 0C 02-07 0C 0C 02 AD 06 0C 02 ................ 0000:0070 AD 06 0C 02 A4 F0 00 F0-37 05 0C 02 13 4C 00 C0 ........7....L.. el contenido del primer vector, que ocupa las direcciones 0h –3h (formato base:desplazamiento) se obtiene leyendo al revés el resultado del comando debug (68 10 A7 00) es decir, 00A7:1068. Por lo tanto, la rutina de atención a la interrupción 0h se encuentra en la posición 00A7:1068 = 01AD8 = 0000:1AD8 y por lo tanto en el primer segmento estándar Analogamente, podríamos ver por ejemplo, la rutina que maneja la interrupción 09h correspondiente a la IRQ1, y destinada al teclado. Acudiendo a la tabla vemos que el vector de esta interrupción se encuentra en la posición 24h – 27h, que según lo devuelto por debug (EC 06 29 05), corresponde a la posición 0529:06EC. Ventajas e inconvenientes Este método es útil cuando: • El procesador debe responder rápidamente a un evento (p. ej. señal de reloj) para transferir datos. • Sincronizar diferentes eventos. Cuenta con la desventaja: • Las interrupciones requieren tiempo de procesador para dirigirse a la rutina de servicio (conocido como latencia de interrupción) y tiempo para realizar las tareas de la rutina de servicio. Placa base 17/17 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 DMA (Acceso directo a memoria) • La técnica DMA (Direct Memory Access) permite transferir datos entre un dispositivo y memoria o de una zona de memoria a otra sin la intervención del micro (Excepto para arbitrar la transferencia). Esto es mas rápido que el método tradicional donde cada dato llega a la CPU quien lo graba en memoria. • Requiere de un dispositivo que controle la operación en sustitución del micro. • El bus ISA permite DMA mediante el obsoleto controlador DMA (8237) que veremos mas adelante. • El bus PCI ya contempla entre sus características la posibilidad de acceder a memoria, por lo que no necesita de hardware adicional. Ventajas e inconvenientes • Este método es útil cuando se deben transferir grandes bloques de datos (P. ej. lectura/escritura en disco). • No es útil cuando la CPU tiene que procesar uno por uno los datos que se leen/escriben. El controlador DMA (8237) • Trabaja sincronizado con el bus ISA, por lo que en las placas actuales donde la CPU trabaja mucho más rápido que el bus, no ofrece ninguna ventaja respecto al acceso mediante interrupciones. PIO (Programmed Input/Output). • El 8237 está bastante anticuado, por lo que no puede emplearse por ejemplo en mover datos desde la tarjeta gráfica a memoria. • En los AT, se encargaba además del ciclo de refresco necesario para la memoria DRAM. Actualmente este cometido lo realizan circuitos integrados específicos (El controlador de memoria en chipsets Intel 430TX y posteriores). • OBSOLETOS XT • El primer bus de expansión nación con los primeros ordnadores XT y se quedó con el nombre. • Bus direcciones 20 bits (Aunque sólo 16 se usan para direccionar dispositivos E/S) • Bus de datos 8 bits. • Velocidad de funcionamiento igual que la CPU: 4,7 MHz. Placa base 18/18 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 ISA. • Industrial Standard Architecture. Es el bus que se usa en el PC desde que se definió para usarse con el 80286 y su arquitectura AT. • Llamado bus AT pues se implementó en los sistemas AT. • Compatible con el XT de 8 bits. • Bus direcciones 24 bits, bus de datos 16 bits. • La ranura de expansión se compone de una ranura idéntica a la de 8 bits, alineada junto a otra que soporta los 8 bits que faltan y las nuevas lineas de dirección. • Frecuencia de funcionamiento adaptada al 286: primero 4,77 MHz y luego 8,3 MHz. Se quedó ahí a pesar del aumento de frecuencia del 286 (12 – 20 MHz). • Limitada capacidad de configuración automática de dispositivos. • Limitado a 15 interrupciones hardware, 7 canales DMA. MCA (Micro Channel Architecture) • Nace para aprovechar la potencia de los 32 bits de los 386 IBM en sus sistema PS/2. • Bus de 32 bits. • Incompatible ISA. No pueden convivir en un sistema. Este factor junto con el elevado precio de los periféricos provocó su escaso éxito y su pronta desaparición. • Tanto las tarjetas como el controlador del bus incluyen inteligencia para liberar de trabajo a la CPU. • Configuración software de puertos e IRQs. EISA (Enhanced ISA) • Nace como respuesta del resto de fabricantes al bus MCA de IBM. • Bus de datos de 32 bits que posibilita tasas de transferencia mayores de 20 MB/s • Compatible con ISA lo que limita la frecuencia de reloj a 8,3 MHz. • Configuración: Los dispositivos “se presentan” al controlador del sistema, o se configuran con el software suministrado, por lo que precisa electrónica adicional para la inteligencia propia de las tarjetas y del controlador del bus. Esto encarece los dispositivos. • Mediante el SETUP, hay que indicar al sistema la utilización de tarjetas ISA junto la IRQ que utilicen. Bus local VESA • Bus local: Está acoplado directamente con la CPU, por lo que se alimenta de la misma frecuencia de reloj y tiene acceso a las mismas lineas de datos y direcciones. Placa base 19/19 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 • Pensado en principio para resolver el cuello de botella que el bus ISA suponía para el subsistema gráfico. • Su diseño dependiente de la CPU hacía que determinadas tarjetas no funcionararn adecuadamente en todos los sistemas. • Desapareció prematuramente debido a la casi simultanea aparición del estándar PCI que acabó imponiendose. Diseñado para frecuencias de reloj de hasta 40 MHz funcionaba bien en 486DX-33 y DX2-66 con frecuencias de bus de 33 MHz. Planteaba problemas en placas 486DX-50 cuya frecuencia de bus era 50 MHz, pues muchas tarjetas fallaban esta velocidad. PCI (PERIPHERAL COMPONENT INTERCONNECT) Su arquitectura es independiente del procesador, por lo que es necesario que entre ambos haya un controlador de bus. Esto permite su utilización en otras plataformas (Alpha, Power PC, …). Así por ejemplo, una misma tarjeta pueda instalarse en sistemas distintos, cambiando únicamente los controladores de dispositivo (drivers). • Hasta la versión 2.1 sólo funciona a 33’3 MHz. Velocidad máxima teórica: 33’3 MHz x 32 bits ≅ 127 MB/s. • Bus de direcciones y datos multiplexados en las lineas AD[31-0]. Esto permite al conector mantener unas medidas reducidas. Transferencia de datos En terminología PCI las transferencias de datos se realizan entre un iniciador (initiator) que asume el control del bus (bus master) y un destinatario (target) que funcionará como esclavo (bus slave). Una transferencia de datos está compuesta por una primera fase de direccionamiento y por una o varias fases posteriores de lectura/escritura de datos. Fase de direccionamiento Las 4 lineas denominadas C/BE[3:0]# (Command/Byte Enable) se encuentran multiplexadas, de manera que durante esta fase se utilizan para codificar comandos, mientras que en la fase de transferencia de datos indican cuales de los bytes de datos son válidos. La fase de direccionamiento comienza con la activación de las señal FRAME#. Durante esta fase el iniciador activa las señales C/BE[3:0]# que codifican el tipo de transferencia que va a tener lugar (Lectura de memoria, escritura en memoria, lectura de dispositivo E/S, escritura en dispositivo E/S, etc...). Las direcciones aparencen en el bus multiplexado, lineas AD[31-0] Placa base 20/20 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 El sufijo # en el nombre de una señal indica que es activa a nivel bajo. C/BE[3:0 ]# 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 Comando Interrupt Acknowledge Special Cycle I/O Read I/O Write Reserved Reserved Memory Read Memory Write Reserved Reserved Configuration Read Configuration Write Memory Read Multiple Dual Address Cycle Memory Read Line Memory Write and Invalidate Fase de transferencia de datos Durante esta fase las señales multiplexadas C/BE[3:0]# se utilizan como Byte Enable, es decir, indican cual de los 4 bytes de datos es válido y cual no. Esto permite transferencias de datos de longitud variable. • Los datos aparencen en el bus multiplexado, lineas AD[31-0]. • Tanto el iniciador como el destinatario pueden insertar estados de espera durante la transferencia desactivando las señales IRDY# (Initiator ReaDY) y TRDY# (Target ReaDY). Fin de la transferencia El iniciador puede terminar la transferencia desactivando la señal FRAME# durante la última fase de datos. El destinatario puede finalizar la transferencia activando la señal STOP#. Control de errores El bus dispone de la señal PAR que compone la paridad par sobre las señales AD[31:0] y BE[3:0]#. Esta señal tiene la misma temporización que AD[31:0] pero retrasada un ciclo de reloj para permitir el cálculo de paridad. Control del bus Placa base 21/21 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 A diferencia del bus ISA que proporciona un controlador específico para el acceso directo a memoria de los periféricos (Controlador DMA 8237), PCI no proporciona un circuito especial para ese propósito. En cambio contempla un mecanismo de transferencia llamado Bus mastering. El iniciador activa la señal REQ# (REQuest=petición) para indicar al controlador PCI que desea tomar el control del bus. El controlador PCI confirma la propiedad del bus activando la señal GNT# (GraNT=cesión) convirtiendo al iniciador en lo que se conoce como Bus master. Señal LOCK# El iniciador activa la señal LOCK# pidiendo acceso exclusivo al bus para realizar múltiples transacciones con el destinatario. Transferencia a memoria de una tarjeta de adquisición de datos sin Bus mastering (arriba) y con Bus mastering (abajo). • Impide que otros iniciadores modifiquen las direcciones bloqueadas (mínimo de 16 bytes bloqueables). • Durante el bloqueo se pueden realizar otras transacciones no exclusivas con direcciones no bloqueadas. Slots master y slave Cada slot PCI tiene su propia linea REQ# y otra GNT# que va unida al controlador PCI. Por ejemplo el Host Bridge de los chipsets de Intel dispone de 4 patillas para REQ# y otras 4 para GNT#. Es por esto que, en principio, sólo puede haber 4 slots PCI con capacidad Bus master. Placa base 22/22 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 En la imagen, una tarjeta de red PCI tiene la conexión 18 (REQ#) sin utilizar. Por tanto esta tarjeta no puede utilizar Bus Mastering en las transferencias de datos. El manual de la misma indica "Data Transfer: 32 bit I/O", que lo confirma. Este hecho penaliza sus prestaciones y aumenta el uso de CPU respecto de tarjetas con capacidad Bus Mastering. En la otra cara observaríamos lo mismo referido al contacto nº 17 que corresponde a la señal GNT#. Hay placas base que añaden un quinto slot PCI llamado "Slave" que no puede alojar tarjetas bus master, al no disponer de las señales REQ# y GNT# y debe realizar las tareas de transferencia mediante interrupciones (modo PIO), lo que involucra al procesador. Ver imagen adjunta. Configuración Cada dispositivo incluye un conjunto de registros de configuración que permiten su identificación de tipo (SCSI, video, Ethernet, etc...), y fabricante. Otros registros permiten la configuración de las direcciones E/S, direcciones de memoria, interrupciones que se usarán para la comunicación con el sistema. • Durante el arranque las rutinas PCI/PnP del BIOS asignan los recursos a los dispositivos y guardan esta información en la CMOS-RAM (ocupando memoria superior: E000-EDFF) en lo que se Placa base 23/23 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 denomina ESCD (Extended System Configuration Data). Esto permite que la información permanezca hasta el próximo arranque. (Salvo que se active la opción “Clear ESCD” en el BIOSSetup) • Después de que la BIOS PCI ha inicializado los dispositivos, el control pasa al sistema operativo. Aquí es donde el sistema operativo comienza a cargar los drivers. El driver llama a las rutinas BIOS PCI para obtener información sobre los recursos que "su" hardware utiliza. Para ello usa la identificación del dispositivo (ID) y el nº de fabricante (p. ej. 8086 = Intel). • Para acceder a las rutinas PCI presentes en el BIOS, se utiliza la interrupción software INT 1AH y el valor 1BH en la parte alta del acumulador. El número de función se pasa a través de la parte baja del acumulador. • Durante la carga de drivers el bus PCI permanece bajo el control del sistema operativo, pero una vez finalizada el control vuelve al BIOS. Windows 9x Puede acceder directamente a los registros de configuración de los dispositivos y además puede acceder al ESCD. Esto le permite modificar las asignaciones de recursos de cada dispositivo. Windows NT Nunca usa el ESCD. Utiliza llamadas directas a los registros de configuración de los dispositivos. Placa base 24/24 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Interrupciones • Cada Slot PCI cuenta con 4 lineas ( INTA#, INTB#, INTC#, INTD#). Las tarjetas utilizarán una linea para cada función que implementen. Una tarjeta que únicamente implementa una función (P. Ej. tarjeta de red) utilizará solamente la linea INTA#. Sin embargo, una tarjeta PCI que incorpore interfaz de red y modem utilizaría INTA#, INTB#. P. ej. La tarjeta de red Kingston KNE30BT especifica: I/O Base Address: 0000h-FFFFh (set by BIOS PCI). Interrupt (IRQ) Levels: INTA (set by BIOS PCI). • Para compatibilizar con las interrupciones estándar (IRQs) se utiliza un circuito integrado (puente ISA-PCI) que enruta las INTn# hacia las IRQs: El enrutador de interrupciones PCI (p. Ej. el incluido en el circuito integrado 82371EB-PIIX4) cuenta con 4 lineas (PIRQA#, PIRQB#, PIRQC#, PIRQD#) que se conectan a las de los slots (INTA#, INTB#, INTC#, INTD#). • Los dispositivos pueden utilizar las lineas INTx# de los slots PCI que son redirigidas a las IRQs por el enrutador según una tabla que reside en la BIOS PCI. Los dispositivos PCI pueden entonces usar su linea INTx# para generar la IRQ y mantener así la compatibilidad con el software antiguo. Supongamos que tenemos una aplicación MS-DOS diseñada para una tarjeta de sonido SoundBlaster ISA antigua. Deseamos que dicha aplicación funcione sobre una tarjeta SoundBlaster PCI. Ese viejo software usará un driver MS-DOS que accede al hardware mediante una IRQ y puertos E/S. Cuando la tarjeta PCI requiera servicio activará su linea INTx#. Mediante la tabla de la BIOS PCI se enrutará dicha petición generando la IRQ que el driver espera. Esto hará que la CPU busque el vector de interrupción correspondiente a esa IRQ y se ejecute el driver MS-DOS. • La BIOS puede asignar más de una IRQ al mismo dispositivo. • Además dos dispositivos pueden compartir la misma IRQ. Este aparente conflicto lo resuelve el sistema operativo, que cuando se activa una interrupción, llama de forma encadenada a cada gestor de interrupción hasta que uno de ellos reclama dicha interrupción. Placa base 25/25 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 En la imagen podemos observar como en un sistema una tarjeta de red (E100B) y la controladora SCSI (aic78xx) comparten la IRQ 14. Puente PCI a ISA (PCI to ISA bridge) • Es un circuito integrado que permite colgar un bus ISA de un bus PCI consiguiendo que en una placa base convivan ambos buses. Es utilizado por todas las placas base en las que conviven ambos buses. • En las placas actuales este elemento se encuentra dentro del chipset (P. Ej. Intel PIIX4). Puente PCI (PCI Bridge) Permite incrementar la capacidad del bus a un mayor número de dispositivos. Placa base 26/26 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 • La arquitectura Bridged Bus utiliza un puente de bus PCI a PCI para ampliar la capacidad de dispositivos. Estos puentes suelen ser ASICs (Circuitos integrados de propósito específico) que aislan eléctricamente dos buses PCI, permitiendo que las transferencias pasen de un bus a otro. • La arquitectura Peer Bus consigue mayor rendimiento, ya que cada uno de los buses PCI lleva su propio circuito integrado Host-to-PCI bridge. Extensiones de la revisión 2.1 Extensión a 64 bits • Utiliza un conector extendido compatible con tarjetas de 32 bits. • Dobla el ancho de banda teórico, lo que permite soportar mejor tecnologías como Gigabit Ethernet y Fibre Channel. Extensión a 66 Mhz • Motivos de carga eléctrica y restricciones en la temporización impiden soportar más de dos dispositivos. Para solucionar este problema se suele utilizar la arquitectura peer bus vista anteriormente. • Pueden conectarse dispositivos de 33 MHz en un bus de 66 MHz. Hay que tener en cuenta que el bus trabajará tan rápido como el más lento de los dispositivos conectados. • Este bus resulta ideal para interconexiones de sistemas que formen un cluster donde es crítica la baja latencia de las señales de control y datos entre los servidores del cluster. Frequenci a Bus Velocidad transferencia 32-Bit 64-Bit 33 MHz 127 MB/seg 254 MB/seg 66 MHz 254 MB/seg 508 MB/seg Direccionamiento de 64 bits. • La especificación 2.1 de PCI define la capacidad de direccionar mas de 4 GB (32 bits 232 = 4 GB) de memoria del sistema mediante el uso de 64 bits de direcciones. • Este direccionamiento es posible en dispositivos de 32 bits, pero necesitan que la fase de direccionamiento dure dos ciclos de bus, mientras que los dispositivos de 64 bits lo hacen en uno. Placa base 27/27 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 PCI Hot-Plug Observese en la figura la arquitectura de un sistema PCI Hot Plug • Permite la inserción/sustitución en caliente de tarjetas en el bus PCI, eliminando los tiempos muertos tan importantes en servidores. • La especificación PCI hot-plug en su revisión 1.0, define interfaces software y hardware para tarjetas PCI, pero no define como deben ser implementados por los fabricantes. • Permite la coexistencia con tarjetas PCI que no soporten Hot-Plug. • Cuando falle una tarjeta, se desactivará su ranura PCI, se sustituirá dicha tarjeta y se volverá a activar. Elementos implicados Placa base: • El controlador PCI debe poseer capapacidad Hot-plug para controlar individualmente las señales de cada ranura PCI. • Modificaciones para evitar riesgos eléctricos en las ranuras PCI activas. • Facilidad para el acceso a las ranuras. Tarjetas y driver del dispositivo: Lógicamente las tarjetas y sus drivers deben estar diseñados para soportar esta tecnología. Placa base 28/28 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Sistema operativo: Cada sist. op. debe definir capas de interfaz entre el hardware y el nucleo del sistema operativo. Por ejemplo, un servidor PC con tecnología PCI hot-plug puede utilizar dos tarjetas de red, una de ellas redundante. Al fallar la tarjeta principal, la tarjeta de reserva se activará automáticamente. Sin necesidad de apagar el sistema puede reemplazarse la tarjeta averiada, Eliminándose los tiempos muertos del sistema. Versiones Dependiendo de las distintas implementaciones de esta especificación pueden incluirse o no las siguientes características: • Hot plug PCI replacement: Sustituir un dispositivo que falla por otro idéntico. • Hot plug PCI upgrade: Sustituir dispositivos y controladores por nuevas versiones. • Hot plug PCI Expansion: Instalar tarjetas adicionales y drivers. Placa base 29/29 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.5.- CIRCUITOS INTEGRADOS DE LA PLACA BASE Interconexión típica de los principales componentes de un sistema basado en AMD K6 (izda.) y en el AMD Duron (dcha.). La placa base soporta varios circuitos integrados con distintas funciones: CHIPSET El chipset es el conjunto de circuitos integrados más importante de la placa base. En la actualidad, la mayoría de los chipsets se componen de dos circuitos integrados: El Northbridge (o memory Hub) y el Southbridge. (I/O Hub). Placa base 30/30 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 • Se encargan de gestionar las transferencias de datos entre los distintos buses, sirviendo de interfaz entre el micro y la memoria, controladores de E/S, tarjetas de expansión. • La tendencia actual es agrupar cada vez más funciones dentro del chipset. Muchos de los circuitos integrados originales del XT y AT, como el controlador de interrupciones 8259 (PIC: Programmable Interrupt Controller), el controlador DMA (Direct Memory Access: 8237), el reloj de tiempo real RTC (Real Time Clock), etc... se encuentran integrados en el chipset. • Cada chipset requiere de una versión específica del BIOS. • Definen las prestaciones de la placa base, por ejemplo: - Soporte PCI: versión 2.1, 32 o 64 bits. - Tipo y cantidad de memoria soportada FPM, EDO, BEDO, SDRAM, parity-checking, ECC. - Tipo de Caché L2: burst, pipeline burst, síncrona, asíncrona. - Soporte multiprocesador. Fabricantes de chipsets Además de Intel, que es el principal fabricante de Chipsets, existen otros como VIA, AMD, SIS, UMC, ALI, Opti, etc… Ejemplos Plataforma Super 7 Para plantar cara a Intel y su Slot 1, un grupo de empresas, liderado por AMD y Cyrix, formaron la denominada plataforma Super 7. Este grupo mantenía que el Socket 7 no había muerto y, consiguieron que fabricantes de chipsets, como ALI, SIS o VIA, dotaran a este tipo de placas con avances de la época como el bus a 100 MHz, bus AGP, y las especificaciones del PC 98. P. ej. Via Apollo VP3, MVP3: bus AGP, 100 MHz, Caché L2 de hasta 2 MB, memoria cacheable > 64 MB. SIS 5598 Integra todas las funciones de control de la placa base en un único circuito integrado. Soporte UDMA 33 MBps, incluye tarjeta gráfica. Placa base 31/31 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 AMD 760 Diagrama de bloques del Chipset AMD 760 para microprocesador AMD Athlon. Observar los distintos buses y su anchura. Intel 850 • Diseñado como soporte al Pentium 4. • Microarquitectura “NetBurst” con 2 canales de RDRAM que proporciona un ancho de banda de 3’2 GB/s en el bus de memoria. • Bus de sistema de 400 MHz. Placa base 32/32 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 VIA Apollo P4X333 Diagrama de bloques del chipset VIA Apollo P4X333 para Pentium 4. Entre otras cosas aporta: • Soporte para memoria DDR 333 • AGP 8X, • ATA/133, • USB 2.0 OTROS CIRCUITOS INTEGRADOS Generador de frecuencias Los primeros sistemas basados en el 8086 usaban el circuito integrado 8284A para generar las distintas señales de reloj necesarias en el sistema: CPU y periféricos. En los sistemas actuales, existe un circuito integrado que se encarga de generar las señales de reloj para los distintos elementos de la placa base. Placa base 33/33 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 • Necesitan de un cristal de cuarzo que determina la frecuencia de referencia. Utilizando divisores y multiplicadores de frecuencia, este circuito integrado genera las demás señales de reloj de diversas frecuencias. • Estos cristales situados en la placa se distinguen por su encapsulado metálico plateado en el que está inscrita su frecuencia de oscilación. Ejemplo: Winbond W83194R-39. Acepta un cristal de referencia de 14,318 MHz. 2 señales de reloj para CPU. 13 señales de reloj para 3 DIMMs de memoria SDRAM a 100 MHz. 6 señales de reloj síncronas para PCI. Una señal de 48 MHz para USB. En la siguiente imagen vemos el esquema de conexiones de un sintetizador de reloj CK100 para chipset Intel 440BX, ZX, etc... Se aprecian las entradas para el cristal de referencia de 14'318 MHz, y como salidas las señales de reloj para la CPU , para el bus PCI y para el bus USB. Temporizadores-contadores • Desde el 8086 se dotó a las placas base XT con un circuito integrado dotado de tres temporizadores, cada uno de los cuales puede generar una señal de frecuencia programable por software a partir de una señal de referencia conectada a cada uno de los contadores. Placa base 34/34 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 • En los primeros PCs, se utilizaba el circuito integrado 8253 y posteriormente el 8254. Actualmente la funcionalidad del 8254 se encuentra integrada dentro del chipset (P.ej. PIIX4): - El primero de los tres contadores (counter 0) genera 18,2 veces por segundo una interrupción hardware IRQ0. Esto se puede utilizar para temporizar eventos en una aplicación. - El segundo contador (counter 1), proporciona una señal de periodo 15µs. Está conectada al controlador DMA para poder usarlo en el refresco de memoria DRAM. - El tercer contador (counter 2) se usa en conexión con el altavoz del sistema para crear distintos tonos audibles. Se puede programar el 8253 accediendo a los puertos de entrada/salida 42h, 43h para que genere una frecuencia determinada. A continuación mediante el puerto de entrada/salida 61h puede activarse el altavoz que sonará a la frecuencia programada en el 8253. Controlador de teclado Antiguamente esta función la desempeñaba el circuito integrado Intel 8042 o compatible. Actualmente no se encuentra en la placa base y sus funciones las realiza uno de los circuitos integrados del chipset o un circuito integrado llamado Super I/O. The keyboard controller provides the following functions to the PC: • Cuando recibe un código de tecla desde el teclado, activa la IRQ1. • También maneja la entrada para el ratón tipo PS/2 que hay en muchos equipos actuales. Así es como lo diseño originalmente IBM cuando creó el estándar PS/2. Entradas/salidas • Son los circuitos integrados responsables de la interfaz del sistema con periféricos como el teclado, puerto serie, puerto paralelo, disquetera. • Aunque estas interfaces solían estar en tarjetas de ampliación, en la actualidad se encuentran en un único circuito integrado de la placa base. Placa base 35/35 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Ejemplo: Winbond W83977ATF • Controla 2 disqueteras. • 2 UARTs de alta velocidad para ambos puertos serie. • Soporte para puerto de infrarrojos. • Puerto paralelo compatible IEEE 1284. • Controlador de teclado (compatible 8042). MONITORIZACIÓN DEL HARDWARE • Hay diversos circuitos integrados en el mercado que cumplen esta función, por lo que es cuestión de cada fabricante de placas base integrar uno u otro. • La función de estos integrados es la de ofrecer información al usuario de parámetros vitales para el buen funcionamiento del sistema: - Tensiones de la fuente de alimentación. - Funcionamiento de los ventiladores. - Temperatura del micro y del sistema. - Apertura del sistema (para evitar intrusiones). Winbond W83781D Placa base 36/36 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Descripción • Es un circuito integrado para sistemas basados en microprocesador. Puede monitorizar: - 3 sensores de Tª (termistores). - 5 tensiones analógicas positivas. - 2 tensiones analógicas negativas. - 3 salidas de tacómetros de ventiladores. - 1 entrada para circuitos de detección de apertura de la caja. • Mediante sus entradas VID[0-4] que se conectan a salidas del mismo nombre del Pentium II y posteriores puede averiguar las tensiones de alimentación que necesita el micro. • Accesible desde software estándar como LANDesk Client Manager Integración en sistemas de gestión empresarial. Interfaces • Puede programarse a través de dos buses: - ISA mediante los puertos 295h y 296h del espacio de direcciones de E/S (instrucciones IN y OUT). - Bus serie de gestión del sistema (SMBus) a través del PIIX4. • El usuario puede ajustar los límites superior e inferior de las magnitudes que se monitorizan. Cuando se sobrepasan estos límites: - Puede habilitarse un tono acústico. - Puede generar interrupciones software (patilla SMI#) y hardware (patilla INT). Ejemplo: Placa Asus P2B Utiliza las direcciones I/O 290H-297H para comunicarse con el W83781D, de forma que hay que tenerlo en cuenta al instalar tarjetas ISA no PnP para que no utilicen los mismos puertos. National Semiconductor LM79 • Interfaz ISA para acceder a los registros internos de estado y control. El acceso a dichos registros se realiza escribiendo el offset del registro en el puerto 05h de E/S seguido de una lectura del puerto 06h. • También es accesible mediante el SMBus. • Mediante sus entradas VID[0-4] que se conectan a salidas del mismo nombre del Pentium II y posteriores puede averiguar las tensiones de alimentación que necesita el micro. • Dispone de entradas para ventiladores dotados de salidas de tacómetro. Esta salida aporta una señal consistente en un pulso por cada vuelta del ventilador. Placa base 37/37 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 El que una placa incorpore uno de estos circuitos integrados no significa que se monitorizen todos los parámetros de los que es capaz: • El fabricante de la placa base puede no incluir conectores para todas las E/S del circuito integrado. • El fabricante del PC puede no utilizar todos los conectores disponibles. Por ejemplo, no incorporar fuente de alimentación cuyo ventilador esté dotado de tacómetro. • El fabricante puede no incluir un software adecuado para la monitorización y control de todos los parámetros disponibles, con lo que debe incorporarse por separado. Placa base 38/38 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.6.- ALIMENTACIÓN DE LA PLACA BASE • Las placas toman la tensión de la fuente de alimentación que transforma la corriente alterna de la red en tensiones continuas. • Algunas placas Pentium disponían de un zócalo llamado VRM (Voltage Regulator Module) que permite la futura utilización del P55C que requieren una menor tensión de funcionamiento. • Las placas actuales incluyen reguladores de tensión para poder proporcionar la diversidad de tensiones de alimentación de los distintos componentes (Módulos de memoria, microprocesador, Chipset,...). Básicamente existen dos tipos de conexiones de alimentación a las placas: CONECTOR AT • Es el que utilizaban la mayoría de placas hasta hace poco. • Proporciona tensiones +5V, -5V, +12V y –12V. CONECTOR ATX • Es el utilizado actualmente en placas con este formato para la conexión de fuentes ATX. • Proporciona 3’3V además de las tensiones del conector AT (+5V, -5V, +12V y –12V). • Incorpora señales de control para la comunicación del sistema con la fuente ATX. Se ampliará información sobre este conector en el tema decicado al estándar ATX. Placa base 39/39 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.7.- DISEÑO El diseño es un factor muy importante a la hora de valorar la calidad de una placa base: DISTRIBUCIÓN DE LOS COMPONENTES • La distribución de los componentes es un indicador del esmero y calidad de fabricación. Es típico el caso de algún componente mal colocado que impide la inserción de tarjetas largas en un zócalo ISA. DISIPACIÓN TÉRMICA Contaba alguien en Internet: “Hace varios años me llamó un amigo que dedía ‘MI ordenador se ha vuelto loco. Cuando pulso una tecla muestra caracteres extraños, y tengo que escribir un informe urgente. Voy a utilizar la máquina de escribir’. Y así lo hizo. Pasados unos dias acudí a su casa y encontré el problema: Tenía unos libros que bloqueaban la salida de aire del ventilador de la fuente de alimentación. Distribución de la potencia disipada por un equipo típico: Veamos a continuación unos ejemplos de consideraciones térmicas en el diseño de la placa base: Placa base 40/40 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Es conveniente que el aire procedente del micro vaya dirigido hacia los transistores del regulador, como puede verse en la imagen. En la mayoría de las placas, los reguladores de tensión utilizan transistores de potencia que representan una fuente adicional de calor. Es conveniente que el flujo de aire procedente del exterior no lleve ese calor hacia el procesador. En la siguiente imagen puede verse la circulación del aire en una caja ATX Mínitorre típica. La orientación del ventilador de la fuente de alimentación y la placa base se han modificado en la especificación ATX. El ventilador de la fuente introduce aire através del chasis pasando por el procesador que se encuentra al lado para recibir aire sin necesidad de un ventilador auxiliar. Placa base 41/41 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 Segundo ventilador En las imágenes podemos observar la ubicación adecuada de un segundo ventilador. Colocado en la parte trasera de la caja ayuda al ventilador de la fuente a desalojar el aire que entra por el frontal, incrementando el flujo de aire a través de la placa base. Aumenta la entrada de aire del exterior por la regilla delantera. Por ejemplo, añadir un segundo ventilador idéntico al que ya posee incrementa el nivel sonoro en un valor típico de 3 dBA CAPAS La placa base está formada por varias capas de material aislante en las que se encuentran impresas las pistas de cobre que transportan las señales. Estas pistas se conectan de forma que la señal puede pasar de una capa a otra. Alguna de estas capas suele usarse como masa del sistema intercalándose entre dos capas que transportan señal y evitando interferencias entre ambas. Es un parámetro importante, ya que en general un mayor número de capas redunda en una mayor estabilidad del sistema. Es típico fabricarlas de 4 capas, aunque a medida que aumenta la complejidad de las placas se están usando 6 capas. Por ejemplo la placa DFI CA64-SC para Pentium III especifica que está fabricada con cuatro capas. Placa base 42/42 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 INTERFERENCIAS ELECTROMAGNÉTICAS (EMI) Por ejemplo, Intel recomienda observar las siguientes reglas en el diseño de placas base para minimizar los efectos de la diafonía entre las pistas del bus de alta velocidad GTL+: • Maximizar el espacio entre pistas (procurar un mínimo de 0,01 pulgadas). • Evitar paralelismo entre señales de planos adyacentes (Las placa de circuito impreso puede estar formada por 6 capas o planos por donde discurren las pistas). • Como es un bus de muy baja tensión, separar las pistas de otros buses como por ejemplo las pistas de 5V/3’3V del PCI. • Separar las pistas de direcciones, datos y control para minimizar interferencias entre grupos. Recordar que cualquier orificio de ventilación es una entrada para interferencias electromagnéticas. Cuanto más pequeños sean menor será la longitud de onda que “permiten pasar” y por tanto mayor la frecuencia. Placa base 43/43 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.8.- CONFIGURACIÓN • La configuración de una placa madre significa la adecuación de los parámetros de funcionamiento a los componentes instalados. • Estos parámetros se determinan en el arranque y la mayoría se guardan en la CMOS RAM para quedar a disposición del sistema operativo o cualquier otro software que los necesite para funcionar. P. Ej. Adecuar la velocidad del bus del sistema al micro instalado. • Aunque cada vez menos, la configuración de las placas se realiza mediante unos conectores llamados jumpers que abren o cierran una conexión. • Cada vez mas parámetros se configuran mediante el programa setup que reside en el BIOS-ROM. • Actualmente, algunas placas como las QDI utilizan una tecnología que evita totalmente el uso de jumpers. Incluso, la propia BIOS se encarga de detectar los parámetros del micro instalado. Placa base 44/44 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.9.- EJEMPLOS PLACA BASE AMI FORTRESS 3000 (CHIPSET INTEL 440GX) 1 Mouse port 16 Battery 2 Keyboard port 17 System BIOS 3 Serial port 2 18 Channel A Ultra-wide/Ultra-2 SCSI 4 Parallel port connector (68 pin) 5 Serial port 1 19 Channel B Ultra-wide/Ultra-2 SCSI 6 USB connector connector (68 pin) 7 RJ-45 20 Channel B fast/narrow SCSI 8 LAN controller connector (50 pin) 9 AGP slot 21 FDD connector 10 PCI slots 22 EIDE connector 2 (secondary) 11 ISA slot 23 EIDE connector 1 (primary) 12 Intel 82371EB PIIX4E (PCI-ISA 24 DIMM sockets bridge) 25 Intel 443GX system controller 13 DEC 21152 (PCI-PCI bridge) 26 Power connector 14 Buzzer 27 Slot 1 CPU sockets 15 SCSI controller Placa base 45/45 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 PLACA BASE INTEL D850GB • Chipset Intel 850 para Pentium 4 • 4 zócalos para módulos RIMM de memoria RDRAM PC800 y PC600 (Entre 128 MB y 2 GB). • Soporte para USB 2.0. • Soporte Ultra ATA/100. • AGP 4X de 1’5Voltios. Placa base 46/46 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 3.10.- ATX (REVISIÓN 2.01) • Las especificaciones ATX se refieren a una serie de EXIGENCIAS y RECOMENDACIONES para la fabricación de placas base. • Los objetivos son reducir costes de fabricación y mantenimiento. • Existen dos tamaños: ATX y mini-ATX. • Involucra a otros componentes del PC, como la fuente de alimentación y la caja donde se ubican placa y fuente. PROCESADOR • Alejado de los slots de expansión para permitir el uso de tarjetas largas y acceso mas cómodo en posibles actualizaciones. • Cerca del ventilador de la fuente de alimentación para aprovechar flujo de aire. ZÓCALOS DE MEMORIA • Lejos de los buses de expansión y accesibles para facilitar actualizaciones. Placa base 47/47 Mantenimiento de Equipos Informáticos Apuntes 01/02 ver. 5.2 CONECTORES I/O • Se integra en la placa un panel de doble altura que alberga los conectores I/O más comunes. • Menos cables y mas cortos reducen costos y emisiones EMI (los cables serie y paralelo pueden comportarse como antenas). • Ejemplo de conector: FUENTE DE ALIMENTACIÓN • Nuevo conector de 20 pines. • Se añade conexión de 3,3 V en previsión de alimentar las futuras tarjetas PCI de 3,3V. (COM = común o masa del sistema). Además proporciona una tensión continua de valor más cercano al empleado por los micros actuales, lo que permite reducir el tamaño de los reguladores de tensión de la placa base. • Un único ventilador situado en la parte trasera expulsa el aire permitiendo la refrigeración del micro y de las tarjetas de expansión. Puede evitar la necesidad de ventiladores adicionales por lo que se reducen los costes de refrigeración y ruido acústico. • El cumplimiento de la versión 2.01 de la especificación requiere la inclusión de las señales PS-ON, 5VSB y PW-OK: Más información en el tema de alimentación. UNIDADES DE ALMACENAMIENTO • Conectores (IDE, FLOPPY) cerca de unidades de almacenamiento para acortar cables. CHASIS • Las dimensiones de la placa tienen la misma anchura que las Full-AT, pero no la misma longitud. • Los orificios de montaje coinciden con los de las placas Full-AT pero se han añadido alguno mas, por lo que los chasis no son idénticos. Placa base 48/48