soluciones - Facultad de Ingeniería

Anuncio

Facultad de Ingeniería – UDELAR

Int. a los microprocesadores – DICIEMBRE 2011

SOLUCIONES

pag. 1/5

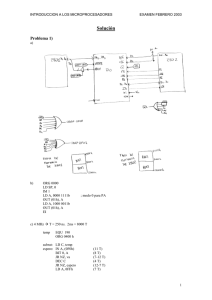

SOLUCIÓN PROBLEMA 1

a) Hardware

-- Memorias:

ROM

A[14..0]

/MREQ

Add[]

RAM

D[7..0]

Data[]

A[14..0]

/MREQ

OR2

CS

OE

A15

inst16

CS

OE

WE

/RD

inst15

/WR

inst32

-- Puertos, decodificación e Interrupciones.

Puertos salida:

inst14

• mux_ctrl[2]

• out

Puertos Entrada:

• port_in[4] = mux, ena, sel[2]

• ffint[2]

Pulsos (mapeados en espacio de salida):

• ack+

• ackVCC

MUX

data[]

PRN

D

inst13

IRQ+

DFF

mux

result

D[7..0]

Data[]

OR2

A15 NOT

/RD

IN[3..0]

Add[]

BAND2

/INT

Q

inst40

CLRN

inst36

sel[]

inst34

/ACK+

MUX_CTRL[1..0]

inst12

DFF

D

NOT

DATA_BUS

D0

TRI

VCC

PRN

Q

IRQ-

D1

TRI

inst22

inst30

CLRN

inst38

/IDSP_41H

DFF

D0

NOT

PRN

D

inst45

out

Q

ODSP_42

/ACK-

CLRN

inst6

D3

TRI

inst46

ENA

D2

TRI

D[1..0]

DFF

D

inst35

SEL[1..0]

D[1..0]

TRI

MUX_CTRL[1..0]

Q

ODSP_43

CLRN

inst20

inst37

/IDSP_40H

PRN

NOT

inst44

deco_1de4

A0

A1

Y0

Y1

Y2

Y3

A1

A0

OR2

/RD

deco_1de4

/IDSP_40h

/IDSP_41h

A0

A1

/WR

OR2

G

inst41

A[6]

NOT

inst29

inst18

A[7]

Y0

Y1

Y2

Y3

A1

A0

G

DECO

/IORQ

OR3

inst

inst42

inst21

DECO

/ACK+

/ACK/ODSP_42H

/ODSP_43H

Facultad de Ingeniería – UDELAR

Int. a los microprocesadores – DICIEMBRE 2011

SOLUCIONES

b) Rutina atención interrupciones

; isr:

;

preservar registros

;

si irq+ pendiente entonces

;

isr_subida()

;

borro ff subida

;

else

;

isr_bajada()

;

borro ff bajada

;

finsi

;

restaurar registros

;

ei, ret

;

org 38h

isr:

push af

in a, (irqs)

bit 0, a

jr z, else

call isr_subida

out (ack_subida), a

jr finsi

else:

call isr_bajada

out (ack_bajada), a

finsi:

pop af

ei

ret

pag. 2/5

manejo_mux:

push hl

push af

push bc

ld hl, sel_ena_anterior

in a, (port_in)

and mask_sel_ena

cp (hl)

jr z, fin_si_sel

;

sel_anterior = sel

ld (hl), a

mientras_out:

ld a, (var_out)

bit bit_mux, a

jr nz, mientras_out

ld b, a

ld a, 0xFF

ld (CAMBIANDO), a

; cambiando = TRUE

ld a, b

out (mux_ctrl), a

; pmux_ctrl = sel

mientras_mux:

in a, (port_in)

bit bit_mux, a

jr nz, mientras_mux

xor a

ld (CAMBIANDO), a

fin_si_sel:

pop bc

pop hl

pop af

ret

; isr_subida:

;

si (ena=1 and not cambiando) entonces d) Inicialización, definición de constantes,

out <- 1

reserva de memoria

;

; sp, modo 1

isr_subida:

; port_out, var_out

in a, (port_in)

; sel_ant=sel, ena_ant=ena

bit bit_ena, a

; mux_ctrl =sel

jr z, fin1

; esperar mux=0

ld a, (CAMBIANDO)

; inicializo_otros()

or a

; habilitar interrupciones

jr nz fin1

; jp loop principal

ld a, 1

out (port_out), a

org 0

ld (var_out), a

init:

fin1:

ld sp, 0

ret

im 1

ld a, 0

; isr_bajada:

out (port_out), a

;

out <- 0

ld (var_out), a

isr_bajada:

in a, (port_in)

ld a, 0

and mask_sel_ena

out (port_out), a

ld (sel_ena_anterior), a

ld (var_out), a

out (mux_ctrl), a

ret

espero_inicial:

in a, (port_in)

c) Subrutina manejo_mux

bit bit_mux, a

; manejo_mux(){

jr nz, espero_inicial

;

si sel != sel_ant or ena != ena_ant {

call inicializo_otros

;

sel_ant = sel

ei

;

ena_ant = ena

;

mientras (out == 1) {} // espero

loop:

;

cambiando = TRUE

call atiendo_otros

;

pmux_ctrl = sel

call manejo_mux

;

mientras (mux = 1) {} // espero

jp loop

;

cambiando = FALSE

;

}

; }

Facultad de Ingeniería – UDELAR

Int. a los microprocesadores – DICIEMBRE 2011

SOLUCIONES

; constantes

irqs

port_in

bit_mux

bit_ena

mask_sel_ena

equ

equ

equ

equ

equ

0x41

0x40

3

2

00000111B

ack_subida

ack_bajada

equ

equ

0x40

0x41

port_out

mux_ctrl

pag. 3/5

equ 0x42

equ

0x43

; Reserva de memoria

org 8000h

CAMBIANDO:

DB

sel_ena_anterior:

DB

var_out:

DB

Facultad de Ingeniería – UDELAR

Int. a los microprocesadores – DICIEMBRE 2011

SOLUCIONES

pag. 4/5

SOLUCIÓN PROBLEMA 2

a) Hardware.

Memorias

ROM-P

ROM

A[13..0]

Add[]

ROM-S

ROM

D[7..0]

Data[]

A[9..0]

OR2

Add[]

RAM

D[7..0]

Data[]

A[14..0]

Add[]

Data[]

D[7..0]

OR2

CS

OE

inst19

CS

OE

inst23

/MREQ

OR2

CS

OE

WE

/RD

A15 NOT

inst16

/WR

inst32

/MREQOR2

A15

inst17

NOT

A14

inst15

inst20

inst22

/RD

inst13

ctc

D7..D0

BIDIR

VCC

M1/

M1\ CK/TRG0

IORQ\ ZC/TO0

RD\ CK/TRG1

ZC/TO1

CS1

CK/TRG2

CS0

ZC/TO2

CE\

CK/TRG3

INPUT

VCC

INPUT

VCC

INPUT

VCC

IORQ/

RD/

A1

INPUT

VCC

INPUT

VCC

A0

CK

INPUT

VCC

INPUT

VCC

RESET

A7

A6

CK

RESET\

BOR2

INPUT

VCC

INPUT

VCC

VCC

IEI

D0..D7

IEO

INT\

a dispositiv os de MENOR prioridad

OUTPUT

R

inst5

OUTPUT

inst

/IDSP_82H

INT/

NOT

DATA_BUS

inst45

ent_muest[7..0]

TRI

inst7

CONVERSOR A/D

/IDSP_81H

VCC

D

UPDATE

/ODSP_81

PRN

data[7..0]

NOT

DFF

DFF

D

inst47

TRI

Q

/IDSP_80H

Q

D0

inst46

CLRN

inst4

PRN

CLRN

inst8

NOT

inst44

ENABLE

TRI

D2

/ODSP_80H

start_convert

inst9

ent_func[1..0]

TRI

D[1..0]

inst10

deco_1de4

A0

A1

/RD

Y0

Y1

Y2

Y3

A1

A0

OR2

deco_1de4

/IDSP_80H

/IDSP_81H

/IDSP_82H

A0

A1

/WR

OR2

G

inst41

A[7]

NOT

inst29

inst18

A[6]

Y0

Y1

Y2

Y3

A1

A0

G

DECO

/IORQ

OR3

inst1

inst42

inst21

DECO

/ODSP_80H

/ODSP_81H

Facultad de Ingeniería – UDELAR

Int. a los microprocesadores – DICIEMBRE 2011

SOLUCIONES

pag. 5/5

Aclaración hecha en el salón: cuando ena=0 lo que debe valer 0 es la salida del conversor A/D, la

señal data[] puede variar siempre y cuando no haya un flanco en start_convert. En particular en

esta solución data[] es directamente el bus de datos por lo que cambia todo el tiempo.

b) Inicialización y programa principal

org 0

init:

ld sp, 0

im 2

ld a, int_table/256

ld i, a

call inicializo_timer

call inicializo_otros

ld a, 0

out(START_CONVERT), a

out(UPDATE_CLR), a

ld (ENABLED), a

ei

main_loop:

call atiendo_otros

in a, (UPDATE)

or 00h

jr z, main_loop

;; hay update pendiente

in a, (ENT_FUNC)

ld b, a

and ENABLE_MASK

ld (ENABLED), a

in a, (ENT_MUEST)

ld (MUEST_MSEC), a

ld a, b

and FUNC_MASK

;; preparar puntero a tabla con func

ld hl, tab_cuad

add h

ld h,a

ld (TAB_FUNC_PTR), hl

;; borrar flag de update y

;; reconfigurar contador

out(UPDATE_CLR), a

call inicializo_counter

jp main_loop

inicializo_timer:

ld a, TIMER_VEC

out(CTC0), a

ld a, TIMER_CTL

out(CTC0), a

ld a, TIMER_CONST

out(CTC0), a

ret

inicializo_counter:

ld a, COUNTER_CTL

out(CTC1), a

ld a, (MUEST_MSEC)

out(CTC1), a

ret

c) Rutina interrupciones

isr_counter:

ei

push af

push hl

ld a, (ENABLED)

or 00h

jr z, dac_write

ld hl, (TAB_FUNC_PTR)

ld a, (hl)

inc l

ld (TAB_FUNC_PTR), hl

dac_write:

out(START_CONVERT), a

pop hl

pop af

reti

;; tabla interrupciones, reserva de memoria

y constantes

;; tabla ints

org 1000h

int_table:

dw isr_reservado0

dw isr_reservado1

dw isr_reservado2

dw isr_reservado3

dw

dw isr_counter

;; reserva memoria

org 8000h

ENABLED: DB

MUEST_MSEC: DB

TAB_FUNC_PTR: DW

;; constantes

; in ports

ENT_FUNC equ 80h

UPDATE

equ 81h

ENT_MUEST equ 82h

; out ports

START_CONVERT equ 80h

UPDATE_CLEAR equ 81h

; CTC

CTC0 equ C0h

CTC1 equ C1h

TIMER_CTL

equ 00110111b ;di,timer,256,tcf

TIMER_VEC

equ 08h

TIMER_CONST equ 250d

COUNTER_CTL equ 11010111b ;ei,cntr,trg,tcf

;; otros

ENABLE_MASK equ 00000100b

FUNC_MASK

equ 00000011b