diseño de un contador geiger con capacidad de autoverificación

Anuncio

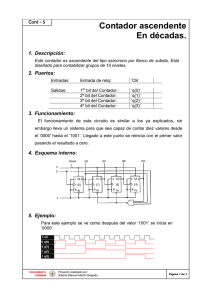

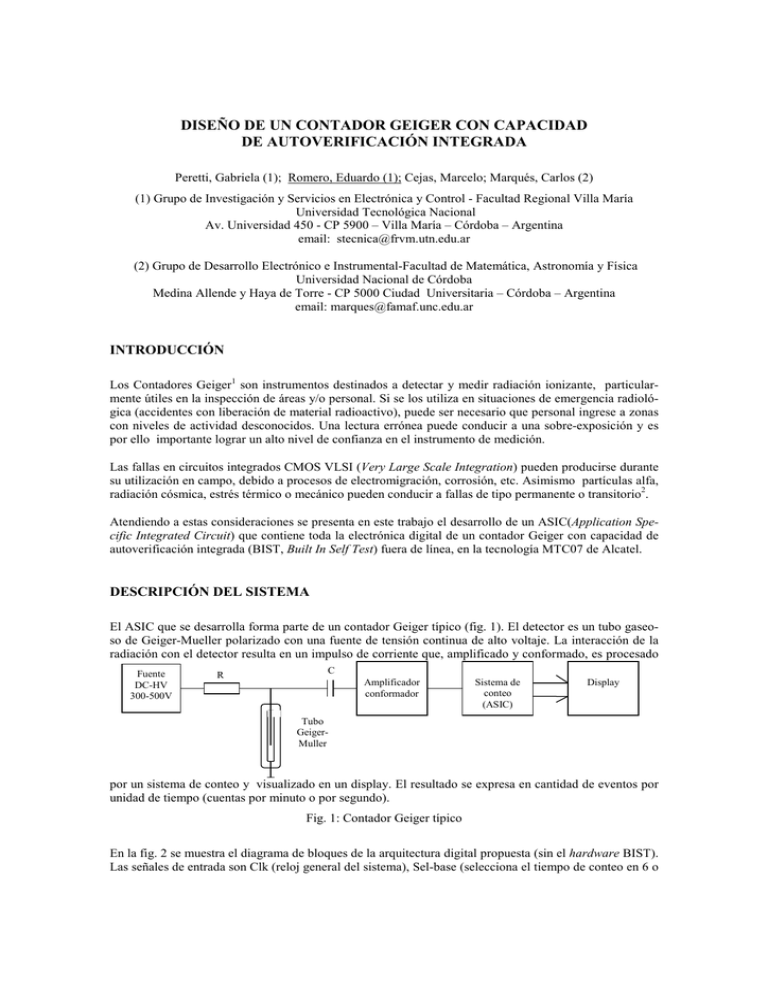

DISEÑO DE UN CONTADOR GEIGER CON CAPACIDAD DE AUTOVERIFICACIÓN INTEGRADA Peretti, Gabriela (1); Romero, Eduardo (1); Cejas, Marcelo; Marqués, Carlos (2) (1) Grupo de Investigación y Servicios en Electrónica y Control - Facultad Regional Villa María Universidad Tecnológica Nacional Av. Universidad 450 - CP 5900 – Villa María – Córdoba – Argentina email: [email protected] (2) Grupo de Desarrollo Electrónico e Instrumental-Facultad de Matemática, Astronomía y Física Universidad Nacional de Córdoba Medina Allende y Haya de Torre - CP 5000 Ciudad Universitaria – Córdoba – Argentina email: [email protected] INTRODUCCIÓN Los Contadores Geiger1 son instrumentos destinados a detectar y medir radiación ionizante, particularmente útiles en la inspección de áreas y/o personal. Si se los utiliza en situaciones de emergencia radiológica (accidentes con liberación de material radioactivo), puede ser necesario que personal ingrese a zonas con niveles de actividad desconocidos. Una lectura errónea puede conducir a una sobre-exposición y es por ello importante lograr un alto nivel de confianza en el instrumento de medición. Las fallas en circuitos integrados CMOS VLSI (Very Large Scale Integration) pueden producirse durante su utilización en campo, debido a procesos de electromigración, corrosión, etc. Asimismo partículas alfa, radiación cósmica, estrés térmico o mecánico pueden conducir a fallas de tipo permanente o transitorio2. Atendiendo a estas consideraciones se presenta en este trabajo el desarrollo de un ASIC(Application Specific Integrated Circuit) que contiene toda la electrónica digital de un contador Geiger con capacidad de autoverificación integrada (BIST, Built In Self Test) fuera de línea, en la tecnología MTC07 de Alcatel. DESCRIPCIÓN DEL SISTEMA El ASIC que se desarrolla forma parte de un contador Geiger típico (fig. 1). El detector es un tubo gaseoso de Geiger-Mueller polarizado con una fuente de tensión continua de alto voltaje. La interacción de la radiación con el detector resulta en un impulso de corriente que, amplificado y conformado, es procesado Fuente DC-HV 300-500V R C Amplificador conformador Sistema de conteo (ASIC) Display Tubo GeigerMuller por un sistema de conteo y visualizado en un display. El resultado se expresa en cantidad de eventos por unidad de tiempo (cuentas por minuto o por segundo). Fig. 1: Contador Geiger típico En la fig. 2 se muestra el diagrama de bloques de la arquitectura digital propuesta (sin el hardware BIST). Las señales de entrada son Clk (reloj general del sistema), Sel-base (selecciona el tiempo de conteo en 6 o Clk Base de tiempo (BT) X10 Sel-Base Decodificador de Estados (DE) Ventana Escribe registro Reset Al display 4 Señal a medir 4 7 3 Contador de Pulsos (CP) 4 Registros 4 4 4 Conversor 7 Seg. (CS) 7 7 Overflow 3 Detector Cuenta Máxima 60 segundos) y señal a medir (del amplificador-conformador). Las salidas del circuito son las necesarias para el manejo del display. Fig. 2: Diagrama de bloques del circuito sin BIST El bloque Base de Tiempo (BT) efectúa una división de frecuencia y junto con el Decodificador de Estados (DE) generan las señales Ventana, que establece el tiempo de medición y Reset, que reinicia el Contador de Pulsos (CP). El CP efectúa la cuenta en BCD (Binary Coded Decimal) de los pulsos de Señal a Medir. El resultado de la cuenta se registra en el Bloque Registros y se convierte a codificación 7 segmentos mediante el bloque Conversor 7 Segmentos (CS). El Bloque Detector de Cuenta Máxima (un registro) genera una señal de alarma (Overflow) si se supera la capacidad de cuenta del contador de pulsos. ESTRATEGIA DE AUTOVERIFICACIÓN Se adopta una estrategia de verificación fuera de línea en la cual el circuito debe sacarse de su operación normal para ser verificado. Se ha seguido un enfoque funcional sin modelo de falla3. Para la verificación de los bloques secuenciales (BT y CP), se explotan las funcionalidades intrínsecas de los bloques y no se utiliza generador de patrones de test. Durante la verificación los bloques se conectan a un MISR (Multiple Input Signature Register) mediante un sistema de bus triestado (fig.3). Un LFSR (Linear Feedback Shift Register) sirve como generador de patrones de test para el Decodificador de Estados y el Conversor 7 Seg. Se verifican en forma secuencial Base de tiempo, Contador de Pulsos, Decodificador de Estados y por último Conversor 7 Seg. Esto permite utilizar un único MISR y un LFSR conduciendo a un sistema de baja sobreasignación de recursos. Los resultados del test compactados por el MISR son comparados con las firmas de los circuitos mediante un comparador. La señal Pasa/Falla indica si el circuito integrado funciona de acuerdo a lo esperado. LFSR Base de tiempo (BT) Buffer triestado Contador de Pulsos (CP) Decodificador de Estados (DE) Buffer triestado Conversor a 7 Seg. (CS) Buffer triestado Buffer triestado Bus MISR Comparador Pasa/Falla Firma 1 Firma 2 Firma 3 Firma 4 Selección firma La fig. 4 muestra la estrategia utilizada para verificar la base de tiempo (CON1 a CON5 y MOD6) y el contador de pulsos (BCD1 a BCD3). Fig. 3: Conexión de los bloques del ASIC en la fase de test. Dichos bloques se componen de contadores sincrónicos conectados en cascada de módulo diez, a excepción de MOD6 (módulo 6). Las entradas y salidas de cada contador , su tabla de estados y diagrama esquemático se muestran en las figuras 5, 6, 7 y 8. Las entradas IC y EP (fig. 5 y 6) permiten la correcta operación en cascada, evitando estados no permitidos. La estrategia consiste en particionar BT y CP en sus bloques contadores y efectuar la verificación funcional de los mismos en sucesivas sesiones de test. Para ello se incluyen multiplexores para deshabilitar la conexión en cascada de los bloques y permitir la manipulación de las líneas de entrada de los mismos. La verificación se efectúa ejercitando una operación de conteo completa partiendo del estado cero. Posteriormente se verifica la permanencia del contador en uno de sus estados bajo la condición de inhabilitación de cuenta. La respuesta del contador bajo test se compacta en el MISR. Se asume que una falla en el circuito provoca la alteración de la secuencia del contador y consecuentemente de la firma, que se detecta por comparación con la del circuito sin fallas obtenida por simulación. N/T Sistema de multiplexores modo test/ modo normal IC EP SP IC EP SP IC EP SP IC EP SP IC EP SP IC EP SP IC EP SP IC EP SP IC EP SP CON1 CON2 CON3 CON4 CON5 BCD1 BCD2 BCD3 MOD6 Buff 3est. Buff 3est. Buff 3est. Bufr 3est. Buff 3est. Buff 3est. Buff 3est. Buff 3est. Buff 3est. bus MISR Comparador Pasa/Falla Firma 1 Firma 2 Selección firma Para la verificación de los bloques DE y CS se propone un test funcional exhaustivo. Para tal fin se emplea un LFSR de longitud máxima4 que se utiliza para generar los patrones de test. El LFSR, de 13 bits, se obtiene de la reconfiguración de los registros del sistema básico mediante el uso de multiplexores y compuertas XOR. IC EP Contador Módulo Diez Q0-Q3 4 RESET CLK SP Fig. 4: Verificación de la Base de Tiempo y del Contador de Pulsos IC EP Q0-Q2 Contador Módulo Seis 3 RESET EP/ IC 00 01 10 Estado actual 0 0/0 0/0 0/0 1 1/0 1/0 1/0 2 2/0 2/0 2/0 3 3/0 3/0 3/0 4 4/0 4/0 4/0 5 5/0 5/0 5/0 6 6/0 6/0 6/0 7 7/0 7/0 7/0 8 8/0 8/0 8/0 9 9/0 9/0 9/0 Estado siguiente / salida actual SP CLK EP/ IC 00 01 10 11 Estado actual 0 0/0 0/0 0/0 1/0 1 1/0 1/0 1/0 2/0 2 2/0 2/0 2/0 3/0 3 3/0 3/0 3/0 4/0 4 4/0 4/0 4/0 5/0 5 5/0 5/0 5/0 0/1 Estado siguiente / salida actual Fig. 5: Diagrama de E/S y tabla de estados del Contador Módulo Diez Fig. 6: Diagrama de E/S y tabla de estados del Contador Módulo Seis Fig. 7:.Diagrama esquemático del Contador Módulo Diez U17 6 U17 7 1 IC 3 EP 1 U17 8 1 2 2 U17 9 3 3 U18 2 INV 3 AND 2 U19 4 2 U19 0 1 3 1 3 1 3 D Q CLK Q R 4 5 U18 4 Q3 AND 2 Q3 3 1 2 2 U19 1 3 DFFR OR2 2 D Q CLK Q R U18 6 4 5 31 QZ2 AND 2 2 2 U19 2 3 AND 2 3 DFFR 1 D Q CLK Q 5 Q1 3 1 Q1 AND 2 QZ1 1 3 DFFR 2 2 AND 2 AND 2 AND 2 AND 2 AND 4 U19 8 1 Q3 2 QZ0 U19 9 3 1 Q2 3 2 QZ1 U20 0 SP U20 1 AND 2 AND 2 1 QZ0 3 2 Q1 1 2 3 QZ3 QZ1 Q0 1 3 U20 2 2 U20 3 OR2 4 1 2 3 Q0 Q2 Q1 U20 4 4 1 2 3 U20 5 AND 2 1 3 1 QZ0 2 3 2 Q2 OR2 AND 3 OR3 U20 6 AND 2 U20 7 4 4 AND 3 1 QZ2 2Q1 3Q0 AND 3 RESE T CLK U 1 7 6 U 1 7 7 U 1 7 8 1 U 1 7 9 U 1 8 1 3 2 2 1 U 1 8 2 1 U 1 8 3 3 1 3 2 3 AND2 1 2 Q 2 5 AND2 O R 2 U 1 8 8 1 3 1 2 2 DFFR U 1 8 9 1 Q Z 2 CLK Q 3 1 2 2 U 1 8 5 Q 2 U 1 9 0 U 1 8 4 4 D R I N V 3 4 D Q CLK Q Q 1 3 1 AND2 5 1 O R 2 3 2 1 DFFR 2 2 Q Z 1 U 1 9 1 3 AND2 U 1 9 3 O R 2 3 4 D Q CLK Q R 1 AND2U 1 9 4 R 3 2 2 4 Q 0 5 Q Z 0 3 1 U 1 9 6 1 Q 0 1 Q Z2 1 2 3 3 I C EP DFFR 2 AND3 AND2 AND2 AND2 U 1 2 7 3 2 1 4 U 1 2 9 2 1 3 AND3 U 1 3 1 SP 2 O R 2 3 1 U 1 2 8 Q Z 0 AND2 2 Q 1 3 1 Q 0 U 1 3 0 2 3 UN A 1D 3 2 1 3 2 Q 2 1 Q Z 0 O R 2 2 2 U19 3 5 QZ2 3 Q3 4 U18 9 1 4 R OR2 3 2 U18 8 U18 7 1 Q2 1 2 3 2 U18 5 1 QZ3 OR2 2 U19 5 Q0 1 QZ1 2 1 2 U18 1 1 2 U18 3 1 AND 2 U18 0 1 2 AND2 RESET CLK Fig. 8: Diagrama esquemático del Contador Módulo Seis OR2 3 D Q CLK Q 4 5 QZ0 R 3 DFFR Q0 11 1/0 2/0 3/0 4/0 5/0 6/0 7/0 8/0 9/0 0/1 RESULTADOS El circuito se implementa con la librería de celdas estándar de la tecnología MTC07 de 0,7 µm de Alcatel5. Los resultados se obtienen mediante simulación Spice, con los tiempos propios de dicha tecnología. Para evaluar la efectividad de la estrategia planteada6, se adopta un modelo de falla estructural tipo stuckat7, lo cual permite la inyección de fallas y su posterior simulación. Si bien el enfoque de BIST funcional descrito en la literatura propone ejercitar todas las funciones del circuito bajo test, nuestros resultados muestran que para el caso de las cadenas de conteo bajo estudio, sólo son necesarias las secuencias mencionadas en el trabajo para obtener una buena cobertura de fallas de tipo estructural. Para los circuitos secuenciales los resultados de simulación permiten determinar una cobertura de fallas del 98 %. El tiempo de test requerido para verificar cada bloque contador es de 48 microsegundos a la frecuencia de test de 1MHz. Para los circuitos combinacionales la cobertura de fallas stuck es del 100%, con un tiempo de test de 8.2mseg. CONCLUSIONES Se presenta en este trabajo el diseño y simulación de un ASIC que contiene toda la electrónica digital de un contador Geiger, con capacidad de autoverificación integrada, destinada a facilitar la verificación en campo. El hardware necesario para la verificación es mínimo y sencillo en su implementación, obteniéndose una cobertura de fallas y tiempos de test razonables para la aplicación en cuestión. REFERENCIAS 1 H. H. Chiang, Electronics for Nuclear Instrumentation. Theory and Application. R. Krieger Publishing. 1985. 2 J. Abraham, W. Fuchs. “Fault and Error Models for VLSI”, IEEE Proc. Special Issue on Fault Tolerance in VLSI (Mayo 1986). 3 M. Abramovici, M. Breuer, A. Friedman. Digital Systems Testing and Testable Design. IEEE Press, 1990. 4 M. Bushnell, V. Agrawal. Essentials of Electronic Testing. Kluwer Academic Publishers, 2000. 5 Alcatel NV, Standar Cell Design Data Book 0,7µm CMOS. Alcatel, 1999. 6 I. Pomeranz, S. M. Reddy, “On achieving complete fault coverage for sequential machines”, IEEE Trans. Comput. (Marzo 1994). 7 P. Lala. Digital Circuit testing and Testability. Academic Press, 1997.