TECNOLOGiIA DE LOS COMPUTADORES

Anuncio

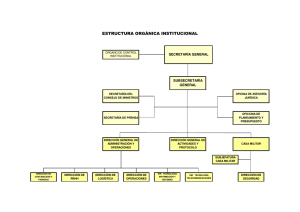

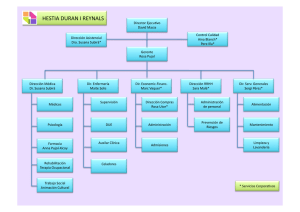

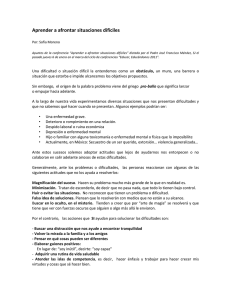

TECNOLOGIA DE LOS COMPUTADORES Examen convocatoria Junio 2003. Departamento de Arquitectura de Computadores APELLIDOS: NOMBRE: Fecha: 30 de Junio de 2003 I. Informatica I.T.I. Gestion I.T.I. Sistemas DNI: Grupo: A B C D 1.- En la gura 1 se muestra las unidades de datos y control de una maquina de proposito especco que permite calcular el maximo comun divisor (m.c.d.) de dos valores A y B. Se pide: (a) Dise~nar una unidad de control microprogramada para la unidad de datos propuesta. Emplea para ello el espacio se~nalado en la gura 1. Se han de especicar claramente el tama~no de los buses, registros, memorias y otros elementos que se utilicen. (b) Completar el dise~no de la unidad de control con el contenido de la memoria de microprograma, indicandolo en la tabla 1. Puedes incorporar a la microinstruccion los puntos de control que consideres necesario, indicando claramente su cometido. Comenta usando notacion RTL que hace cada microinstruccion. El funcionamiento deseado para la maquina es el que se muestra en el diagrama de estados en la gura adjunta. A efectos de implementacion se podra considerar, si fuera necesario, que un estado puede corresponder a varios ciclos de reloj. init Inicio init A <- BUS_A B <- BUS_B S Z Z <- /RESTA(A;B) S <- RESTA(A;B)[7] S B<-RESTA(B;A) Z Z A<-RESTA(A;B) Fin = 1 Comentario en RTL Dir. c1 c2 c3 c4 c5 c6 c7 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 16 17 18 19 20 Tabla 1: Memoria de microprograma (problema 1) 1 8 8 BUS_A BUS_B Unidad de Control 0 1 0 c5 1 c6 8 8 A Load c1 B Load 8 c2 8 0 1 0 c3 1 8 c4 8 c7 X Z S Y 2 RESTA(X;Y) 8 c1 init Figura 1: Unidades de datos y control del problema 1. fin c2 c3 c4 c5 c6 c7 2.- En la siguiente tabla se recoge el formato de algunas de las instrucciones de una maquina hipotetica: Formato de la instruccion #Pal CO Reg1 Reg2 X OPER 2a Pal. 1 000 rd dir XXX 1 001 rd rf XXX oper XXX 1 010 rd dir XXX (C 2) 1 011 rd rf desp XXX 1 100 XXX desp (C 2) XXX 2 101 rd rf XXX oper cte (C 2) (XXX - no usado) ( Los campos marcados con (C 2) corresponden a enteros en convenio complemento a 2) Mnemonico LD rd, (dir) OPER rd, rf ST rd, (dir) LD rd, desp(rf) JMP desp OPER rd, rf, cte Instruccion Signicado rd M (dir ) rd oper (rf ; rd ) M (dir ) rd rd M (rf + desp ) PC PC + 1 + desp rd oper (rf ; cte ) Observese que las instrucciones pueden ocupar una o dos palabras (de 16 bits cada una) en memoria principal. La primera palabra contiene varios campos dependiendo de la instruccion concreta, tal y como se muestra en la tabla anterior. Estos campos son el codigo de operacion (CO) con los 3 bits m as signicativos, dos campos de registro (Reg1 y Reg2), de 3 bits cada uno, un campo de direccion (dir) de 10 bits, un campo de desplazamiento (desp) de 7 bits que es un entero representado en el convenio del complemento a dos (C2), y un campo con la operacion aritmetica a realizar (oper) de 2 bits. Las operaciones aritmeticas posibles son AND/OR/ADD/SUB y se codican mediante 00/01/10/11 respectivamente. La segunda palabra, de ser necesaria, almacena el valor de una constante entera de 16 bits representada usando el convenio del complemento a dos (C2). El ciclo de instruccion, para las instrucciones propuestas, se muestra en la siguiente gura: s1 IR <- M(PC) s2 Decodificación PC <- PC + 1 LD rd, (dir) rd <- M(dir) s3 OPER rd, rf s3 s4 RA <- rf ST rd, (dir) s3 M(dir) <- rd LD rd, desp(rf) s3 RA <- rf JMP desp s3 OPER rd, rf, cte PC <- PC + desp s3 RC <- M(PC) RA <- rf RB <- rd rd <- op(RA, RB) s4 s5 TMP <- RA + desp rd <- M(TMP) s4 s5 PC <- PC + 1 rd <- op(RA, RC) (a) Construye un datapath basado en las unidades funcionales que aparecen en la gura adjunta, y que son: Memoria principal de 1024 16 bits. Se direcciona a traves de la entrada Direccion. Los datos en lectura se reciben a traves de DatoOut y la escritura de datos se realiza por DatoIn. Banco de 8 registros de 16 bits. Se pueden direccionar dos registros para lectura mediante las entradas DA y DB, obteniendose los datos por las salidas A y B, respectivamente. Simultaneamente se puede escribir el registro direccionado en DIn (que coincide con DB), con el valor presente en la entrada In. ALU. Permite realizar las siguientes operaciones: AND, OR, SUMA y RESTA de los valores presentes en sus entradas, en funcion del valor de las se~nales de control c10,c11 (00,01,10,11, respectivamente). Registros: IR, RA, RB, RC, todos de 16 bits. Banco de 2 registros, PC y TMP, de 10 bits cada uno. 10 c3 Load sel TMP 0 PC 1 c4 16 RA c5 3 3 10 DA W DB/DIn A load c7 16 16 16 Banco de Registros 16 In B 16 ALU 16 RB load 16 c8 16 16 IR load 16 oper 2 c10,c11 c6 16 10 c1 c2 W/R CS 16 Memoria Principal Dirección DatoOut 16 DatoIn RC load c9 16 16 En el dise~no se puede incluir la circuitera combinacional (puertas logicas, multiplexores, etc.), constantes, buses y elementos para ajustar el tama~no de los buses que creas necesarios. Debes especicar claramente, la funcion de los puntos de control y el tama~no de los buses, que hayas a~nadido. Se podra usar etiquetas como en OrCAD. Nota: (b) Rellena el siguiente cronograma suponiendo que inicialmente PC = 100H y que el contenido de la memoria es Mem[i] = i, para cada direccion de memoria i (i 0), excepto para la posiciones de la siguiente tabla que contienen el programa que se ejecuta (todos los valores estan expresados en hexadecimal, como indica el sujo H). Asimismo completa dicha tabla indicando en ensamblador, siempre que sea posible, la instruccion y operandos a los que corresponde el codigo maquina mostrado. Dir. 100H 101H 102H 103H 104H 105H 106H 107H Contenido 0505H 68F6H A902H 0200H 8002H 0016H 4601H 4A02H Codigo ensamblador CLOCK PC 100H DatoOut DatoIn IR RA RB RC TMP >Se ha(n) modicado alguna(s) posicion(es) de la memoria? En caso armativo, >cual(es) y que valor se ha almacenado? Direccion Nuevo Contenido